Техническое руководство пользователя.

PHILIPS

P89LPC932

80С51 8-ми битный микроконтроллер

Cодержание

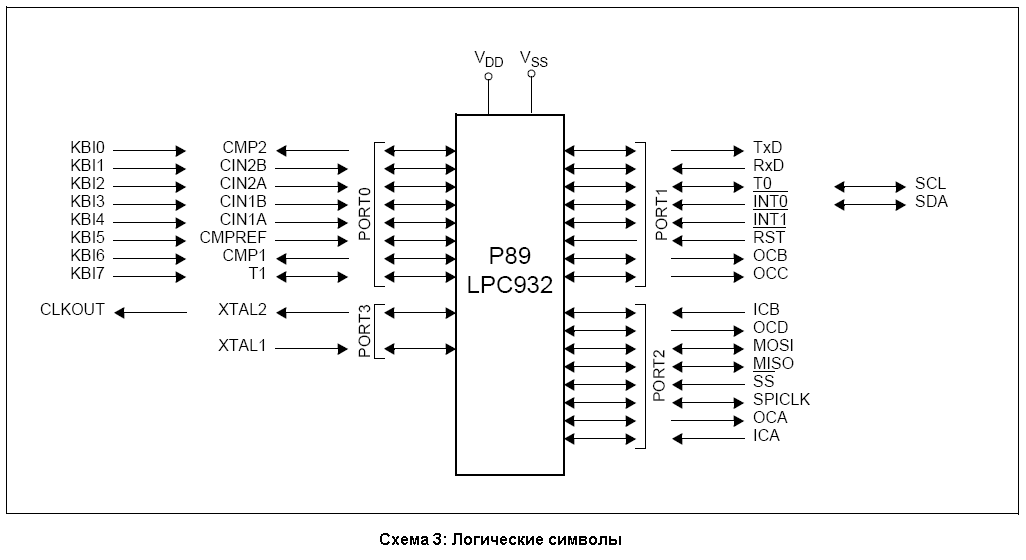

Общее описание

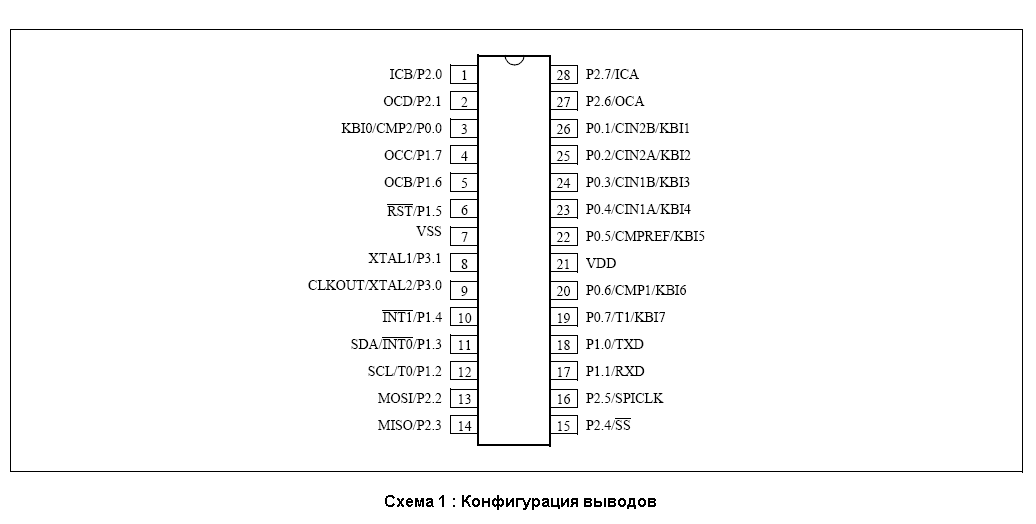

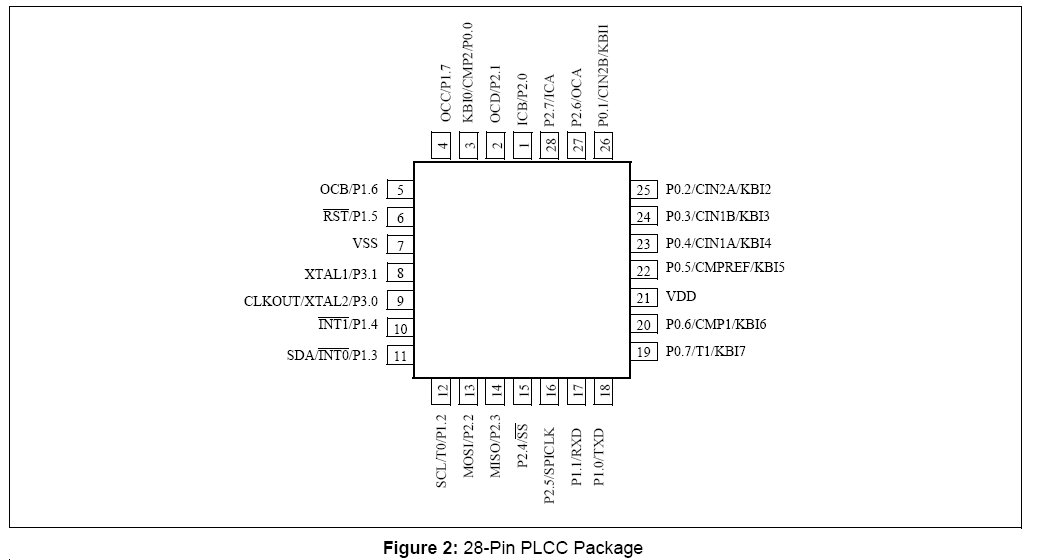

Конфигурация выводов

Описание выводов

Регистры специальных функций

Функциональное описание

Улучшенный CPU

Общее описание.

LPC932 – одночиповый микроконтроллер, разра-ботанный для приложений, требующих высоко-интегрированные низкостоимостные решения в широ-ком диапазоне требований к производительности.LPC932 базируется на высокопроизводительной процессорной архитектуре которая выполняет инструкции (операции) за два-четыре такта, в шесть раз быстрее стандартного 80С51 устройства. Множество функий системного уровня были включены вLPC932 для уменьшения количества компонент, пространства, и стоимости системы.

Описание выводов:

|

Мнемоника |

Номер вывода |

Тип |

Имя и функция |

|

P0.0 – P0.7 |

3, 26, 25, 24, 23, 22, 20, 19 |

I/O |

Порт 0: порт 0 – 8-ми битный порт I/O c программируемым пользователем типом выхода. В течение сброса защелки порта 0 сконфигурированы в режиме входа с отключенным внутренним насыщением. Назначение входов и выходов порта 0 зависит от выбранной конфигурации порта. Каждый вывод порта конфигурируется независимо. Обратитесь к секции конфигурации ввода-вывода (I/O configuration) и электрическим характеристикам постоянного тока (DC Electrical characteristics) для дальнейшей информации.

Прерывание клавиатуры работает с выводами порта 0.

Все выводы имеют входы на триггерах Шмидта.

Порт 0 также обеспечивает некоторые специфические функции, которые описаны ниже. |

|

3 |

I/0 I O |

P0.0 – порт 0, бит 0 CMP2 – компаратор 2 выход KBI0 – клавиатура, вход 0 | |

|

26 |

I/O I O |

P0.1 – порт 0, бит 1 CIN2B – компаратор 2, “+” вход B KBI1 – клавиатура, вход 1 | |

|

25 |

I/O I 0 |

P0.2 – порт 0, бит 2 CIN2B – компаратор 2, “+” вход A KBI2– клавиатура, вход 2 | |

|

24 |

I/O I 0 |

P0.3 – порт 0, бит 3 CIN2B – компаратор 1, “+” вход B KBI3 – клавиатура, вход 3 | |

|

23 |

I/O I 0 |

P0.4 – порт 0, бит 4 CIN1B – компаратор 1, “+” вход B KBI3 – клавиатура, вход 4 | |

|

22 |

I/O I 0 |

P0.5–порт 0, бит 5CIN1A–компаратор 1, “+” вход AKBI3–клавиатура, вход 5 | |

|

20 |

I/O I 0 |

P0.6 – порт 0, бит 6CMPREF – сравнит. вывод (отрицат.) KBI6 - клавиатура, вход 5 | |

|

|

19 |

I/O I 0 |

P0.7 – порт 0, бит 7 CIN1B – компаратор 1, “+” вход A KBI3 – клавиатура, вход 5 |

|

P1.0 - P1.7 |

18,17, 12, 11, 10, 6, 5, 4 |

I/O (для P1.0 – P1.4, P1.6-P1.7)I (для P1.5) |

Порт 1 порт 1– 8-ми битный порт I/O c программируемым пользователем типом выхода, кроме трех выводов, описанных выше. В течение сброса защелки порта 0 сконфигурированы в режиме входа с отключенным внутренним насыщением. Назначение входов и выходов порта 0 зависит от выбранной конфигурации порта. Каждый вывод (из конфигурируемых) порта программируется отдельно. Обратитесь к секции конфигурации ввода-вывода (I/O configuration) и электрическим характерис-тикам постоянного тока (DC Electrical characteristics) для дальнейшей информации. Выводы P1.2 – P1.3 – в режиме открытоко стока (когда выходы). P1.5 – только вход.

Все выводы имеют входы на триггерах Шмидта.

Порт 1 также обеспечивает некоторые специфические функции, которые описаны ниже. |

|

|

18 |

I/O |

P1.0 – порт 1, бит 0 |

|

|

17 |

O I/O I |

TxD – выход передатчика для посл. Порта P1.1 – порт 1, бит 1 RxD – вход приемника для послед. порта |

|

|

12 |

I/O I/O I/O |

P1.2 – порт 1, бит 2 Таймер/счетчик 0 входа внешнего счета или выход по переполнению. (Открытый сток, если исп. как выход) I2C последоват. Генератор вх/вых |

|

|

11 |

I I I/O |

P1.3 – порт 1, бит 3 INT0 – внешнее прерывание 0 входа I2C последоват. Генератор вх/вых |

|

|

10 |

I I |

P1.4 – порт 1, бит 4 INT0 – внешнее прерывание 0 входа |

|

|

6 |

I I |

P1.5 – порт 1, бит 5 (только вход) RST – вход внешнего сброса при включении питания или, если выбрано, через UCFG1. Когда функционирует как вход сброса низкий сигнал на входе сбрасывает микроконтроллер, переводя I/O выводы и периферию в состояние по умолчанию и процессор начинает выполнять микропрограмму с 0 адреса. Также используется в течение процесса начальной загрузки для перехода в состояние внутреннего программирования. |

|

|

5 |

I/O O |

P1.6 – порт 1, бит 6 OCB – выход Compare B |

|

|

4 |

I/O O |

P1.7 – порт 1, бит 7 OCB – выход Compare B |

|

P2.0 – P2.7 |

1,2,13,14, 15, 16, 27, 28 |

I/O |

Порт 1 порт 1– 8-ми битный порт I/O c программируемым пользователем типом выхода, кроме трех выводов, описанных выше. В течение сброса защелки порта 0 сконфигурированы в режиме входа с отключенным внутренним насыщением. Назначение входов и выходов порта 0 зависит от выбранной конфигурации порта. Каждый вывод (из конфигурируемых) порта программируется отдельно. Обратитесь к секции конфигурации ввода-вывода (I/O configuration) и электрическим характерис-тикам постоянного тока (DC Electrical characteristics) для дальнейшей информации. Выводы P1.2 – P1.3 – в режиме открытоко стока (когда выходы). P1.5 – только вход.

Все выводы имеют входы на триггерах Шмидта.

Порт 2 также обеспечивает некоторые специфические функции, которые описаны ниже. |

|

|

1 |

I/O I |

P2.0 – порт 2, бит 0 ICB – вход захвата B |

|

|

2 |

I/O I |

P2.1 – порт 2, бит 1 ICD – вход захвата D |

|

|

13 |

I/O I/O |

P2.2 – порт 2, бит 2 MOSI – SPI master output, slave in. Когда сконфигурирован как мастер, вывод используется как выход, как slave – вход. |

|

|

14 |

I/O I/O |

P2.3 – порт 2, бит 3 MISO – master in, slave out. Когда сконфигурирован как мастер, вывод используется как вход, как slave – выход. |

|

|

15 |

I/O I |

P2.4 – порт 2, бит 4 SS – SPI slave select |

|

|

16 |

I/O I/O |

P2.4 – порт 2, бит 4 SPICLK – SPI slave select |

|

|

|

|

|

Регистры специальных функций.

Note: Регистры специальных функций (Special Function Registers, SFR). Доступ запрещен в следующих случаях:

Пользователь НЕ ДОЛЖЕН обращаться к любым не указанным ячейкам SFR.

Доступ к любым ячейкам SFRдолжен быть только к функциямSFR.

SFRбиты отмечаются “-“ , “0”, “1” – могут быть прочитаны и записаны только в следующей нотации:

“-“ – до тех пока не указано обратное, ДОЛЖЕН быть записан 0, но может вернуть любое значение при чтении (даже если был записан 0). Это зарезервированный бит и может быть использован в будущем.

“0” – ДОЛЖЕН быть записан “0”, и возвращает “0” при чтении.

“1” – ДОЛЖЕН быть записан “1”, и возвращает “1” при чтении.

Таблица.

Примечание:

* - SFRы адресуются побитно.

# - SFRы модифицируются или добавляются кSFR80С51.

$ - BRGR1 иBRGR0 – должны быть записаны

Функциональное описание.

Улучшенное CPU

LPC932 использует улучшенное 80C51CPUкоторое работает в 6 раз быстрее стандартных устройств 80C51. Машинный цикл состоит из из двух тактовCPU, и большинство операций выполняется за один или два машинных такта.

Тактовые импульсы

Определения

LPC932 имеет несколько внутренних тактовых генераторов, как описано ниже:

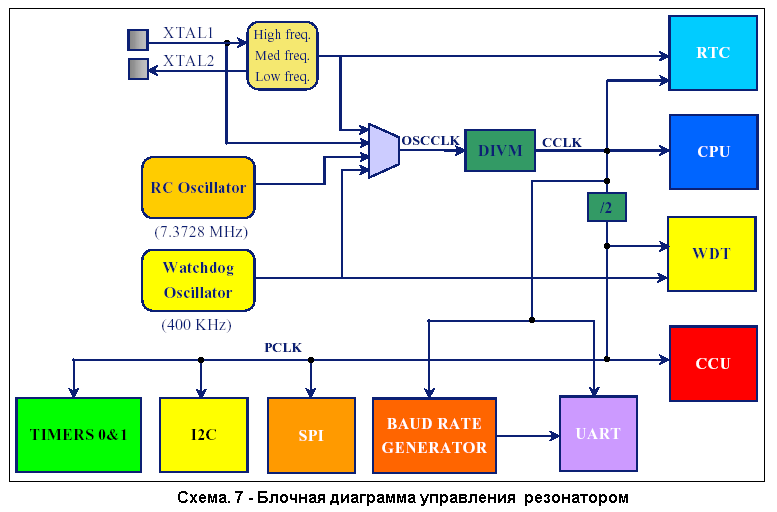

OSСCLK– вход вDIVMделитель частоты.OSCCLKвыбирается как один из четырех источников тактового сигнала (см рис.7) и также может быть поделен на более низкие частоты. (см секцию“CPU Clock (CCLK) modification : DIVM register).

Примечание: Fosc – определено как частотаOSCCLK.

CCLK– тактовый генераторCPU, выход делителя частотыDIVM. Определено два циклаCCLKв составе одного машинного цикла, и большинство операций выполняется за один или два машинных цикла (два или четыреCCLK).

RCCLK– внутренний выход тактовогоRCгенератора, 7,373Mhz.

PCLK– тактовый генератор для периферийных устройств,CCLK/2.

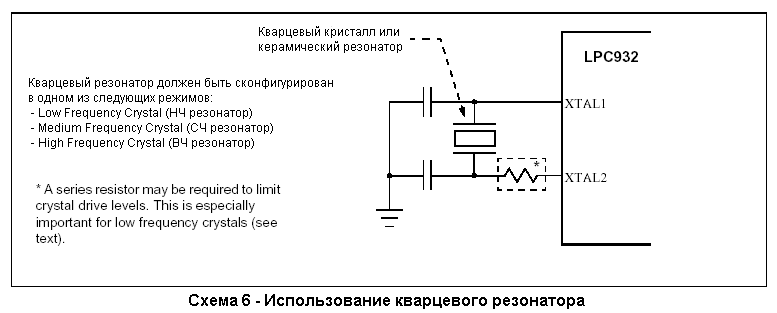

Тактовый генератор (OSCCLK)

LPC932 обеспечивает пользовательскую установку некоторых настроек тактового генератора собственно для генерации тактирующего сигналаCPU. Это позволяет провести оптимизацию под определенный круг потребностей – от высокой точности до наиболее низкой стоимости. Эти опции устанавливаются при программированииFLASHи включают встроенный в кристалл сторожевой таймер генератора тактовых импульсов, встроенный в кристаллRCгенератор, осциллятор, использующий внешний кристалл, или внешний источник тактовых сигналов. Кристалльный осциллятор может быть оптимизирован для низких, средних и высокочастотных кристаллов в диапазоне от 20kHzдо 12MHz.

Низкая скорость резонатора

Эта опция поддерживает внешний кристалл в диапазоне 20 kHz- 100kHz. Керамические резонаторы также поддерживаются в данной конфигурации.

Средняя скорость резонатора

Эта опция поддерживает внешний кристалл в диапазоне 100 kHz- 4MHz. Керамические резонаторы также поддерживаются в данной конфигурации.

Высокая скорость резонатора.

Эта опция поддерживает внешний кристалл в диапазоне 4-12 MHz. Керамические резонаторы также поддерживаются в данной конфигурации.

Выход тактового резонатора.

LPC932 поддерживает

Опция интегрированного RC-резонатора

LPC932 имеет 6-ти битныйTRIMрегистр, который может быть использован для настройки частотыRC-резонатора. В ходе сброса, значение регистраTRIMинициализируется заводскими установками на уровне 7.373MHz+/- 2.5 %. Конечное приложение пользователя может записать вTRIMрегистр для установки интегрированногоRC-резонатора на другие частоты.

Примечание:

Опция резонатора сторожевого таймера.

Сторожевой таймер имеет отдельный резонатор с частотой 400 kHz. Резонатор может быть использован для энергосбережения, когда не требуется высокая тактовая частота.

Опция входа внешнего генератора тактовых импульсов.

В этой конфигурации тактовая частота процессора отводится от внешнего источника с выхода XTAL1/P3.1 . Частота может быть от 0Hzдо 12MHz. ВыводXTAL2/P3.0 может быть использован как стандартный вывод порта или выход тактового генератора.

Задержка

LPC932 имеет внутренний таймер пробуждения, который задерживает тактовый генератор до тех пор пока тот не стабилизируется в зависимости от источника тактовых сигналов. Если источник тактовых сигналов один из трех кварцевых (низкие, средние и высокие частоты), то задержка около 992OSCCLKциклов. Если источник тактовых импульсов – внутреннийRC-резонатор, резонатор сторожевого таймера или внешний источник- задержка составит 224OSCCLKциклов.

СPU Clock (CCLK modification) : DIVM register

Частота OSCCLKможет быть поделена на целое число раз вплоть до 256 раз меньше путем конфигурирования делящего регистра (DIVM), для обеспеченияCCLK. Это продуцирует частотуCCLKпо следующей формуле:

CCLK=fosc / (N+1), гдеfosc – частота OSCCLK,N– значениеDIVM

Так как DIVMпростирается в диапазоне от 0 до 255, тоCCLKможет простираться в диапазоне –foscдоfosc/256.

Эта особенность делает возможным для временной работы CPUна более низких частотах, снижая энергопотребление. Деля частоту,CPUможет приобретать способность отвечать на другие события, кроме тех, которые вызывают прерывания (события, которые позволяют выйти из режима бездействия (Idle)) путем исполнения программы более медленно. Часто это может привести к еще меньшему энергопотреблению, чем в режиме бездействия (Idle). Это может позволить пренебрегать временем запуска резонатора в случаях когда режим выключенного питания не может быть использовано. Значение регистраDIVMможет быть изменено программой в любое время не прерывая исполнения кода.

Выбор низкого питания.

LPC932 разработан для работы на частоте 12MHz(CCLK) в пределе. Однако, еслиCCLKменее 8MHzили меньше, тогдаCLKLPSFRбит (AUXR1.7) может быть установлен в ‘1’ для поддержания дальнейшего низкого энергопотребления. При любом сбросеCLKLPустанавливается в ‘0’ для наивысшей производительности. Этот бит затем может быть установлен программно, еслиCCLK- 8MHzили менее.

Организация памяти.

Схема памяти LPC932 приведена в схеме 8.

LPC932 имеет различные области памяти:

DATA- 128 байт внутреннего пространства данных (07h…7Fh), обращение путем прямой и непрямой адресации, используя команды другие чемMOVXиMOVC. Весь стек или его часть могут находиться в данной области.

IDATA– непрямые данные. 256 байт внутреннего пространства данных (00h..FFh), обращение через непрямую адресацию, используя команды другие чемMOVXиMOVC. Все или часть стека может находиться в данной области. Эта область включает в себя областьDATAи 128 байт выше нее.

SFR– Регистр специальных функций. ВыбранныеCPUрегистры и управление периферией и статусные регистры, обращение путем только прямой адресации.

XDATA– «Внешние» данные или вспомогательная (дополнительная) память. Дуплицирует классическую 80С51 64Kbобласть данных, адресуемая через командуMOVX, используяDPTR, R0 иR1. Вся или часть этого пространства может быть включена в чип.LPC932 имеет 512 байт данных на чипеXDATAпамяти.

CODE– 64Kbадресного пространства, получая доступ как часть выполнения программы и через командуMOVC.LPC932 имеет 8Kbвстроенной памяти областиCODE.

Размещение DataRAM

768 байт данных встроенной RAM-памяти

Прерывания.

LPC932 использует четырехуровневую структуру приоритетов. Это позволяет огромную гибкость в управлении и обращении 15 источников прерываний дляLPC932.

Каждый источник прерываний может быть отдельно включен или отключен путем установки или снятия в регистре управления прерываниями (IEN0 иIEN1).IEN0 регистр также содержит глобальный включающий бит,EA, который включает все прерывания.

Каждый источник прерываний может быть индивидуально запрограммирован на один из 4-х уровней приоритета путем установки или снятия битов в регистре приоритетов прерываний IP0,IP0HиIP1 иIP1H. Программа обработки прерывания может быть прервана прерыванием более высокого приоритета, но не прерыванием того же или более низкого приоритета. Программа обработки прерывания наивысшего приоритета не может быть прервана никаким другим прерыванием. Если одновременно поступают запросы сразу от двух источников прерываний разных приоритетов, обслуживается запрос с наивысшим приоритетом.

Если запросы на прерывание обрабатываются в начале командного цикла, внутренняя последовательность опроса решает какой из них обслуживается. Это называется арбитражное упорядочение. Такая система используется при обработке запросов только одного и того же приоритета.

Таблица 4 суммирует данные об источниках прерываний, флаговых битах и адресов векторов программ обработки прерываний, битов включения , битах приоритета, порядке опроса и какой из прерываний может «разбудить» CPUиз состояния выключенного питания.

Структура уровней приоритета.

Порты ввода/вывода

LPC932 имеет 4 порта ввода/вывода: порт 0, порт 1, порт 2, порт 3. Порты 0, 1 и 2 – 8-ми битные, а порт 3 – 2-х битный. Точное число контактов ввода.вывода, имеющихся в наличие зависит от выбранной частоты и опций сброса (см. Таблицу)

Конфигурации порта

Все, кроме трех контактов ввода/вывода на LPC932 могут быть сконфигурированы программным обеспечением к одному типу из четырех на побитном базисе, как указано в таблице 6. Типы: квази-двунаправленные (стандартный выходной вывод 80С51), двутактный (pull-push), открытый сток, вход. Два конфигурационных регистра для каждого порта выбирают тип для каждого контакта.

P.1.5 ( неRST) может быть только входом и не конфигурируется.

P1.2 (SCL/T0) иP1.3 (SDA/INT0) могут быть только сконфигурированы либо только как входы, либо открытый сток.

Таблица 6.

Квази-двунаправленный вывод.

Квази-двунаправленный выходы могут быть использованы как вход, и как выход без необходимости переконфигурации. Это возможно когда на выходе логическая единица, и он не управляется, что позволяет внешнему устройству установить его в 0. Когда на выходе 0, он управляется хорошо и способен поглотить большой ток. Здесь три повышающих транзистора в квази-двунаправленном выходе, которые служат различным целям.

Один из транзистором, называемый “очень слабый” повышатель, всегда включен, когда защелка порта содержит 1. А так как в цепи ток мал, то он установит 1, если тот болтался.

Второй транзистор, «слабый», когда защелка порта для контакта содержит 1 и сам контакт находится в 1. Этот транзистор обепечивает основной источник тока для квази-двунаправленного порта, который выдает 1.

Третий транзистор – «сильный», усилитель, транзистор используетсяч для ускорения перехода сигнала с 0 в 1 в квази-двунаправленном выходе, когда защелка порта переходит из 0 в 1. Когда это случается, транзистор включается за два такта CPUбыстро переводя вывод из 0 в 1.

Структура порта на рис 10

Хотя LPC932 – 3Vустройство, большинство контактов достаточно толерантны и к 5V. Если на контакте – 5Vи контакт сконфигурирован как квази-двунаправленный, ток потечет с контакта кVdd, вызывая дополнительное потребление мощности. Однако, подавать 5Vк контактам, сконфигурированным как квази-двунаправленные не рекомендуется.

Квази-двунаправленный порт имеет вход на триггере Шмидта, который подавляет помехи.

Конфигурация открытого стока.

Выход, постоенный на открытом стоке выключает все повышающие транзисторы и работает только понижающим транзистором на контакте, когда защелка порта содержит логический 0. Для формирования высокого уровня напряжения при запирании транзистора на выходе элемента с открытым коллектором требуется подключить резистор, соединенный с Vdd.

Схема порта показана на рис 11.

Конфигурация порта с ОК имеет вход на триггере Шмидта с подавлением помех.

Конфигурация входа.

Нарисована на рис. 12. Вход – на триггере Шмидта с подавлением помех.

Двутактный вывод.

Двутактный выход имеет такую же структуру запирания как у ОК и квази-двунаправленный выход, но обеспечивает продолжительное постоянное насыщение, когда защелка порта в логической единице. Такой режим контакта используется когда необходимо большой ток на выходе.

Структура – на рис. 13.

Вход – на триггере Шмидта с контуром подавления помех.

Аналоговые функции порта 0.

Контроль электропитания.

LPC932 включает в себя функции слежения за электропитанием, разработанных для предотвращения неправильных операций в процессе запуска или при сбое питания или спад при операции. Это достигается с помощью двух аппаратных функций:Power-onDetect(Обнаружение запуска) иBrownoutDetect(обнаружение спада).

Обнаружение спада.

Функция BrownoutDetectопределяет случаи падение напряжения электропитания ниже определенного уровня. Операция по умолчанию при наступлении такого события для данной функции – вызов перезагрузки процессора. Однако, она может быть альтернативно сконфигурирована для генерации прерывания путем установкиBOI(PCON.4) бит иEBO(IEN0.5) бит.

Включение и отключение BrownoutDetectionвыполняется черезBOPD(PCON.5) бит, битовое полеPMOD1-0 (PCON1-0) и бит конфигурации пользователяBOE(UCFG1.5). ЕслиBOEв непрограммируемом состоянии, данная функция отключена вне зависимости от состоянияPMOD1-0 иBOPD. ЕслиBOEв состоянии программирования, тоPMOD1-0 иBOPDбудут определять будет ли данная функция включена или отключена.PMOD1-0 используется для выбора режима уменьшения энергопотребления. ЕслиPMOD1-0 = «11», то схема дляBrownoutDetectionотключена для низкого энергопотребления.BOPDпо умолчанию «0», то это указывает на то, что функция включена при включении электропитания, если запрограммированBOE.

Если BrownoutDetectionвключена, то рабочий диапазон напряжения дляVDD– 2.7V-3.6V, и условие для выполнения функции наступает, если уровеньVDD падает нижеBrownouttipvoltage(VBO) и инвертируется когдаVDD становится вышеVBO. Если данная функция отключена, то рабочий диапазон напряжения дляVDD составляет 2.4V– 3.6V. Если устройствоLPC932 должно работать при напряжении менее 2.7V, тоBOEдолжно быть оставлено в непрограммируемом состоянии для того, чтобы была возможна работа на 2.4V, иначе постоянные сбросы могут предотвратить устройство от функционирования.

Если BrownoutDetectionвключено (BOEпрограммирован,PMOD1-0 не равен «11»,BOPD= 0),BOF(RSTSRC.5) будет установлен в случает срабатывания функции, независимо от того сброс или прерывание включены,BOFостанется в установленном состоянии, до тех пор пока программно не будет установлен «0». Примечание: еслиBOEне запрограммирован, тоBOF– бессмыслен. ЕслиBOEзапрограммирован и происходит включение питания, тоBOFбудет установлен в дополнение к флагу включения питания (POF–RSTSRC.4).

Для правильной активации BrownoutDetect, точные времена падения и взлетаVDD должны быть замечены. Смотрите инструкцию для конкретных данных.

|

BOE |

PMOD1-0 |

BOPD |

BOI |

EBO |

EA |

Description |

|

0 (erased) |

xx |

x |

x |

x |

x |

|

|

1 (programmed) |

11 |

х |

х |

х |

х |

|

|

|

|

|

|

|

| |

|

|

|

|

|

| ||

|

|

|

|

| |||

|

|

|

| ||||

|

|

|

|

Обнаружение включения питания.

Power-onDetectимеет схожую функцию, как и уBrownoutDetect, но предназначен для работы при начальном включении питания, до тех пор пока питание не достигнет уровня , на которомBrownoutDetectможет работать. ФлажокPOF(RSTSRC.4) устанавливается для указания, что подано питание. ФлажокPOFбудет установлен до тех пор, пока не снимется программным обеспечением путем записи «0» в бит. Примечание: еслиBOE(UCFG1.5) запрограммирован, тоBOF(RSTSRC.5) будет установлен при установкеPOF. ЕслиBOEне запрограммирован, тоBOF– бессмыслен.

Режимы уменьшения энергопотребления.

LPC932 поддерживает три различных режима уменьшения энергопотребления, которые определяютсяSFRбитамиPCON.1-0 (см. таблицу 9)

|

PMOD 1 |

PMOD 0 |

Description |

|

0 |

0 |

Нормальный режим (по умолчанию) |

|

0 |

1 |

Состояние бездействия. Состояние бездействия оставляет периферию в рабочем состоянии для того, чтобы активизировать процессор при генерации прерывания. Любое включенное прерывание или сброс может прервать состояние бездействия. |

|

1 |

0 |

Состояние отключенного питания. Состояние отключенного питания останавливает резонатор для уменьшения энергопотребления. LPC932 выходит из данного состояния либо через сброс, или через определенные прерывания – внешние выводы INT0/INT1, прерывание спада, клавиатура, часы реального времени/системный таймер, сторожевой таймер или компаратор. Пробуждение по сбросу включено только в том случае, если соответствующий сброс включен, и пробуждение по прерываниювключено втом случае, если соответствующее прерывание включено и бит EA SFR (IEN 0.7) установлен.В режиме выключенного питания внутренний RC резонатор отключен до тех пор, пока не выбран RC резонатор как тактовый генератор и RTC не включен. В режиме выключенного питания, напряжение электропитания может быть уменьшено до состояния сохранения данных памяти в RAM – VRAM. Это позволяет удерживать содержимое RAM в состоянии, когда произошел переход в режим выключения питания. Сохранение содержимого SFR не гарантируется при уменьшении после уменьшения VDD до VRAM, поэтому рекомендуется пробуждение процессора производить через сброс в данной ситуации. VDD должно быть повышено до нормального уровня перед выходом из состояния выключенного питания. Когда процессор просыпается из режима выключенного питания, немедленно производится запуск резонатора и начинается выполнение, когда резонатор стабилен. Стабильность определяется подсчетом 1024 тактовых импульсов CPU после запуска, когда используется одна из конфигураций кварцевого резонатора, или после 256 тактовых импульсов после запуска в случае использования внутреннего RC резонатора или источника внешнего тактового сигнала. Несколько функция чипа продолжают выполняться и используют питание в режиме выключенного питания, повышая энергопотребление в состоянии выключенного питания. Функции включают:

|

|

1 |

1 |

Состояния полностью отключенного питания. Практически полностью повторяет состояние отключенного питания, за исключением того, что график обнаружение спада и компараторы напряжения выключены для сохранения дополнительного питания. Заметьте, что сброс по спаду или прерывания не случится. Прерывания компаратора напряжения и прерывания обнаружения спада не могут использоваться в качестве источника пробуждения. Внутренний RC резонатор отключен до тех пор, пока не выбран RC резонатор как тактовый генератор и RTC не включен. Поддерживаются следующие источники пробуждения:

|

Сброс

Вывод P1/#RSTможет функционировать либо как активный низкий вход сброса или как цифровой вход,P1.5. БитRPE(ResetPinEnable) бит вUCFG1, при установке в 1, включает функцию внешнего входа сброса наP1.5. При сбросе бита,P1.5 может быть использован как входной контакт.

Примечание: в течение включения питания, выбор RPEперекрыт и этот вывод всегда функционирует как вход сброса. При подключении внешней цепи, эта внешняя цепь не должна «держать» на входе низкий уровень при включении питания, иначе всегда будет сброс. После включения питания этот вход будет функционировать либо как вход внешнего сброса, либо как цифровой вход, как и было определо ранее самимRPEбитом. Только сброс при включении питания временно перекроет саму функциюRPE.

Сброс может быть инициирован от следующих источников:

вход внешнего прерывания (при включении питания, если пользователь сконфигурирован через UCFG1)

обнаружение включение питания

обнаружение спада

сторожевой таймер

программный сброс

UART

Для каждого источника сброса существует флаг в регистре сброса, RSTSCR. Пользователь может прочитать содержимое регистра для того, чтобы выяснить источник последнего сброса. Эти флаги могут быть программно сброшены, путем установки в ‘0’ соответствующего бита. Более одного бита можно установить, если:

В течении сброса при включении питания, оба PODиBOFустанавливаются, а все остальное стирается.

Для любого другого сброса, любые ранее установленные биты, которые не были стерты, останутся в том же состоянии.

Таймеры/счетчики 0 и 1.

В микроконтроллере LPC932 имеется 2 таймера/счетчика общего назначения, которые совместимы со стандартом 80C51. Это Таймер 0 (T/C0) и Таймер 1 (T/C1). Каждый из них может быть запрограммирован на работу в режиме таймера (подсчет импульсов, поступающих от внутреннего тактового генератора) или счетчика событий (подсчет импульсов, поступающих с внешних устройств через входы T0 и T1). Также добавлена возможность автоматического переключения вывода Tx при переполнении таймера.

В режиме таймера, содержимое регистра инкрементируется в каждом машинном цикле (МЦ).

В режиме счетчика, содержимое регистра инкрементируется под воздействием внешнего сигнала на соответствующих входах T0 и T1, при переходе из 1 в 0 (т.е. по спаду сигнала). В этом режиме сигнал на внешних выводах проверяется один раз за каждый машинный цикл. Если сигнал имеет высокий уровень в течение одного МЦ, а в следующем МЦ – низкий уровень, то счетчик инкрементируется. Новое значение счетчика записывается в регистр в течение цикла следующего за тем, в котором был обнаружен переход. Поскольку для распознавания перехода необходимо 2 машинных цикла (4 такта CPU, Central Processing Unit), то максимальная частота подсчета входных сигналов составляет 1/4 опорной частоты CPU. Ограничений на длительность входных сигналов нет, но изменение значения счетчика гарантировано только в том случае, если сигнал на входе держится как минимум в течение одного машинного цикла.

Управление работой и взаимодействием T/C с подсистемой прерывания осуществляется посредством нескольких регистров специального назначения:

- TMOD и TAMOD, для задания режима работы;

- TCON, для управления работой таймера/счетчика.

В ыбор

режима “таймер” или “счетчик”

осуществляется с помощью бита TnC/T в

регистре TMOD. Таймеры 0 и 1 имеют 5 режимов

работы (режим 0, 1, 2, 3 и 6), которые выбираются

с помощью битов TnM1 и TnM0 в регистре TMOD и

бита TnM2 в регистре TAMOD (назначение

отдельных разрядов регистров TMOD и TAMOD

приведено в таблицах 1 и 2, соответственно).

ыбор

режима “таймер” или “счетчик”

осуществляется с помощью бита TnC/T в

регистре TMOD. Таймеры 0 и 1 имеют 5 режимов

работы (режим 0, 1, 2, 3 и 6), которые выбираются

с помощью битов TnM1 и TnM0 в регистре TMOD и

бита TnM2 в регистре TAMOD (назначение

отдельных разрядов регистров TMOD и TAMOD

приведено в таблицах 1 и 2, соответственно).

Таблица 1. Регистр режима (TMOD, Timer/Counter Mode Control register)

|

Бит |

Обозначение |

Назначение |

|

TMOD.7 |

T1GATE |

У |

|

TMOD.6 |

T |

Выбор режима “таймер” или “счетчик” для таймера 1. Бит сбрасывается для выбора режима “таймер”. Установка бита приводит к выбору режима “счетчик”. |

|

TMOD.5,4 |

T1M1, T1M0 |

Выбор режима работы таймера 1. Эти биты используются вместе с битом T1M2 регистра TAMOD для задания режима работы таймера 1. |

|

TMOD.3 |

T0GATE |

У |

|

TMOD.2 |

T |

Выбор режима “таймер” или “счетчик” для таймера 0. Бит сбрасывается для выбора режима “таймер”. Установка бита приводит к выбору режима “счетчик”. |

|

TMOD.1,0 |

T0M1, T0M0 |

Выбор режима работы таймера 0. Эти биты используются вместе с битом T0M2 регистра TAMOD для задания режима работы таймера 0. |

Таблица 2. Вспомогательный регистр режима (TAMOD, Timer/Counter Auxiliary

Mode Control register)

|

Бит |

Обозначение |

Назначение |

|

TAMOD.7-5 |

- |

Зарезервировано. Эти биты не должны устанавливаться в 1 при программировании микроконтроллера. |

|

TAMOD.4 |

T1M2 |

Дополнительный бит выбора режима для таймера 1. Используется вместе с битами T1M1 и T1M0 (регистр TMOD) для задания режима работы таймера 1. |

|

TAMOD.3-1 |

- |

Зарезервировано. Эти биты не должны устанавливаться в 1 при программировании микроконтроллера. |

|

TAMOD.0 |

T0M2 |

Дополнительный бит выбора режима для таймера 0. Используется вместе с битами T0M1 и T0M0 (регистр TMOD) для задания режима работы таймера 0. |

Назначение режимов 0, 1, 2 и 6 одинаковое для обоих таймеров/счетчиков. Режим 3 различен для T/C0 и T/C1 (пояснение режимов работы таймеров/счетчиков приведено в таблице 3).

Таблица 3. Режимы работы таймера

|

Биты TnM2 – TnM0 |

Режим работы таймера |

|

000 |

Младшая часть таймера TLn функционирует как 5-разрядный предделитель. |

|

001 |

THn и TLn каскадно соединены. Разрядность таймера/счетчика равна 16. |

|

010 |

Автоперезагружаемый 8-разрядный таймер/счетчик. При переполнении TLn в него загружается значение, находящееся в THn. |

|

011 |

Таймер 0 образует 2 независимых 8-разрядных таймера/счетчика. TL0 управляется с помощью битов управления таймера 0. TH0 управляется с помощью битов управления таймера 1. Таймер 1 остановлен. |

|

100 |

Зарезервировано. Пользователь не должен задавать такой режим. |

|

101 |

Зарезервировано. Пользователь не должен задавать такой режим. |

|

110 |

Режим широтно-импульсного модулятора (ШИМ). |

|

111 |

Зарезервировано. Пользователь не должен задавать такой режим. |

правление

разрешением работы таймера 1. Если бит

установлен в 1, то работа таймера/счетчика

разрешена, только если выводINT1

имеет высокий уровень и установлен

бит TR1.

Если бит сброшен, то работа таймера 1

разрешена, если установлен бит TR1.

правление

разрешением работы таймера 1. Если бит

установлен в 1, то работа таймера/счетчика

разрешена, только если выводINT1

имеет высокий уровень и установлен

бит TR1.

Если бит сброшен, то работа таймера 1

разрешена, если установлен бит TR1. 1C/T

1C/T правление

разрешением работы таймера 0. Если бит

установлен в 1, то работа таймера/счетчика

разрешена, только если выводINT0

имеет высокий уровень и установлен

бит TR0.

Если бит сброшен, то работа таймера 0

разрешена, если установлен бит TR0.

правление

разрешением работы таймера 0. Если бит

установлен в 1, то работа таймера/счетчика

разрешена, только если выводINT0

имеет высокий уровень и установлен

бит TR0.

Если бит сброшен, то работа таймера 0

разрешена, если установлен бит TR0. 0C/T

0C/T