Capture/Compare Unit (CCU)

Блок фиксации/сравнения

This unit features:

Характеристики блока:

• A 16-bit timer with 16-bit reload on overflow

16-разрядный таймер с перезагрузкой по переполнению

• Selectable clock (CCUCLK) , with a prescaler to divide the clock source by any integer between 1 and 1024.

Изменяемый тактовый сигнал с предварительным делителем частоты, позволяющим делить тактовый сигнал на любое целое число от 1 до 1024

• 4 Compare / PWM outputs with selectable polarity

4 выхода сравнения/PWM с изменяемой полярностью

• Symmetrical / Asymmetrical PWM selection

Выбор симметричного/ассиметричного режима PWM

• 2 Capture inputs with event counter and digital noise rejection filter

2 канала ввода с счетчиком событий и цифровым противопомеховым заграждающим фильтром

• 7 interrupts with common interrupt vector (one Overflow, 2xCapture, 4xCompare),

7 каналов прерываний с общим вектором прерываний (один – по переполнению, 2 – по вводу, 4 – по сравнению)

• Safe 16-bit read/write via shadow registers.

Сохранение 16 разрядов чтения/записи посредством регистра теневой памяти

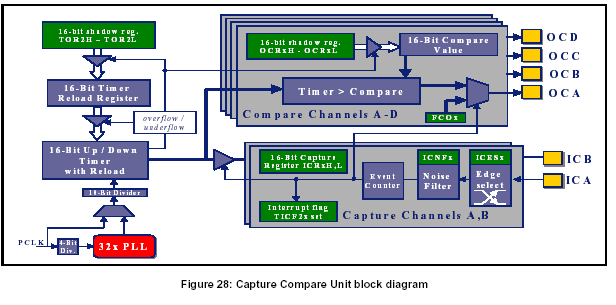

Figure 28: Capture Compare Unit block diagram

Рис. 28 Блок-схема CCU

CCU Clock (CCUCLK)

The CCU runs on the CCUCLK, which can be either PCLK in basic timer mode or the output of a PLL (see Figure 28). The PLL is designed to use a clock source between 0.5 MHz to 1 MHz that is multiplied by 32 to produce a CCUCLK between 16 MHz and 32 MHz in PWM mode (asymmetrical or symmetrical). The PLL contains a 4-bit divider (PLLDV3:0 bits in the TCR21 register) to help divide PCLK into a frequency between 0.5 MHz and 1 MHz

CCU работает по сигналу CCUCLK, в качестве которого может выступать сигнал PCLK в основном режиме таймера или сигнал с выхода PLL (см. рис. 28). PLL предназначен для возможности использования источника тактовых импульсов в диапазоне частот от 0,5 МГц до 1 МГц; этот сигнал умножается на 32, чтобы выработать сигнал CCUCLK с частотой в диапазоне от 16 МГц до 32 МГц в режиме PWM (ассиметричном или симметричном). PLL включает в себя 4-разрядный делитель (PLLDV3:0 биты в регистре TCR21), чтобы реализовать деление сигнала PCLK до частоты в диапазоне от 0,5 МГц до 1 МГц.

CCU Clock prescaling

Предварительный делитель частоты

This CCUCLK can further be divided down by a prescaler. The prescaler is implemented as a 10-bit free-running counter with programmable reload at overflow. Writing a value to the prescaler will cause the prescaler to restart.

Сигнал CCUCLK в дальнейшем может быть поделен с помощью предварительного делителя частоты. Предварительный делитель частоты осуществлен как 10-разрядный независимый счетчик с программируемой загрузкой по переполнению. Запись значения в предварительный делитель частоты вызовет возобновление его работы.

Basic timer operation

Базовый процесс таймера

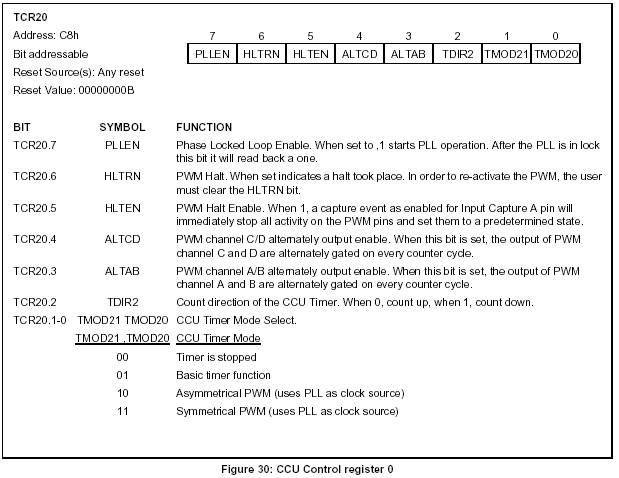

The Timer is a free-running up/down counter counting at the pace determined by the prescaler. The timer is started by setting the CCU Mode Select bits TMOD21 and TMOD20 in the CCU Control Register 0 (TCR20) as shown in the table in the TCR20 register description (Figure 30).

The CCU direction control bit, TDIR2, determines the direction of the count. TDIR2=0: Count up, TDIR2=1: Count down. If the timer counting direction is changed while the counter is running, the count sequence will be reversed in the CCUCLK cycle following the write of TDIR2. The timer can be written or read at any time and newly-written values will take effect when the prescaler overflows. The timer is accessible through two SFRs, TL2(low byte) and TH2(high byte). A third 16-bit SFR, TOR2H:TOR2L, determines the overflow reload value. TL2, TH2 and TOR2H, TOR2L will be 0 after a reset.

Таймер – независимый двунаправленный счетчик с шагом, определяемым предварительным делителем частоты. Таймер запускается установкой битов TMOD21 и TMOD20 в нулевом регистре управления CCU (TCR20), как показано в таблице в описании регистра TCR20 (рис.30).

Бит управления направлением CCU, TDIR2, определяет направление счета. TDIR2=0: прямой счет, TDIR2=1: обратный счет. Если направление счета таймера изменяется во время работы счетчика, последовательность счета будет изменена в противоположную сторону в следующий после записи бита TDIR2 период сигнала CCUCLK. Значение таймера может быть записано или считано в любое время и вновь записанные значения окажут действие, когда предварительный делитель частоты переполнится. Таймер доступен посредством двух регистров SFRs, TL2 (младший байт) и TH2(старший байт). Третий 16-разрядный регистр, TOR2H; TOR2L, определяет загружаемое значение при переполнении. TL2, TH2 и TOR2H, TOR2L будут установлены в 0 после выполнения сброса (reset).

Up-counting: When the timer contents are FFFFH, the next CCUCLK cycle will set the counter value to the contents of TOR2H:TOR2L.

Прямой счет: когда содержимое таймера будет равно FFFFH, в следующий период сигнала CCUCLK в счетчик будет записано содержимое регистра TOR2H:TOR2L.

Down-counting: When the timer contents are 0000H, the next CCUCLK cycle will set the counter value to the contents of TOR2H:TOR2L. During the CCUCLK cycle when the reload is performed, the CCU Timer Overflow Interrupt Flag (TOIF2) in the CCU Interrupt Flag Register (TIFR2) will be set, and, if the EA bit in the IEN0 register and ECCU bit in the IEN1 register (IEN1.4) are set, program execution will vector to the overflow interrupt. The user has to clear the interrupt flag in software by writing a logical ‘0’ to it.

Обратный счет: когда значение таймера будет равно 0000H, в следующий период сигнала CCUCLK в счетчик будет записано содержимое регистра TOR2H:TOR2L. В течение периода сигнала CCUCLK, когда выполняется загрузка, будет установлен флаг прерывания CCU по переполнению таймера (TOIF2) в регистре флагов прерывания CCU (TIFR2), и если EA-бит в регистре IEN0 и ECCU-бит в регистре IEN1 (IEN1.4) установлены, то выполнение программы будет передано прерыванию по переполнению. Пользователь должен снять флаг прерывания с помощью программного обеспечения, записав логический ‘0’.

When writing to the reload registers, TOR2H and TOR2L, the values written are stored in two 8-bit shadow registers. In order to latch the contents of the shadow registers into TOR2H and TOR2L, the user must write a logical one to the CCU Timer Compare/Overflow Update bit TCOU2, in CCU Timer Control Register 1 (TCR21). The function of this bit depends on whether the timer is running in PWM mode or in basic timer mode. In basic timer mode, writing a one to TCOU2 will cause the values to be latched immediately and the value of TCOU2 will always read as zero. In PWM mode, writing a one to TCOU2 will cause the contents of the shadow registers to be updated on the next CCU Timer overflow. As long as the latch is pending, TCOU2 will read as one and will return to zero when the latching takes place. TCOU2 also controls the latching of the Output Compare registers OCR2A, OCR2B and OCR2C.

При записи значений в регистры перезагрузки, TOR2H и TOR2L, эти значения хранятся в двух 8-разрядных теневых регистрах. Для того, чтобы сохранить содержимое теневых регистров в TOR2H и TOR2L, пользователь должен записать логическую единицу в бит TCOU2, в регистре TCR21. Назначение этого бита зависит от того, работает ли таймер в режиме PWM или в базовом режиме таймера. В базовом режиме таймера запись единицы в TCOU2 вызовет немедленное сохранение значений, а значение TCOU2 всегда будет читаться как ноль. В режиме PWM, запись единицы в TCOU2 приведет к обновлению содержимого теневых регистров при следующем переполнении таймера CCU. Пока в защелку не будут загружены значения, TCOU2 будет читаться как единица и как ноль, когда значения будут загружены. TCOU2 также контролирует загрузку регистров OCR2A, OCR2B и OCR2C.

When writing to timer high byte, TH2, the value written is stored in a shadow register. When TL2 is written, the contents of TH2’s shadow register is transferred to TH2 at the same time that TL2 gets updated. Thus, TH2 should be written prior to writing to TL2. If a write to TL2 is followed by another write to TL2, without TH2 being written in between, the value of TH2 will be transferred directly to the high byte of the timer.

При записи старшего байта таймера, TH2, записанное значение хранится в теневом регистре. При записи TL2, содержимое теневого регистра, хранящего TH2, переносится в TH2 в то же самое время, когда обновляется TL2. Таким образом, TH2 должен быть записан раньше TL2. Если за записью TL2 следует другая запись TL2 без записи TH2 между ними, значение TH2 будет перенесено прямо в старший байт таймера.

If the 16-bitCCU Timer is to be used as an 8-bit timer, the user can write FFh (for upcounting) or 00h (for downcounting) to TH2. When TL2 is written, FFh:TH2 (for upcounting) and 00h (for downcounting) will be loaded to CCU Timer. The user will not need to rewrite TH2 again for an 8-bit timer operation unless there is a change in count direction.

Если 16-разрядный таймер CCU необходимо использовать как 8-разрядный таймер, пользователь может записать FFh (для прямого счета) или 00h (для обратного счета) в TH2. Когда TL2 будет записано, в таймер CCU будет загружено FFh:TH2 (для прямого счета) и 00h (для обратного счета). Пользователю не нужно будет перезаписывать TH2 снова для работы 8-разрядного таймера, пока не будет изменено направление счета.

When reading the timer, TL2 must be read first. When TL2 is read, the contents of the timer high byte are transferred to a shadow register in the same PCLK cycle as the read is performed. When TH2 is read, the contents of the shadow register are read instead. If a read from TL2 is followed by another read from TL2 without TH2 being read in between, the high byte of the timer will be transferred directly to TH2.

При чтении значения таймера TL2 должен быть прочитан первым. При чтении TL2 содержимое старшего байта таймера переносится в теневой регистр в течение того же периода, когда выполняется чтение. При чтении TH2 вместо него будет прочитано содержимое теневого регистра. Если за чтением из TL2 следует другое чтение TL2 без чтения содержимого TH2 между ними, старший байт таймера будет перемещен прямо в TH2.

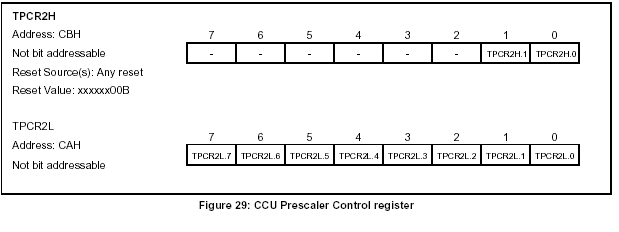

Figure 29: CCU Prescaler Control register

Рис. 29: Регистр управления предварительным делителем частоты CCU

* примечания к рисунку 29:

Not bit addressable – нет побитовой адресации

Reset Source(s): Any reset – источник(и) сброса: любой сброс

Reset Value: хххххх00В – значение после сброса: хххххх00В

Figure 30: CCU Control register 0

Рис. 30: Нулевой регистр управления ССU

* примечания к рисунку 30:

Bit addressable – побитовая адресация

Reset Source(s): Any reset – источник(и) сброса: любой сброс

Reset Value: 00000000В – значение после сброса: 00000000В

|

Бит |

Обозначение |

Назначение |

|

TCR20.7

|

PLLEN

|

Разрешение работы схемы PLL. 1- начало работы PLL. После …, он будет читаться как единица.

|

|

TCR20.6

|

HLTRN

|

Остановка PWM. Когда этот бит установлен в 1, это показывает, что остановка имела место. Для того, чтобы возобновить PWM, пользователь должен снять этот бит (установить его в 0). |

|

TCR20.5

|

HLTEN

|

Разрешение остановки PWM. Когда это бит устанавливается в 1, ввод, разрешенный на канале А, немедленно остановит деятельность на входах PWM и установит их в предопределенное состояние. |

|

TCR20.4

|

ALTCD

|

Разрешение поочередного вывода каналов C/D PWM. Когда этот бит установлен, на выходе PWM каждый период счетчика чередуются каналы C и D. |

|

TCR20.3

|

ALTAB

|

Разрешение поочередного вывода каналов A/B PWM. Когда этот бит установлен, на выходе PWM каждый период счетчика чередуются каналы А и В.

|

|

TCR20.2

|

TDIR2

|

Направление счета таймера CCU. 0 - прямой счет, 1 - обратный счет.

|

|

TCR20.1-0 |

TMOD21,TMOD20 TMOD20,TMOD21 00 01 10 11 |

Выбор режима таймера CCU

Таймер остановлен Основная функция таймера Асимметричный PWM (PLL используется как источник Симметричный PWM тактовых импульсов) |

Output compare

//Сравнение на выходе

The four output compare channels A, B, C and D are controlled through four 16-bit SFRs, OCRAH:OCRAL, OCRBH:OCRBL, OCRCH:OCRCL, OCRDH: OCRDL. Each output compare channel needs to be enabled in order to operate. The channel is enabled by selecting a Compare Output Action by setting the OCMx1:0 bits in the Capture Compare x Control Register – CCCRx (x=A, B, C, D). When a compare channel is enabled, the user will have to set the associated I/O pin to the desired output mode to connect the pin. (Note: The SFR bits for port pins P2.6, P1.6, P1.7, P2.1 must be set to ‘1’ in order for the compare channel outputs to be visible at the port pins.) When the contents of TH2:TL2 match that of OCRxH:OCRxL, the Timer Output Compare Interrupt Flag - TOCFx is set in TIFR2. This happens in the CCUCLK cycle after the compare takes place. If EA and the Timer Output Compare Interrupt Enable bit – TOCIE2x (in TICR2 register), as well as ECCU bit in IEN1 are all set, the program counter

will be vectored to the corresponding interrupt. The user must manually clear the bit by writing a ‘0’ to it.

Четыре выходных канала сравнения A, B, C и D управляются четырьмя 16-разрядными регистрами SFRs - OCRAH:OCRAL, OCRBH:OCRBL, OCRCH:OCRCL, OCRDH: OCRDL. Для работы, каждый выход должен находиться в состоянии enable, что может быть достигнуто установкой битов OCMx1:0 в регистрах управления CCCRx (x=A, B, C, D). После этого пользователь будет должен установить соответствующий контакт в желаемый режим вывода. (Замечание: биты регистра SFR для выводов Р2.6, Р1.6, Р1.7, Р2.1 должны быть установлены в ‘1’, чтобы выходы каналов компаратора были видимыми для этих контактов). Когда содержимое TH2:TL2 совпадает с OCRxH:OCRxL, в TIFR2 устанавливается флаг прерывания TOCFx. Это происходит в следующий после сравнения период CCUCLK. Если EA и бит TOCIE2x (в регистре TICR2), так же как и бит ECCU в IEN1 установлены, программный счетчик будет направлен на соответствующее прерывание. Пользователь должен вручную снять бит путем записи ‘0’ в него.

Two bits in OCCRx, the Output Compare x Mode bits OCMx1 and OCMx0 select what action is taken when a compare match occurs. Enabled compare actions take place even if the interrupt is disabled.

Два бита в OCCRх, биты OCMx1 и ОСМх0 выбирают, какое действие произвести, когда выполняется сравнение. Разрешенные действия сравнения имеют место, даже если прерывание запрещено.

In order for a Compare Output Action to occur, the compare values must be within the counting range of the CCU timer.

Для того, чтобы выходное действие сравнения произошло, сравниваемая величина должна находиться внутри диапазона счета таймера CCU.

When the compare channel is enabled, the I/O pin (which must be configured as an output) will be connected to an internal latch controlled by the compare logic. The value of this latch is zero from reset and can be changed by invoking a forced compare. A forced compare is generated by writing a ‘1’ to the Force Compare x Output bit – FCOx bit in OCCRx. Writing a one to this bit generates a transition on the corresponding I/O pin as set up by OCMx1/OCMx0 without causing an interrupt. In basic timer operating mode the FCOx bits always read zero. (Note: This bit has a different function in PWM mode.) When an output compare pin is enabled and connected to the compare latch, the state of the compare pin remains unchanged until a compare event or forced compare occurs.

Когда канал сравнения открыт, I/О пин (который должен быть настроен как выход) будет подсоединен к внутренней защелке, контролируемой логикой сравнения. Значение этого регистра - ноль с момента сброса, но оно может быть изменено выполнением вынужденного сравнения. Вынужденное сравнение вызывается записью ‘1’ в бит FCOx в регистре OCCRх. Запись единицы в этот бит генерирует переход на соответствующий пин, как установка OCMx1/OCMx0 без вызова прерывания. В базовом режиме работы таймера биты FCOx всегда читаются, как нули. (Замечание: этот бит имеет другое назначение в режиме PWM). Когда контакт сравнения на выходе доступен и соединен с регистром сравнения, состояние контакта остается неизменным до тех пор, пока не произойдет сравнение (может быть и вынужденное).

Figure 31: Capture Compare Control register

Рис.31 Регистр управления

* примечания к рисунку 31:

Not bit addressable – нет побитовой адресации

Reset Source(s): Any reset – источник(и) сброса: любой сброс

Reset Value: 00000000В – значение после сброса: 00000000В

|

Бит |

Обозначение |

Назначение |

|

СССRх.7

|

ICECx2

|

Бит, определяющий задержку ввода (фиксации). Подробности см. в таблице 11 |

|

СССRх.6

|

ICECx1

|

Бит, определяющий задержку ввода (фиксации). Подробности см. в таблице 11 |

|

СССRх.5

|

ICECx0

|

Бит, определяющий задержку ввода (фиксации). Подробности см. в таблице 11 |

|

СССRх.4

|

ICESx

|

Бит выбора фронта, по которому будет происходить ввод (фиксация) 0 - отрицательный фронт 1 - положительный фронт |

|

СССRх.3

|

ICNFx

|

Бит разрешения работы шумового фильтра При 1 для логической установки необходимы четыре последовательных образца одинакового значения для того, чтобы распознать фронт как событие для установки. Образцы подаются на входы каждые два периода CCLK независимо от скорости таймера. |

|

СССRх.2

|

FCOx

|

Вынужденное сравнение, выходной бит. Когда он установлен, это вызывает вынужденное сравнение.

|

|

СССRх.1-0

|

OCMx1,OCMx2 |

Сравнение на выходе, режим. См. Таблицу 12 |

When the user writes to change the output compare value, the values written to OCRH2x and OCRL2x are transferred to two 8-bit shadow registers. In order to latch the contents of the shadow registers into the capture compare register, the user must write a logical one to the CCU Timer Compare/Overflow Update bit TCOU2, in the CCU Control Register 1 - TCR21. The function of this bit depends on whether the timer is running in PWM mode or in basic timer mode. In basic timer mode, writing a one to TCOU2 will cause the values to be latched immediately and the value of TCOU2 will always read as zero. In PWM mode, writing a one to TCOU2 will cause the contents of the shadow registers to be updated on the next CCU Timer overflow. As long as the latch is pending, TCOU2 will read as one and will return to zero when the latch takes place. TCOU2 also controls the latching of all the Output Compare registers as well as the Timer Overflow Reload registers - TOR2.

Когда пользователь изменяет значение выходной сравниваемой величины, значения, записанные в OCRH2x и OCRL2x переносятся в два 8-разрядный теневых регистра. Для того, чтобы загрузить содержимое теневых регистров в регистр сравнения, пользователь должен установить в единицу бит TCOU2 в регистре TCR21. Назначение этого бита зависит от того, в каком режиме работает таймер – в PWM режиме или в основном режиме таймера. В основном режиме таймера запись единицы в TCOU2 вызовет немедленную загрузку значений, а значение бита TCOU2, будет всегда читаться как ноль. В PWM режиме запись единицы в TCOU2 вызовет обновление содержимого теневых регистров при следующем переполнении CCU таймера. Пока защелка находится в ожидании, TCOU2 будет читаться как единица и как ноль, когда загрузка будет осуществлена. TCOU2 также контролирует загрузку всех регистров выходного сравнения, так же, как и регистров перезагрузки по переполнению таймера - TOR2.

Input capture

Ввод

Input capture is always enabled. Each time a capture event occurs on one of the two input capture pins, the contents of the timer is transferred to the corresponding 16-bit input capture register ICRAH:ICRAL or ICRBH:ICRBL. The capture event is defined by the Input Capture Edge Select – ICESx bit (x being A or B) in the CCCRx register. The user will have to configure the associated I/O pin as an input in order for an external event to trigger a capture.

Ввод всегда разрешен. Каждый раз, когда происходит ввод на одном из двух входных каналов, содержимое таймера пересылается в соответствующий 16-разрядный входной регистр ввода ICRAH:ICRAL или ICRBH:ICRBL. Событие ввода определяется битом ICESx (где х может быть А или В) в регистре CCCRx. Пользователь должен будет сконфигурировать соответственный контакт ввода/вывода как вход для того, чтобы внешнее событие синициировало запись.

A simple noise filter can be enabled on the input capture input. When the Input Capture Noise Filter ICNFx bit is set, the capture logic needs to see four consecutive samples of the same value in order to recognize an edge as a capture event. The inputs are sampled every two CCLK periods regardless of the speed of the timer.

Простой шумовой фильтр может быть активен при вводе. Когда бит ICNFx установлен, логика ввода должна просмотреть четыре последовательных образца одного и того же значения для того, чтобы распознать фронт как событие ввода. На входы приходят образцы каждые два периода CCLK, не взирая на скорость таймера.

An event counter can be set to delay a capture by a number of capture events. The three bits ICECx2, ICECx1 and ICECx0 in the CCCRx register determine the number of edges the capture logic has to see before an input capture occurs.

Счетчик событий может быть установлен так, чтобы задерживать ввод на какое-то количество событий по вводу. Три бита ICEx2, ICECx1 и ICECx0 регистра CCCRx определяют количество фронтов, которые должна пропустить логика ввода прежде, чем произойдет ввод.

When a capture event is detected, the Timer Input Capture x (x is A or B) Interrupt Flag – TICF2x (TIFR2.1 or TIFR2.0) is set. If EA and the Timer Input Capture x Enable bit – TICIE2x (TICR2.1 or TICR2.0) is set as well as the ECCU (IEN1.4) bit is set, the program counter will be vectored to the corresponding interrupt. The interrupt flag must be cleared manually by writing a ‘0’ to it.

Когда событие по вводу определено, устанавливается флаг прерывания TICF2x (TIFR2.1 или TIFR2.0). Если EA и бит TICIE2x (TICR2.1 или TICR2.0) установлен, как и бит ECCU (IEN1.4), программный счетчик будет направлен на соответствующее прерывание. Флаг прерывания должен быть снят вручную записью ‘0’ в него.

When reading the input capture register, ICRxL must be read first. When ICRxL is read, the contents of the capture register high byte are transferred to a shadow register. When ICRxH is read, the contents of the shadow register are read instead. (If a read from ICRxL is followed by another read from ICRxL without ICRxH being read in between, the new value of the capture register high byte (from the last ICRxL read) will be in the shadow register.)

Когда происходит чтение, регистр ICRxL должен быть прочитан первым. Когда прочитан регистр ICRxL, содержимое старшего байта этого регистра переносится в теневую регистровую память. При чтении регистра ICRxH вместо него читается содержимое теневой памяти. (Если за процессом чтения из ICRxL следует другой процесс чтения из ICRxL без чтения ICRxH между ними, новое значение старшего байта регистра ввода (с момента последнего чтения ICRxL) будет в теневой регистровой памяти)

Таблица 11: Счетчик задержек события для ввода

*Delay (numbers of edges) – задержка (количество фронтов)

PWM operation

Широтно-импульсная модуляция

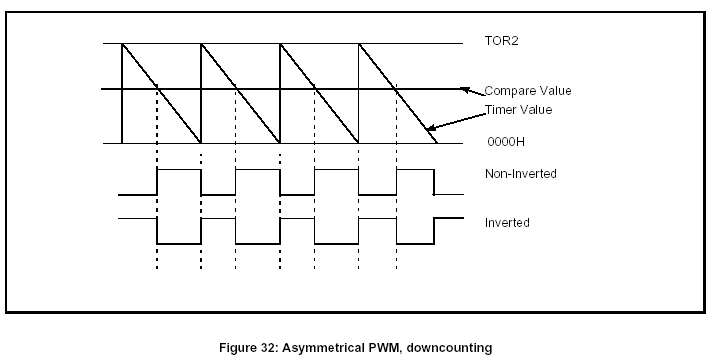

PWM Operation has two main modes, asymmetrical and symmetrical. These modes of timer operation are selected by writing 10H or 11H to TMOD21:TMOD20 as shown in section "Basic timer operation".

Операция PWM имеет два главных режима – асимметричный и симметричный. Эти режимы работы таймера выбираются записью 10Н или 11Н в TMOD21;TMOD20, как показано в разделе «Базовый режим работы таймера».

In asymmetrical PWM operation, the CCU Timer operates in downcounting mode regardless of the setting of TDIR2. In this case, TDIR2 will always read 1.

В асимметричном режиме PWM таймер CCU работает в режиме обратного счета независимо оттого, что записано в TDIR2. В этом случае TDIR2 всегда будет читаться, как 1.

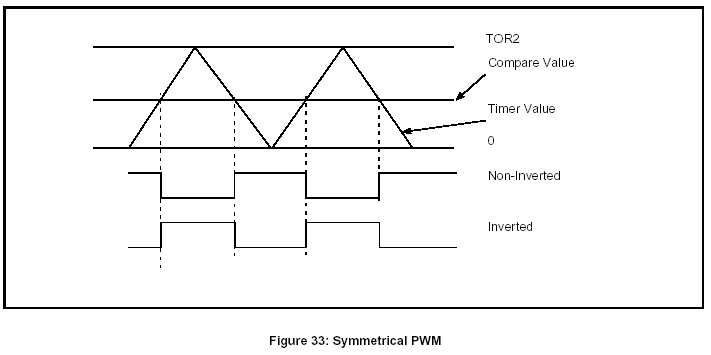

In symmetrical mode, the timer counts up/down alternately and the value of TDIR2 has no effect. The main difference from basic timer operation is the operation of the compare module, which in PWM mode is used for PWM waveform generation. Table 12 shows the behavior of the compare pins in PWM mode.

В симметричном режиме таймер считает, увеличиваясь/уменьшаясь поочередно, и значение TDIR2 не имеет значения. Главное отличие от базового режима работы таймера заключается в работе модуля сравнения, который в режиме PWM используется для генерации временной диаграммы PWM. Таблица 12 показывает поведение контактов сравнения в режиме PWM.

The user will have to configure the output compare pins as outputs in order to enable the PWM output. As with basic timer operation, when the PWM (compare) pins are connected to the compare logic, their logic state remains unchanged. However, since the bit FCO is used to hold the halt value, only a compare event can change the state of the pin.

Пользователь будет должен настроить контакты сравнения как выходы для того, чтобы активизировать выход PWM. Как и в базовом режиме работы таймера, когда контакты PWM (сравнения) подключены к логике сравнения, их логические состояния не изменяются. Однако, так как бит FCO содержит значение остановки, только событие сравнения может изменить состояние этого контакта.

Figure 32: Asymmetrical PWM, downcounting

Рис. 32: Асимметричный режим PWM, обратный счет

Figure 33: Symmetrical PWM

Рис.22: Симметричный режим PWM

* Compare Value – величина сравнения

Timer Value – значение таймера

Non-inverted – не инвертированный