- •3) Частотно-временной анализ

- •4) Нелинейная обработка

- •5) Адаптивная фильтрация

- •6) Многоскоростная обработка

- •1.3. Реализация алгоритмов цос

- •1.4. Особенности цос

- •17. Особенности архитектуры цпос. Основные свойства цпос (л3: р.2.1, 2.2)

- •2. Особенности архитектуры цпос

- •2.1. Основные свойства цпос

- •2.2. Архитектура цпос

- •18. Цпос с фиксированной и плавающей точкой. Основные типы цпос (л3: р.2.3, 2.4)

- •2.3. Цпос с фиксированной и плавающей точкой

- •2.4. Основные типы цпос

- •1) Стандартные цпос (Conventional dsp).

- •2) Улучшенные стандартные цпос (Enhanced-Conventional dsp).

- •3) Процессоры с архитектурой vliw

- •4) Суперскалярные процессоры

- •5) Гибридные процессоры

- •19. Микропроцессоры семейства adsp21xx (л3: р.3.1)

- •3.1. Микропроцессоры семейства adsp21xx

19. Микропроцессоры семейства adsp21xx (л3: р.3.1)

3.1. Микропроцессоры семейства adsp21xx

Семейство ADSP21xx – это набор 16-разрядных сигнальных микропроцес-

соров с общей базовой архитектурой, которая оптимизирована для выполнения

алгоритмов ЦОС и ряда других приложений, требующих высокопроизводи-

тельных вычислений с ФТ.

Сейчас в это семейство входит 15 микропроцессоров, которые отличаются

друг от друга, в основном, расположенными на кристалле периферийными уст-

ройствами. Все МП этого семейства обладают высокой производительностью и

имеют низкую стоимость. Кроме того, для них имеются хорошо развитые аппа-

ратные и программные средства разработки прикладных систем. Все это обес-

печило популярность и хорошую конкурентоспособность этих МП.

Микропроцессоры семейства ADSP21xx имеют модифицированную гар-

вардскую архитектуру, в рамках которой предусмотрена возможность доступа

в память команд при ее физическом разделении с памятью данных. Высокая

производительность достигается за счет многофункциональной и гибкой сис-

темы команд, аппаратной реализации операций, типичных для ЦОС, высокой

степени параллелизма процессов.

Обобщенная структурная схема сигнального микропроцессора семейства

ADSP21xx показана на рисунке 9.

В микропроцессоре имеется три независимых функциональных блока:

АЛУ, умножитель с накоплением (MAC) и устройство барабанного сдвига. Ка-

ждый из них работает с 16-разрядными данными и обеспечивает аппаратную

поддержку вычислений. МП содержит также генератор адресов команд и два

генератора адресов данных, которые организуют адресацию к данным и коман-

дам, расположенным во внутренней и во внешней памяти. Параллельная работа

генераторов дает возможность выбирать за один такт из памяти команду и два

операнда, что сокращает время выполнения команды. Последовательные порты

обеспечивают интерфейс с большинством стандартных последовательных уст-

ройств и с аппаратными средствами сжатия и восстановления данных, исполь-

зующих A- и μ -законы компандирования. Что касается порта интерфейса с

хост-процессором, то он дает возможность взаимодействовать с любым хост-

процессором системы без всяких дополнительных устройств.

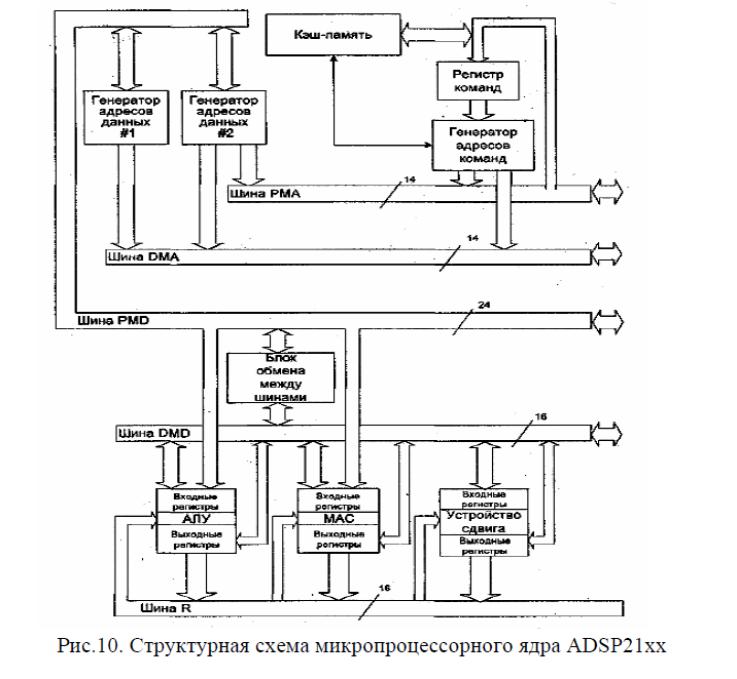

Общее для семейства микропроцессорное ядро представлено на рисунке 10.

АЛУ осуществляет выполнение стандартных арифметических и логиче-

ских операций, включая деление. Устройство MAC выполняет операции умно-

жения со сложением/вычитанием за один такт. Устройство сдвига осуществля-

ет арифметические и логические сдвиги операндов, нормализацию, возведение

в степень. Шина внутренних результатов позволяет блокам обмениваться

результатами выполнения операций.

Внутренние функциональные блоки связаны между собой пятью шинами:

шина адресов памяти данных (DMA), шина адресов памяти команд (PMA), ши-

на данных памяти данных (DMD), шина данных памяти команд (PMD). Эти

шины имеют мультиплексированный внешний интерфейс в виде шины адреса и

шины данных. Устройства связаны, как уже говорилось, шиной внутренних ре-

зультатов (R).

По системе команд все процессоры этого семейства совместимы снизу

вверх, некоторые представители имеют дополнительные и расширенные ко-

манды.

Каждая команда выполняется за один такт. Многофункциональные коман-

ды МП объединяют несколько пересылок данных с арифметико-логической

обработкой.

Все устройства в МП 16-разрядные, работают только с данными в формате

с ФТ. Числа при этом представляются либо как беззнаковые, либо в дополни-

тельном коде. Логические операции выполняются над битовыми строками. Со-

вершенствование семейства идет в направлении повышения тактовой частоты,

расширения коммуникационных возможностей, уменьшения энергопотребле-

ния.

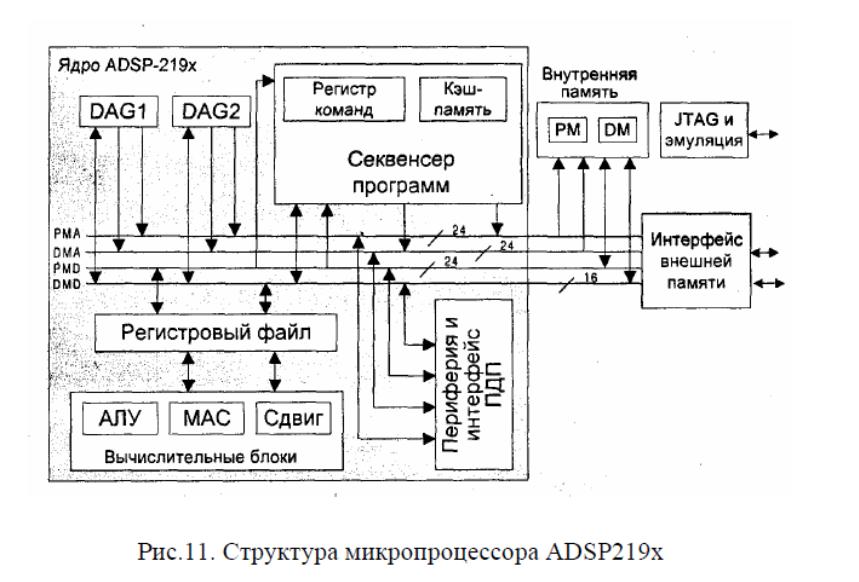

Новый МП семейства ADSP219x имеет модифицированное ядро. В буду-

щем на основе этого ядра AD планирует создавать процессоры под конкретные

требования, а для приложений, требующих высокой производительности,

предполагается строить процессоры с несколькими ядрами на одном кристалле.

По сравнению с процессорами семейства ADSP218x, имеющими 14-

разрядную шину адреса, в семействе ADSP219x применяется 24-разрядная ши-

на адреса. Это позволяет осуществлять прямую адресацию в пределах 64 Кслов

или страничную адресацию в пределах 16 Мслов. Генератор адреса поддержи-

вает как все ранее использованные, так и пять новых режимов адресации. МП

семейства ADSP219x программно совместим с предыдущими, обладает гораздо

большей производительностью (300 MIPS) и меньшим энергопотреблением (0.4

мВт/MIPS). Его структура показана на рисунке 11.

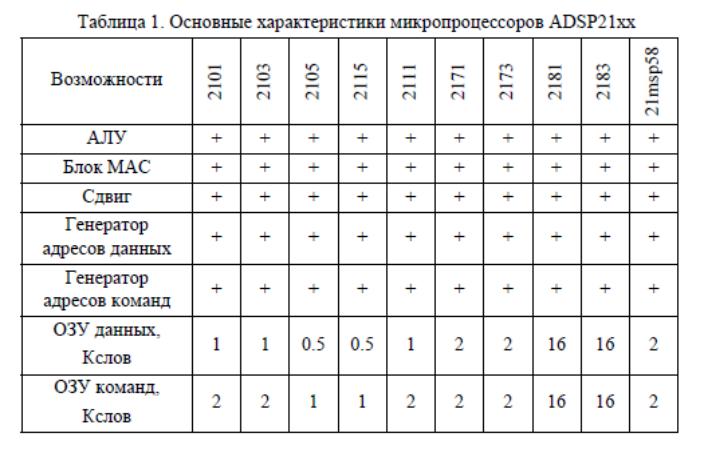

Основные характеристики некоторых сигнальных микропроцессоров

ADSP21xx приведены в таблице 1.