- •3) Частотно-временной анализ

- •4) Нелинейная обработка

- •5) Адаптивная фильтрация

- •6) Многоскоростная обработка

- •1.3. Реализация алгоритмов цос

- •1.4. Особенности цос

- •17. Особенности архитектуры цпос. Основные свойства цпос (л3: р.2.1, 2.2)

- •2. Особенности архитектуры цпос

- •2.1. Основные свойства цпос

- •2.2. Архитектура цпос

- •18. Цпос с фиксированной и плавающей точкой. Основные типы цпос (л3: р.2.3, 2.4)

- •2.3. Цпос с фиксированной и плавающей точкой

- •2.4. Основные типы цпос

- •1) Стандартные цпос (Conventional dsp).

- •2) Улучшенные стандартные цпос (Enhanced-Conventional dsp).

- •3) Процессоры с архитектурой vliw

- •4) Суперскалярные процессоры

- •5) Гибридные процессоры

- •19. Микропроцессоры семейства adsp21xx (л3: р.3.1)

- •3.1. Микропроцессоры семейства adsp21xx

1.4. Особенности цос

В общем, задачи цифровой обработки сигналов довольно специфические и

непростые. Они имеют целый ряд особенностей, из-за которых к элементной

базе ЦОС предъявляются весьма жесткие требования. К ним относятся:

1) Поточный характер обработки в реальном времени больших объемов

данных, которые поступают порой с огромной скоростью, требует высокой

производительности процессора.

2) Динамический диапазон входных/выходных сигналов может составлять

100 дБ. Следовательно, ЦПОС должен обеспечивать обработку данных боль-

шой разрядности, так как одному биту соответствует примерно шесть децибел.

3) Большое количество операций сложения, умножения и логических опе-

раций, операторов свертки, рекурсии, ДПФ и БПФ. Элементная база должна

быть ориентирована на их быстрое выполнение.

4) Необходимость обеспечения гибкости и перестройки цифровых систем

обработки сигналов.

5) Параллелизм алгоритмов, т.е. для каждого набора входных данных вы-

полняются совмещаемые по времени действия.

6) Регулярность алгоритмов, т.е. повторяемость отдельных операций.

Типичный пример – операция “бабочка” в БПФ.

Все эти особенности непосредственно определяют то, каким способом

должен быть реализован алгоритм ЦОС, какова должна быть ее элементная ба-

за, какие архитектуру и параметры должен иметь ЦПОС и т.п.

Короче говоря, от основных особенностей цифровой обработки сигналов

зависят и особенности сигнальных микропроцессоров.

17. Особенности архитектуры цпос. Основные свойства цпос (л3: р.2.1, 2.2)

2. Особенности архитектуры цпос

В предыдущем разделе рассмотрены особенности и проблемы цифровой

обработки сигналов, ее направления и задачи. От них в первую очередь зависят

требования, предъявляемые к процессорам, осуществляющим эту обработку, их

свойства, параметры.

2.1. Основные свойства цпос

Сигнальный процессор должен обладать следующими свойствами:

1) Быстрое выполнение типовых операций ЦОС.

2) Аппаратная реализация комплексной операции умножения с накоплени-

ем, что позволяет осуществлять операцию умножения за один такт.

3) Применение арифметики с фиксированной и с плавающей точкой с раз-

личной разрядностью.

4) Параллельное выполнение отдельных частей алгоритма, что достигается

аппаратной реализацией ряда типовых алгоритмов.

5) Большая внутрикристальная память данных и память программ.

6) Разнообразие режимов адресации применительно к различным задачам.

7) Обработка в реальном времени данных, поступающих с высокой скоро-

стью.

8) Наличие внутрикристальной периферии.

9) Малое время обращения к элементам внешней периферии.

Все эти особенности необходимо учитывать при разработке архитектуры

сигнального процессора.

2.2. Архитектура цпос

Под словом «архитектура» обычно понимается то, какие узлы входят в со-

став устройства, каковы их принцип действия и конфигурация, как они соеди-

нены и как взаимодействуют друг с другом. В это понятие входят также изло-

жение возможностей программирования, форматов данных, системы команд и т.д.

В общем, термин «архитектура» относится и к аппаратным средствам, и к

программному обеспечению. Главная особенность архитектуры любого сиг-

нального процессора заключается в том, что архитектура эта в первую очередь

определяется алгоритмом ЦОС, реализуемом в этом сигнальном процессоре.

Этот алгоритм, в свою очередь, зависит от того, какую функцию должен

выполнять процессор. Поэтому ЦПОС иногда еще называют проблемно-

ориентированными процессорами.

Короче говоря, для каждой задачи нужен свой алгоритм, своя архитектура

и, соответственно, свой процессор. Конечно, это неудобно, но именно за счет

узкой специализации сигнальные процессоры способны эффективно выполнять

поставленные задачи. Правда, разработчики стараются все же хоть в какой-то

мере унифицировать сигнальные процессоры.

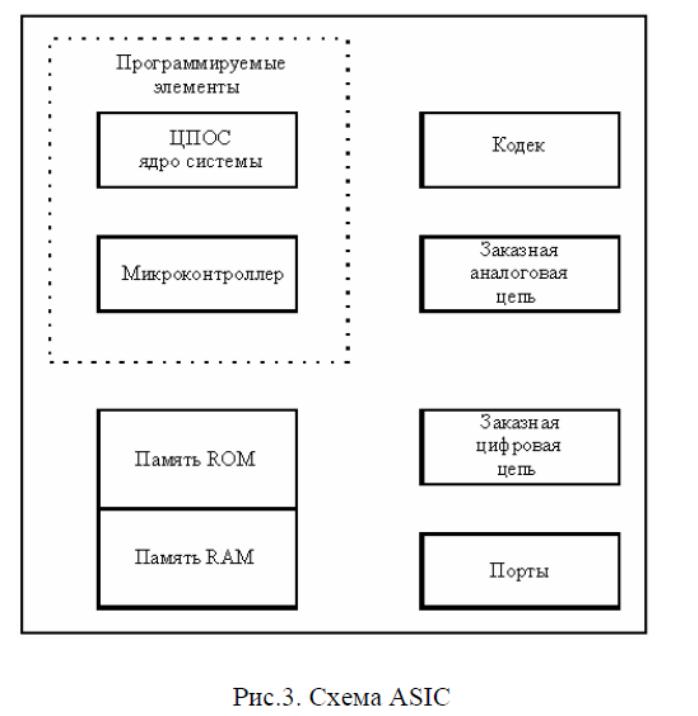

Типичный пример такой унификации – создание прикладных специализи-

рованных схем ASIC (Application-Specific Integrated Circuits). Их еще называют

проблемно-ориентированными ИС. Схема ASIC приведена на рис.3.

Она включает в себя ядро ЦПОС как элемент общего кристалла, порты, за-

казные цепи, кодеки, память, микроконтроллеры.

Такие ИС в одном кристалле содержат собственно ЦПОС и пользователь-

скую схему. Благодаря этому они подобно заказным схемам имеют высокую производительность и малые габариты, и при этом у них есть возможность про-

граммирования, инструментальные средства и библиотеки программ, как у

ЦПОС.

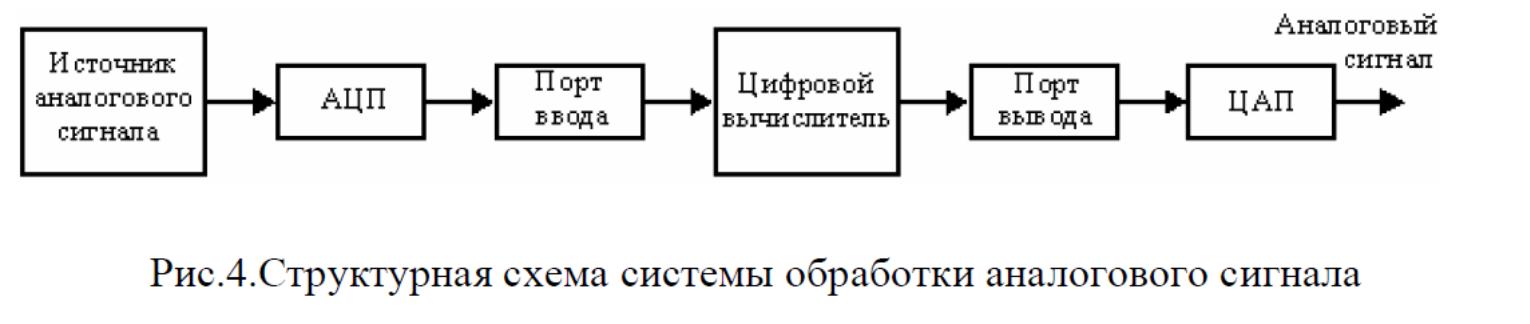

Общая структурная схема системы обработки аналогового сигнала приве-

дена на рисунке 4.

АЦП преобразует аналоговый сигнал в цифровой код, ЦАП осуществляет

обратное преобразование.

Иногда ЦАП не нужен. Нет, например, необходимости в восстановлении

аналогового сигнала в устройствах, где по результатам обработки входного

сигнала выносится какое-либо решение.

Порты ввода/вывода осуществляют ввод цифрового сигнала в вычислитель

и, если это необходимо, вывод результатов.

Вычислитель может быть реализован аппаратным способом и программ-

ным методом. Но во всех сигнальных процессорах для обеспечения высокого

быстродействия реализуется аппаратная поддержка базовых операций алгорит-

мов ЦОС.

Это еще одна характерная особенность архитектуры ЦПОС. Основной опе-

рацией в алгоритмах цифровой обработки сигналов является операция умноже-

ния с накоплением MAC

C=A*B+C.

Для того чтобы работать с высокой производительностью, эту операцию

процессор должен выполнять за один такт. Поэтому для сигнальных процессо-

ров характерно наличие аппаратного умножителя, который осуществляет ум-

ножение двух чисел за один такт.

Кроме этого в ЦПОС реализуется аппаратная поддержка операций сдвига,

программных циклов, кольцевых буферов, обработки прерываний.

Элементная база ЦОС включает непрограммируемые и программируемые

элементы. От нее сильно зависит скорость, с которой процессор решает задачу.

Но в любом случае, сигнальный процессор – это вычислительная система.

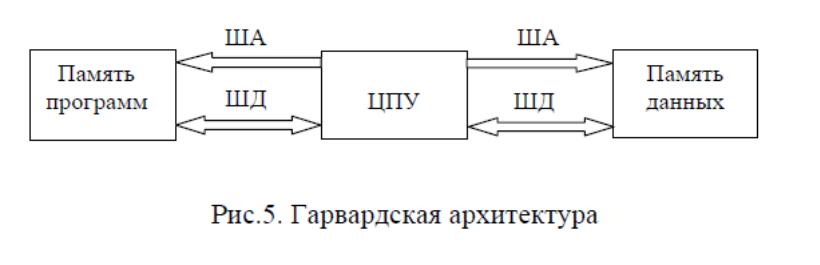

Существует два типа архитектур вычислительных систем: архитектура фон

Неймана и гарвардская архитектура.

В ЦПОС применяется гарвардская архитектура вычислительной системы.

Она приведена на рисунке 5.

В отличие от «фон-неймановской» архитектуры, в гарвардской для хране-

ния программы и данных используются разные устройства памяти.

Соответственно, в такой системе есть два комплекта шин:

• * шина адреса памяти программ (ШАПП),

• * шина данных памяти программ для работы с памятью программ

(ШДПП),

• ** шина адреса памяти данных (ШАПД),

• ** шина данных памяти данных для работы с памятью данных (ШДПД).

Следовательно, в системе, построенной по гарвардской архитектуре, мож-

но одновременно обращаться к различным элементам памяти – одновременно

выбирать команду из ПП по ШДПП и сомножитель из ПД по ШДПД.

В таком случае для выполнения операции MAC – базовой операцией ЦОС

– требуется два цикла работы процессора вместо трех-четырех. Реально время

выполнения операции MAC почти всегда удается свести к одному циклу за счет

различных дополнительных мер.

Надо заметить, что в сигнальных процессорах данные могут храниться и в

памяти программ, поэтому в данном случае правильнее говорить о модифици-

рованной гарвардской структуре.

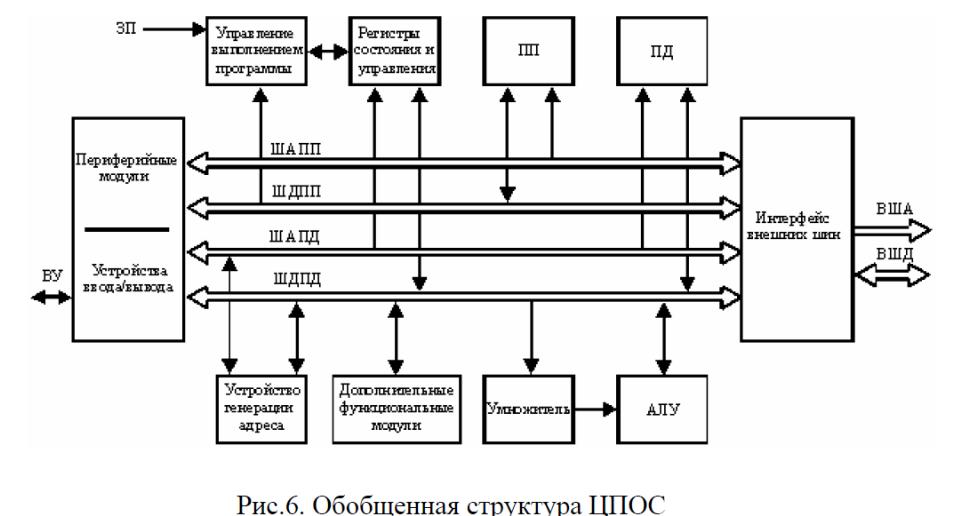

Обобщенная структура ЦПОС представлена на рисунке 6.

Информация хранится в памяти данных и в памяти программ.

ПП и ПД при помощи шин связаны с другими устройствами. Шина адреса

ПП предназначена для передачи адресов ячеек памяти программ. Шина данных

ПП служит для передачи команд, хранимых в ПП, и данных в случае их хране-

ния в ПП. Шины адреса и данных ПД применяются для передачи адреса и дан-

ных ПД.

Разрядность ЩДПД сильно влияет на производительность процессора.

Во всех ЦПОС имеется внутренняя (внутрикристальная) память. Ее часто

не хватает, и тогда сигнальный процессор использует внешнюю память посред-

ством интерфейса внешних шин и самих внешних шин адреса (ВША) и данных

(ВШД).

ВША и ВШД могут использоваться и при обращении к каким-либо другим

внешним устройствам, а не только к памяти. Устройство управления выполне-

нием программы в соответствии с командами из ПП выдает сигналы управле-

ния работой всех узлов ЦПОС.

В регистры состояния и управления записывается информация, управ-

ляющая работой всего процессора. На устройство управление от внешних уст-

ройств ВУ поступают запросы на прерывание основной программы работы для

согласования скорости работы процессора и этих внешних устройств.

АЛУ, умножитель и дополнительные функциональные узлы осуществляют

непосредственную обработку информации.

От них главным образом и зависит производительность всей системы в це-

лом.

Устройство генерации адреса (УГА) формирует адреса данных, извлекае-

мых из ПД. Для одновременной выборки нескольких операндов необходимо

формировать несколько адресов, следовательно, необходимо иметь несколько

УГА.

Как уже говорилось, характерной особенностью архитектуры ЦПОС явля-

ется аппаратная реализация функций, которые в универсальных МП выполня-

ются программным способом.

Для выполнения таких операций и предназначены дополнительные функ-

циональные узлы и различные специализированные модули. Они работают па-

раллельно АЛУ и значительно повышают быстродействие ЦПОС.

К ним можно отнести умножитель, сдвигатели, различные устройства для

выполнения арифметических и логических операций. Важную роль играют мо-

дули для аппаратной реализации циклов. Следует также отметить, что для по-

вышения производительности процессор может иметь не одно АЛУ, а несколь-

ко.