- •ВАРИАЦИИ DSP56300

- •ВАРИАЦИИ DSP56300

- •ВАРИАЦИИ DSP56300

- •ВАРИАЦИИ DSP56300

- •ВАРИАЦИИ DSP56300

- •ОСОБЕННОСТИ DSP56307

- •ОСОБЕННОСТИ DSP56307

- •ЦЕЛЕВЫЕ ПРИЛОЖЕНИЯ DSP56307

- •ОБЗОР DSP56307

- •Redcap2 - 5665_

- •Redcap2 (продолжение)

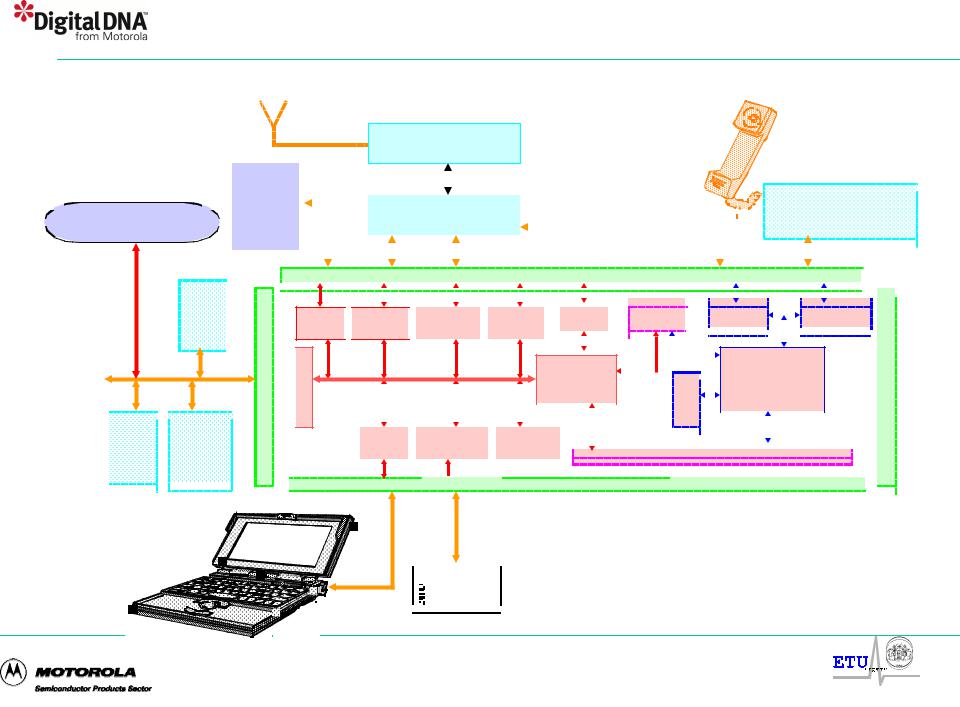

- •Redcap в беспроводной телефонной трубке

- •Семейство M•CORE

- •Архитектура M•CORE

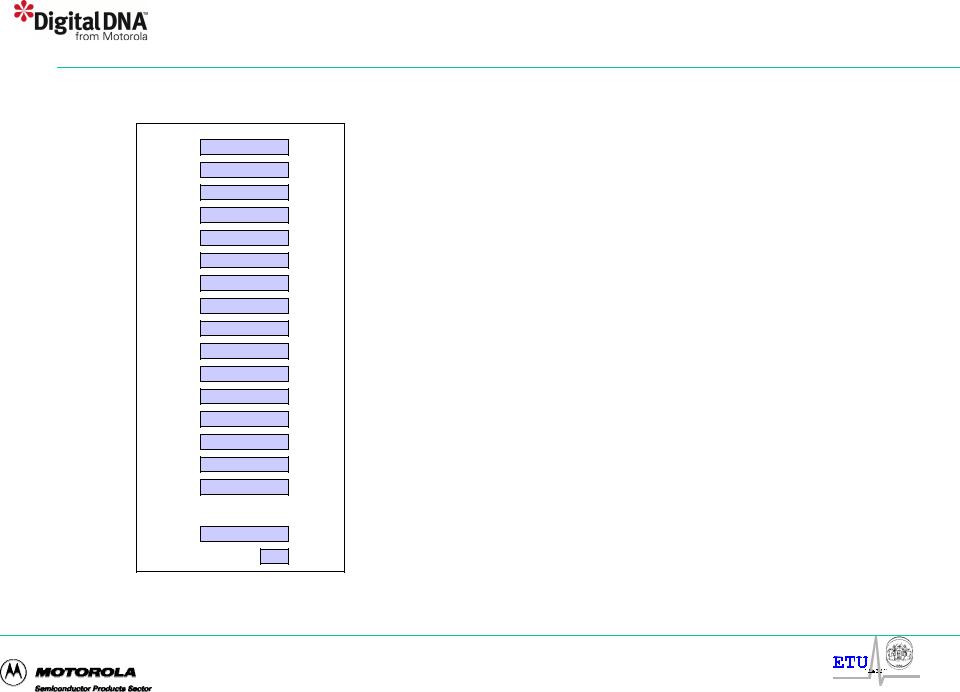

- •Программная модель пользователя M•CORE

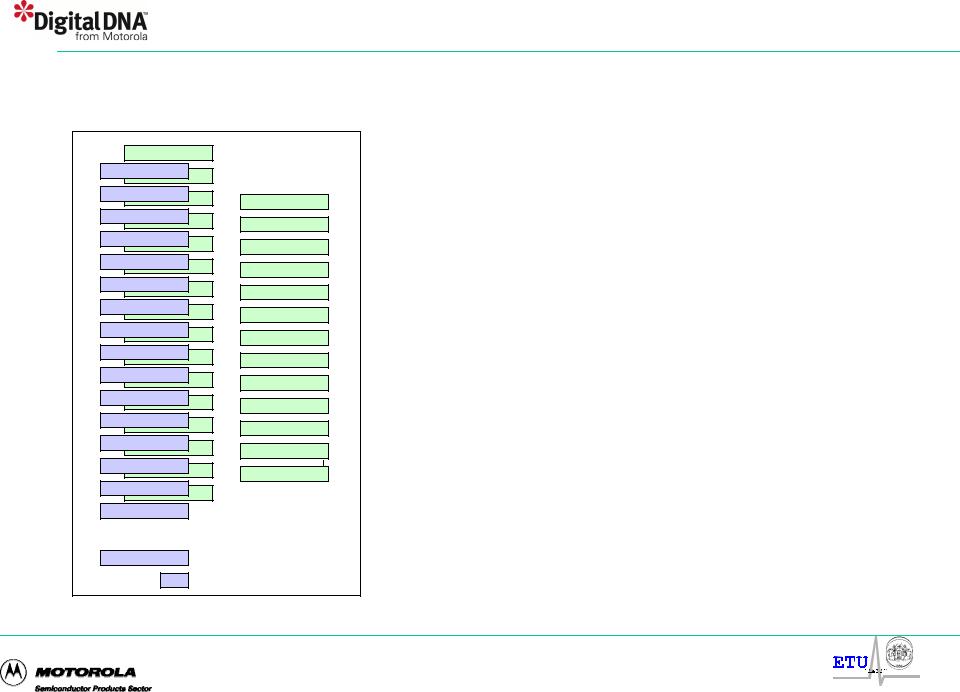

- •Программная модель супервизора M•CORE

- •Режимы пониженного энергопотребления M•CORE

- •Семейства M•CORE

- •Семейство DSP56600

- •Особенности ядра DSP56600

- •Энергопотребление 56652, 1.8V

- •ПЕРИФЕРИЯ REDCAP

- •Соединение периферии Redcap

- •Интерфейс MCU-DSP (MDI)

- •MDI: разделяемая память

- •MDI: поведение в режимах пониженного энергопотребления

- •QSPI: конфигурация каналов

- •Интерфейс внешней памяти M•CORE (EIM)

- •Порт клавиатуры M•CORE (KPP)

- •Сторожевой таймер M•CORE

- •Сторожевой таймер: конфигурация

- •M•CORE Таймер периодических прерываний (PIT)

- •Импульсный ввод/вывод M•CORE

- •Возможности DSP и контроллера

- •Функциональная схема DSP56L811

- •Функциональная схема DSP56824

- •Сравнение DSP56L811 & DSP56824

- •Характеристики 56800

- •Параллельная пересылка DSP56800

- •Особенности DSP56800 MCU

- •Низкое энергопотребление DSP56800

- •Особенности и достоинства DSP56800

- •Особенности и достоинства DSP56800

- •Архитектура SC140

- •Основные секции SC140

- •Особенности архитектуры Star Core

- •Блоки ядра SC140

- •Структура АЛУ

- •Регистровый файл АЛУ

- •Поддерживаемые форматы данных

- •Структура блока генерации адресов

- •Регистровый файл блока генерации адресов

- •Регистры поддержки аппаратных циклов

- •Конвейер выполнения команд

- •Описание этапов конвейера

- •Особенности архитектуры ядра SC140

- •Особенности архитектуры ядра SC140. Продолжение.

- •Особенности архитектуры ядра SC140. Окончание

- •Блоковая диаграмма типичного SC140 устройства

- •СРЕДСТВА РАЗРАБОТКИ DSP

- •Структурная схема EVM

- •Стратегия средств разработки

- •Средства разработки DSP

- •Аппаратные средства разработки

- •Средства программной разработки

- •DSP56300 Family Feature List

- •DSP56600 Family Feature List

- •DSP56000 Family Feature List

- •DSP56800 Family Feature List

Redcap2 - 5665_

•Разработано с iDEN для поддержки телефонии iDEN/GSM

•План

–CDR2 планируется на август 1998

•Добавлена новая периферия DSP

–ускоритель Viterbi

–блок GSM

–один канал ПДП

•Добавлена новая периферия M•CORE

–второй UART

–второй QSPI

•Больший размер ОЗУ DSP

–40Kслов ОЗУ программ DSP (56651 имеет 24K ОЗУ+24K ПЗУ)

–31Kслов DSP ОЗУ данных (56651 имеет 16K ОЗУ+18K ПЗУ)

Москва, 10-13 мая 2000г.

Redcap2 (продолжение)

•Модификации периферии:

–Таймер протокола

•таблица событий увеличена от 80 до 128 входов

•увеличено количество выводов TOUT от 8 до 16

•триггеры для второго QSPI

–MDI: больший размер разделяемой памяти (2K слов вместо 1K слов)

–SAP: более гибкая синхронизация BRM

–BBP: модификации для связи с CSS Ics

–QSPI: очередь ОЗУ увеличена от 64 до 128 входов

•Режим видимости шин данных DSP для расширенной отладки

•Больше выводов и больший размер корпуса

–236 выводов (Redcap имеет 171)

–17x17 мм 256-выводной PBGA

Москва, 10-13 мая 2000г.

Redcap в беспроводной телефонной трубке

PA

Roam

Roam  InUse

InUse NoSvc

NoSvc

18005551212

18005551212

LoBatt Rchg

SRAM

FLASH EEPROM

1 2 |

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

4 5 |

6 |

|

|

|

|

|

|

|

|

|

|

Аудио |

|

|

|

|

RF |

|

|

|

|

||||

7 8 |

9 |

|

|

|

|

|

|

|

|

|||

* 0 |

# |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ТРАНСЛЯТОРЫ УРОВНЯ I/O

Клав.

Внеш. Пам. I/F

Внеш. Пам. I/F

ТРАНСЛЯТОРЫ УРОВНЯ I/O

|

|

|

|

|

|

|

|

|

|

|

Раздел. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Baseband |

|

|

SerialAudio |

|||||

GPIO |

|

Таймер |

|

QSPI |

|

Память |

память |

|

|

||||||||||

|

протокола |

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

m•core |

|

Память |

|

|

DSP56600 |

|||||

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

UART |

|

Smartcard |

|

Таймеры |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

ЛОГИКА ОТЛАДКИ |

||||||||||||

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

ТРАНСЛЯТОРЫ УРОВНЯ I/O

ТРАНСЛЯТОРЫ УРОВНЯ I/O

ТРАНСЛЯТОРЫ УРОВНЯ I/O

SmartCard |

Москва, 10-13 мая 2000г.

Семейство M•CORE

•Оптимизированное для загрузки/восстановления встроенное микро-RISC ядро

•Производительность 32-битного класса при 16-битной памяти

•Оптимизировано для портативных приложений, требующих высокой плотности кода и низкого энергопотребления

•Объявленные разработки:

–M200 Evaluation Chip

–MCC2001 - Powerstrike 1, для рынка маломощных портативных приложений: переносные системы, GPS, цифровая камера, “персональный организатор”

–Redcap: производство и разработка ICs

Москва, 10-13 мая 2000г.

Архитектура M•CORE

Особенности архитектуры:

• 32-битные шины данных

•16-битные инструкции фиксированной

длины

• 16-входовый регистровый файл общего

назначения

• Второй “альтернативный” регистровый

файл

• Режимы пользователя и супервизора

• 5 рабочих регистров, доступных в режиме

супервизора

• Динамическое управление

энергопотреблением

• 3 режима низкого энергопотребления

• 2 уровня векторных прерываний

• Интерфейс аппаратного ускорителя

• >10% неиспользуемого пространства кода

операций

R0’ (sp’)

R0 (sp) |

|

|

R1 |

PSR |

|

R2 |

||

VBR |

||

R3 |

||

EPSR |

||

R4 |

||

FPSR |

||

R5 |

||

EPC |

||

R6 |

||

FPC |

||

R7 |

||

SS0 |

||

R8 |

||

SS1 |

||

R9 |

||

SS2 |

||

R10 |

||

SS3 |

||

R11 |

||

SS4 |

||

R12 |

||

GCR |

||

R13 |

||

GSR |

||

R14 |

||

|

||

R15 (lr) |

|

PC

C

ПРОГРАММНАЯ МОДЕЛЬ ПОЛЬЗОВАТЕЛЯ

ПРОГРАММНАЯ МОДЕЛЬ СУПЕРВИЗОРА

Москва, 10-13 мая 2000г.

Программная модель пользователя M•CORE

R0 (sp)

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13

R14

R15 (lr)

PC

C

•16 32-битных регистров общего назначения

–R0 используется как указатель стека

–R15 используется как регистр связи

•Программный счетчик

•Одиночный бит условия/Перенос (C)

–арифметические/логические операции >32 bits

–проверка условий

Москва, 10-13 мая 2000г.

Программная модель супервизора M•CORE

R0’ (sp’)

R0 (sp) |

|

|

R1 |

PSR |

|

R2 |

||

VBR |

||

R3 |

||

EPSR |

||

R4 |

||

FPSR |

||

R5 |

||

EPC |

||

R6 |

||

FPC |

||

R7 |

||

SS0 |

||

R8 |

||

SS1 |

||

R9 |

||

SS2 |

||

R10 |

||

SS3 |

||

R11 |

||

SS4 |

||

R12 |

||

GCR |

||

R13 |

||

GSR |

||

R14 |

||

|

||

R15 (lr) |

|

PC

C

•Все регистры пользователя плюс:

–16-входовый “альтернативный” регистровый файл

–Регистровый файл супервизора

•PSR - биты управления/состояния:

–режим супервизора

–разрешение исключений

–разрешение прерываний (INT)

–разрешение быстрых прерываний (FINT)

–управление прерываниями

–разрешение альтернативного регистрового файла

–номер вектора исключения

–код условия/бит переноса

•VBR - регистр векторной базы

•SS0-4 - регистры общего назначения

•GCR, GSR - глобальное управление и состояние

•EPSR/EPC - восстановление PSR/PC после исключений и нормальных прерываний

•FPSR/FPC - восстановление PSR/PC при быстрых прерываниях

Москва, 10-13 мая 2000г.

Режимы пониженного энергопотребления M•CORE

• режимы пониженного энергопотребления вводятся инструкциями “wait”, “doze”, и “stop”.

–Синхронизация в ядре запрещается

–Периферия может функционировать (в зависимости от устройства)

Режим |

Поведение |

Поведение |

Выход из режима |

|

ядра |

периферии |

пониженного |

|

|

|

энергопотребления |

|

|

|

|

Нормальный |

Работает |

Работает |

|

|

|

|

|

Wait |

Остановлено |

Работает |

Прерывание |

|

|

|

|

Doze |

Остановлено |

Определяется |

Прерывание |

периферией |

|||

|

|

|

|

Stop |

Остановлено |

Большинство |

Прерывание |

остановлено |

|||

|

|

|

|

|

|

|

|

Москва, 10-13 мая 2000г.

Семейства M•CORE

M700 - 32-битные данные, 32-битные инструкции |

|

|

|

M700 32-битн. |

||

|

|

|

|

|

|

расширения |

M200-M600 - 32-битные данные, |

M500 - Сверх- |

|

|

|

M600 |

|

|

|

Суперскалярный |

||||

16-битные инструкции |

конвейеризованный |

|

M•CORE |

|||

M•CORE |

|

|

• Две инструкции за цикл |

|||

|

|

|

|

|

||

|

|

• Одна инструкция за цикл |

• DC-300 MГц (450 MIPS*) |

|||

|

|

• DC-200 MГц (200 MIPS*) |

• Планируется |

|||

|

Двойное ядро |

• Кэш/MMU |

|

M310 |

|

|

|

• 0.22µ Leff (CDR3) |

• Быстрое умножение |

||||

|

M•CORE + DSP |

|||||

|

|

|

M•CORE-M |

• Кэш / MMU |

||

|

|

M300 |

|

|||

|

|

|

|

|

• DC- 80 MГц (65+ MIPS*) |

|

|

M330 |

M•CORE-M |

|

|

|

• 0.22µ Leff (CDR3) |

M200 |

M•CORE-FP |

|

|

|

|

|

|

• Быстрое умножение |

|

|

|

M370 |

|

M•CORE 1.5 |

|

|

|

M350 |

||

• Одиночная точность с |

• DC- 80 MГц (65+ MIPS*) |

|

|

|||

|

|

M•CORE-DSPlite |

M•CORE/DSP |

|||

• DC-50 MГц (40 MIPS*) |

плавающей запятой |

• 0.22µ Leff (CDR3) |

|

Одиночное ядро |

||

• DC- 80 MГц (65 MIPS*) |

|

|

|

|

|

|

• 1.8-3.6 Вольт |

• 1.8 В, 0.22µ Leff (CDR3) |

M210 |

|

• Light-duty DSP |

||

• 0.36µ Leff |

• 4Q98 |

|

• DC-80 MГц (65MIPS*) |

|||

• 2.2 мм2 площадь ядра |

|

M•CORE-1.5 |

|

• 1.8 Вольт |

|

|

• 0.41 мВт на MГц |

|

w/кэш |

|

• 0.22µ Leff (CDR3) |

||

• Существует |

|

|

|

• Планируется |

|

|

|

|

|

|

|

||

M100 - 16-битные данные, 16-битные инструкции |

M100 M•CORE16 |

|

||||

16-битные шины данных

• Низкая стоимость и производительность

• Планируется

Москва, 10-13 мая 2000г.

Семейство DSP56600

•Эволюция семейства DSP56000:

–“1-Х” ядро DSP56300:

•24-битные слова программ и данных

•24-битная адресация

–ядро ultralite DSP56600:

•24-битные слова программ, 16-битные слова данных

•16-битная адресация

•Представители семейства DSP56600:

–56602 - отдельное ПЗУ

–56603 - отдельное ОЗУ

–56651 - Redcap-разработка

–56652 - Redcap-производство

Москва, 10-13 мая 2000г.