- •ВАРИАЦИИ DSP56300

- •ВАРИАЦИИ DSP56300

- •ВАРИАЦИИ DSP56300

- •ВАРИАЦИИ DSP56300

- •ВАРИАЦИИ DSP56300

- •ОСОБЕННОСТИ DSP56307

- •ОСОБЕННОСТИ DSP56307

- •ЦЕЛЕВЫЕ ПРИЛОЖЕНИЯ DSP56307

- •ОБЗОР DSP56307

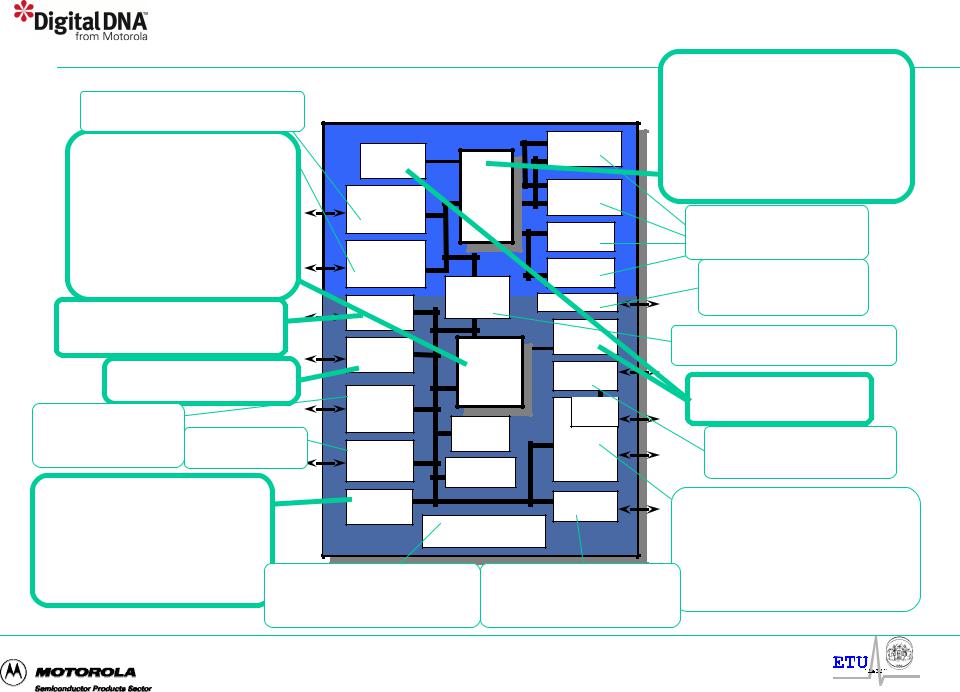

- •Redcap2 - 5665_

- •Redcap2 (продолжение)

- •Redcap в беспроводной телефонной трубке

- •Семейство M•CORE

- •Архитектура M•CORE

- •Программная модель пользователя M•CORE

- •Программная модель супервизора M•CORE

- •Режимы пониженного энергопотребления M•CORE

- •Семейства M•CORE

- •Семейство DSP56600

- •Особенности ядра DSP56600

- •Энергопотребление 56652, 1.8V

- •ПЕРИФЕРИЯ REDCAP

- •Соединение периферии Redcap

- •Интерфейс MCU-DSP (MDI)

- •MDI: разделяемая память

- •MDI: поведение в режимах пониженного энергопотребления

- •QSPI: конфигурация каналов

- •Интерфейс внешней памяти M•CORE (EIM)

- •Порт клавиатуры M•CORE (KPP)

- •Сторожевой таймер M•CORE

- •Сторожевой таймер: конфигурация

- •M•CORE Таймер периодических прерываний (PIT)

- •Импульсный ввод/вывод M•CORE

- •Возможности DSP и контроллера

- •Функциональная схема DSP56L811

- •Функциональная схема DSP56824

- •Сравнение DSP56L811 & DSP56824

- •Характеристики 56800

- •Параллельная пересылка DSP56800

- •Особенности DSP56800 MCU

- •Низкое энергопотребление DSP56800

- •Особенности и достоинства DSP56800

- •Особенности и достоинства DSP56800

- •Архитектура SC140

- •Основные секции SC140

- •Особенности архитектуры Star Core

- •Блоки ядра SC140

- •Структура АЛУ

- •Регистровый файл АЛУ

- •Поддерживаемые форматы данных

- •Структура блока генерации адресов

- •Регистровый файл блока генерации адресов

- •Регистры поддержки аппаратных циклов

- •Конвейер выполнения команд

- •Описание этапов конвейера

- •Особенности архитектуры ядра SC140

- •Особенности архитектуры ядра SC140. Продолжение.

- •Особенности архитектуры ядра SC140. Окончание

- •Блоковая диаграмма типичного SC140 устройства

- •СРЕДСТВА РАЗРАБОТКИ DSP

- •Структурная схема EVM

- •Стратегия средств разработки

- •Средства разработки DSP

- •Аппаратные средства разработки

- •Средства программной разработки

- •DSP56300 Family Feature List

- •DSP56600 Family Feature List

- •DSP56000 Family Feature List

- •DSP56800 Family Feature List

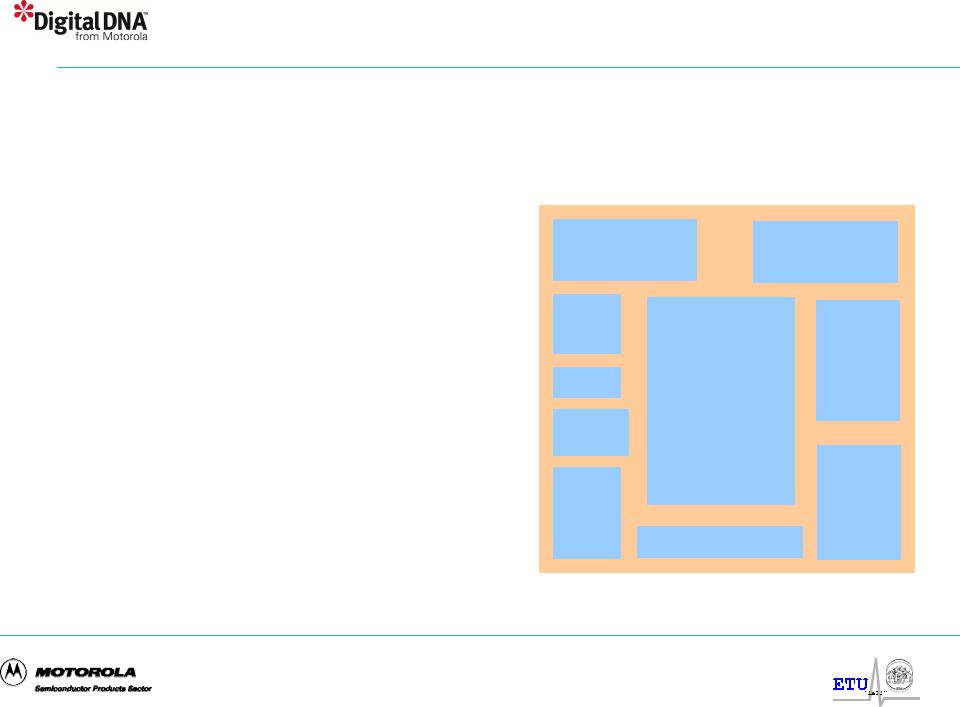

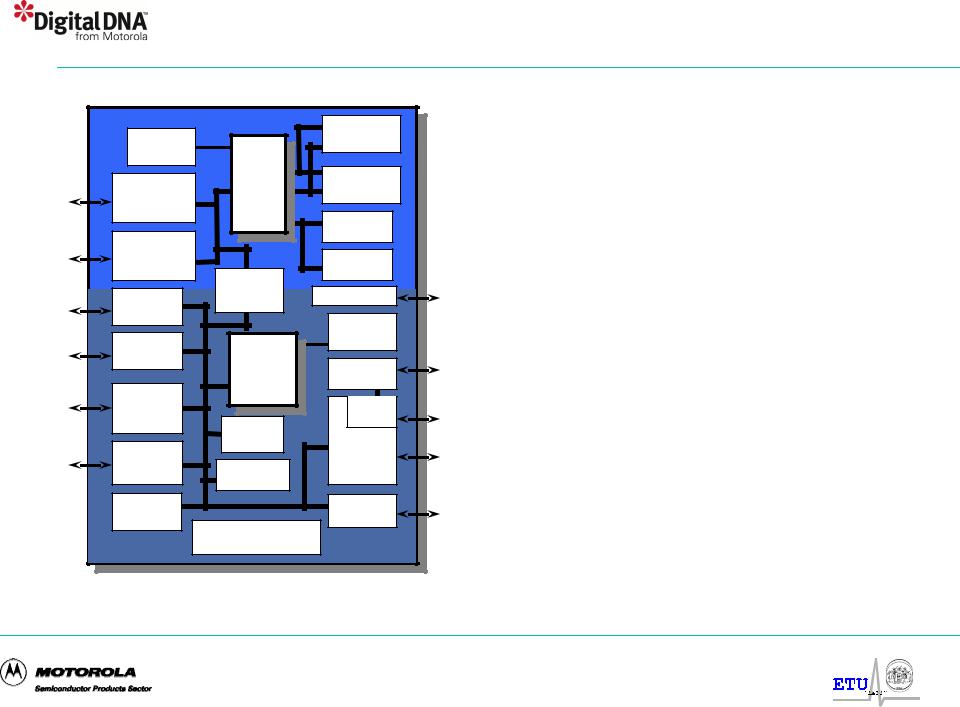

ВАРИАЦИИ DSP56300

DSP56301

•Независимые интерфейсы SRAM/DRAM

•Первый DSP с независимым портом PCI

•Два синхронных последовательных порта 20Mбит/с

•Один последовательный коммуника- ционный интерфейс 10Mбит/с

•2 опции памяти на кристалле:

-4K или 2K слов ОЗУ программ

-4K или 6K слов 24-битного ОЗУ данных

•Сканирование границ JTAG

•Три 24-битных таймера/счетчика

•208 TQFP и 252 PBGA

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2К х 24 |

|

|

|

2К х 24 |

|

||||||||

|

Х-ОЗУ |

|

|

|

Y-ОЗУ |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ESSI |

|

|

|

|

|

|

|

|

|

ОЗУ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

ESSI |

|

|

|

|

|

|

|

|

|

программ |

|

||

|

|

|

|

|

|

Ядро |

|

|

3К х 24 |

|

||||

|

|

|

|

|

|

|||||||||

|

SCI |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

56300 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||||

|

Host |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|||||

|

интерфейс |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Кэш |

|

||

|

|

|

|

|

|

|

|

|

||||||

|

Таймер |

|

|

|

|

|

|

|

|

инструк- |

|

|||

|

|

|

|

|

|

|

|

|

|

|

ций |

|

||

|

Таймер |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

1К х 24 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

Таймер |

|

|

|

Шина расширения |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Москва, 10-13 мая 2000г.

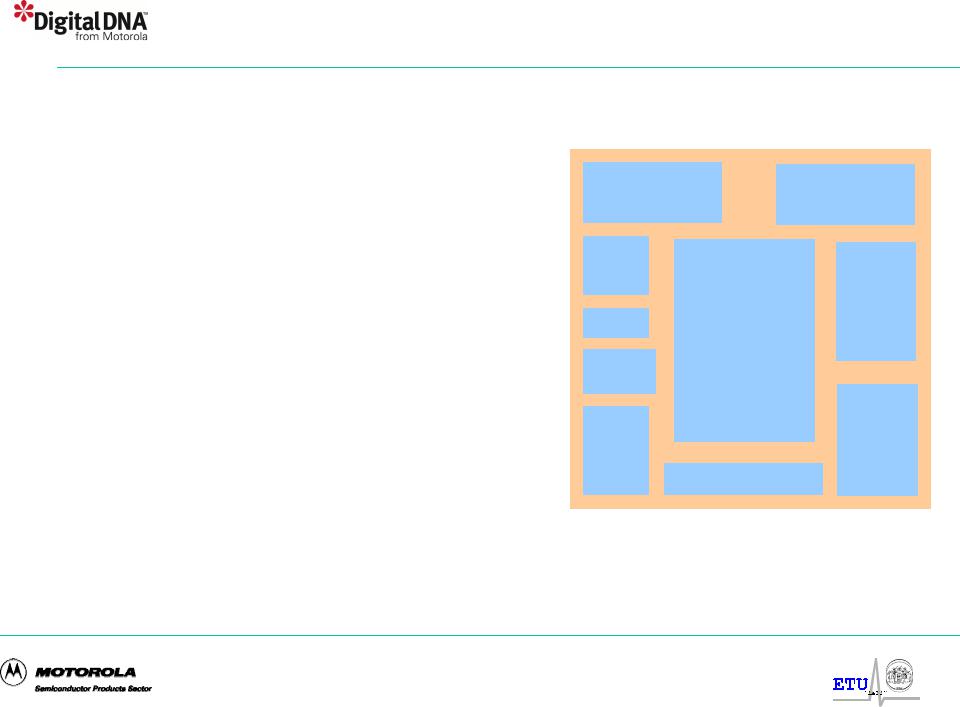

ВАРИАЦИИ DSP56300

DSP56303

•Меньше выводов : 144 TQFP или 196 PBGA

•Дешевая версия 56301

•Шина PCI удалена

•16 выводов GPIO (8 бит Host)

•2 опции памяти на кристалле :

-4K или 2K слов ОЗУ программ

-4K или 6K слов 24-битного ОЗУ данных

•18-битная внешняя адресация

•Независимые интерфейсы SRAM/DRAM

•Два синхронных последовательных

порта 25Mбит/с

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2К х 24 |

|

|

|

2К х 24 |

|

|

||||||

|

Х-ОЗУ |

|

|

|

Y-ОЗУ |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ESSI |

|

|

|

|

|

|

|

|

|

ОЗУ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

ESSI |

|

|

|

|

|

|

|

|

|

программ |

|

|

|

|

|

|

|

|

Ядро |

|

|

3К х 24 |

|

|||

|

|

|

|

|

|

|

|||||||

|

SCI |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

56300 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||||

|

Host |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|||||

|

интерфейс |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Кэш |

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

Таймер |

|

|

|

|

|

|

|

|

инструк- |

|

||

|

|

|

|

|

|

|

|

|

|

|

ций |

|

|

|

Таймер |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

1К х 24 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

Таймер |

|

|

|

Шина расширения |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

•Один последовательный коммуникационный интерфейс 12.5Mбит/с

•Сканирование границ JTAG

•Три 24-битных таймера/счетчика

Москва, 10-13 мая 2000г.

ВАРИАЦИИ DSP56300

Конфигурация памяти DSP56301/3

DSP56301/3 имеет четыре опции размещения памяти на кристалле:

|

|

РЕЖИМ |

По умолчанию |

Режим переключения |

|

|

|

|

|

|

|

|

|

|

|

Кэш |

4K P-ОЗУ |

2K P-ОЗУ |

|

|

|

|

инструкций |

|

|

||

|

|

2K X-ОЗУ |

3K X-ОЗУ |

|

|

|

|

|

запрещен |

|

|

||

|

|

2K Y-ОЗУ |

3K Y-ОЗУ |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

Кэш |

1K Кэш инструкций |

1K Кэш инструкций |

|

|

|

|

инструкций |

3K P-ОЗУ |

1K P-ОЗУ |

|

|

|

|

разрешен |

2K X-ОЗУ |

3K X-ОЗУ |

|

|

|

|

|

2K Y-ОЗУ |

3K Y-ОЗУ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Москва, 10-13 мая 2000г.

ВАРИАЦИИ DSP56300

DSP56309

•Меньше выводов: 144 TQFP или 196 PBGA

•Меньше потребность во внешней памяти:

- 24K или 20K слов ОЗУ программ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7К х 24 |

|

|

|

7К х 24 |

|

|

|

|||||||

- 10K или 14K слов 24-битного ОЗУ данных |

|

|

|

|

|

||||||||||

|

Х-ОЗУ |

|

|

|

Y-ОЗУ |

|

|

|

|||||||

|

|

|

|

|

|

||||||||||

• Удалена шина PCI |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ESSI |

|

|

|

|

|

|

|

|

|

ОЗУ |

|

|

||

• 16 выводов GPIO (8-битный Host) |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

ESSI |

|

|

|

|

|

|

|

|

|

программ |

|

|||

• 18-битная внешняя адресация |

|

|

|

|

|

|

Ядро |

|

|

19К х 24 |

|

||||

|

|

|

|

|

|

||||||||||

|

SCI |

|

|

|

|

|

|

|

|

|

|

||||

• Независимые интерфейсы SRAM/DRAM |

|

|

|

|

|

|

56300 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|||||

|

Host |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

||||||

• Два синхронных последовательных порта |

|

интерфейс |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Кэш |

|

|

||

25Mбит/с |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

Таймер |

|

|

|

|

|

|

|

|

инструк- |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

ций |

|

||

• Один последовательный коммуника- |

|

Таймер |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

1К х 24 |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

ционный интерфейс 12.5Mбит/с |

|

Таймер |

|

Шина расширения |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

• Сканирование границ JTAG |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

• Три 24-битных таймера/счетчика |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Москва, 10-13 мая 2000г.

ВАРИАЦИИ DSP56300

Конфигурация памяти DSP56309

DSP56309 имеет четыре опции размещения памяти на кристалле:

|

|

РЕЖИМ |

По умолчанию |

Режим переключения |

|

|

|

|

|

|

|

|

|

|

|

Кэш |

20K P-ОЗУ |

24K P-ОЗУ |

|

|

|

|

инструкций |

|

|

||

|

|

7K X-ОЗУ |

5K X-ОЗУ |

|

|

|

|

|

запрещен |

|

|

||

|

|

7K Y-ОЗУ |

5K Y-ОЗУ |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

Кэш |

1K Кэш инструкций |

1K Кэш инструкций |

|

|

|

|

инструкций |

19K P-ОЗУ |

23K P-ОЗУ |

|

|

|

|

разрешен |

7K X-ОЗУ |

5K X-ОЗУ |

|

|

|

|

|

7K Y-ОЗУ |

5K Y-ОЗУ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Москва, 10-13 мая 2000г.

ОСОБЕННОСТИ DSP56307

•Новые вариации базируются на ядре DSP56300

•Объектный код совместим с семействами DSP56300 и DSP56000

•Производительность ядра - 100 MIPS

•Аппаратная фильтрация & ускоритель отмены - EFCOP (увеличивает эквивалент MIPS до 170)

•2.5В ядро & 3.3В ввод/вывод (+-10%)

•Память SRAM на кристалле - 1.5 Mb упорядочена как 64K слов

–5 опций переключения памяти:

•Память программ = 16K, 24K, 32K, 40K or 48K

•Память данных = 64K - память программ

•6-канальный контроллер ПДП

•Отдельное питание ядра и ввода/вывода

•2 ESSI, 1 SCI, 1 HI08 и 3 таймера

•196-выводной PBGA (15x15 мм, шаг - 1мм)

Москва, 10-13 мая 2000г.

ОСОБЕННОСТИ DSP56307

Фильтрующий сопроцессор

•EFCOP удваивает производительность, занимая только 3% всей поверхности

•EFCOP - параллельный вычислитель на 100 MHz, оптимизированный для КИХ- и БИХ-фильтров

•EFCOP позволяет выполнять отмену эха (в EFCOP) параллельно с речевой компрессией (в ядре)

•Уменьшает число каналов в многоканальных приложениях таких, как беспроводные транскодеры

Москва, 10-13 мая 2000г.

ЦЕЛЕВЫЕ ПРИЛОЖЕНИЯ DSP56307

Оптимизация для сетевых задач

•Наборы ресурсов DSP

•Передающие беспроводные станции

•Многоканальные беспроводные локальные петли

•Мобильные сотовые центры переключений

•Контроллеры базовых станций

•Оборудование для переключения линий

•Интернет-телефония

•Высокоскоростные банки модемов

Москва, 10-13 мая 2000г.

ОБЗОР DSP56307

•Большой объем памяти на кристалле

•Высокая производительность без параллелизма

•Низкое потребление энергии (0.25 Вт)

•Нет состояний ожидания

•Во многих приложениях не требуется внешнее ОЗУ

•EFCOP

•Сбалансированная архитектура

•Небольшой корпус PBGA (15x15 мм, шаг выводов - 1мм)

•Доступность программных приложений и библиотек фирмы

•Эффективное использование языков высокого уровня

•Совместимость кода с другими членами семейства DSP56300

Москва, 10-13 мая 2000г.

|

|

DSP56652 - процессор с двойным ядром |

||

|

|

ОЗУ данных |

Технология |

|

Отладчик |

|

0.32µ CDR2 (сейчас) |

||

|

14k x 16 |

|||

DSP |

56600 |

|

0.27µ CDR3 (1Q99) |

|

|

|

|||

Последов. |

ПЗУ данных |

Корпус |

||

ядро |

||||

20k x 16 |

||||

|

|

|

||

порт |

DSP |

|

196 PBGA (15мм x 15мм) |

|

Baseband |

|

PROM |

||

|

|

48K x 24 |

Потребление энергии |

|

|

|

|

||

Последов. |

|

512 x 24 |

1.8-2.5В |

|

|

|

|||

Аудио-порт |

|

PRAM |

|

|

DSP/MCU |

|

|

||

|

|

Температура |

||

QSPI |

интерфейс |

Синх/ФАПЧХ |

||

1024 x 16 |

-40 to +850C |

|||

Посл. порт |

|

|||

|

uC |

|||

|

|

Частота |

||

Smartcard |

M•CORE |

отладчик |

||

интерфейс |

|

58.8MHz @1.8В DSP |

||

Интерфейс |

µRISC |

JTAG |

||

ядро MCU |

|

16.8MHz @1.8В M·CORE |

||

|

|

|

||

внешней |

|

MUX |

Состояние |

|

шины |

ОЗУ |

|

||

|

|

производство (сейчас) |

||

Интерфейс |

512 x 32 |

|

||

ПЗУ |

UART |

разработка (июнь 98) |

||

клавиатуры |

||||

|

|

|

||

|

4K x 32 |

|

|

|

Таймер |

|

GPT |

|

|

протокола |

|

|

||

Таймер/PIT |

|

|

||

|

|

|

||

|

Сторожевой таймер |

|

|

|

Москва, 10-13 мая 2000г.

|

|

|

|

Redcap |

|

Ядро DSP56600 |

|||

|

|

|

|

|

|

|

|

•Высокая производительность: |

|

|

|

|

|

|

|

|

|

58.8MHz @1.8V |

|

Аудио-порты |

|

|

|

|

|

|

|

•1x-механизм 60MГц = 60 MIPS |

|

•Полнодуплексная передача |

|

|

|

|

|

|

•16-битные данные |

||

•Стандартная синхронизация кодека |

|

|

|

|

|

•Набор эффективных |

|||

M-CORE MCU |

|

|

|

|

|

|

ОЗУ данных |

24-битных инструкций |

|

|

|

Отладчик |

|

|

|

•16x16=40-битовое умножение |

|||

•16.8MГц @ 1.8В |

|

|

|

|

|

14k x 16 |

•Арифмет. поддержка GSM |

||

•32-битная архитектура, 16-битные |

DSP |

|

|

|

|

•Полная статичность |

|||

инструкции |

|

|

|

|

56600 |

|

•Ультра-низкое энергопотребление |

||

•Плотность кода “Best-in-class” |

|

Последов. |

|

ПЗУ данных |

•Спец. управление энергопотреблением |

||||

|

|

ядро |

|||||||

• |

|

|

|

|

|

||||

Низкое потребление энергии |

|

порт |

|

20k x 16 |

|

||||

•Высокая производительность |

|

|

DSP |

Память DSP |

|||||

•Двойной 16-входовой/32-битный |

|

Baseband |

|

|

|

PROM |

•ПЗУ DSP на кристалле |

||

регистровый файл |

|

|

|

|

|

|

•Возможность смены ПЗУ |

||

•4-уровневый конвейер |

|

|

|

|

|

48K x 24 |

|||

|

|

|

|

|

•ОЗУ DSP на кристалле |

||||

•Одноцикловое выполнение |

|

Последов. |

|

|

|

|

|||

|

|

|

|

PRAM |

|

||||

большинства инструкций |

|

Аудио-порт |

|

|

|

•Гибкая синхронизация |

|||

•Доступ к байту, полу-слову, слову |

|

DSP/MCU |

512 x 24 |

•16-60MГц ФАПЧХ |

|||||

|

|

||||||||

•Поддержка быстрых перываний |

|

|

интерфейс |

Синх/ФАПЧХ |

•Два тактовых входа: |

||||

|

|

|

QSPI |

||||||

Послед. периферийный интерфейс |

|

10-20 MГц или 32KHz |

|||||||

|

1024 x 16 |

||||||||

•Совместимость с SPI |

|

|

Посл. порт |

|

|

|

uC |

Интерфейс MCU-DSP (MDI) |

|

•Переменный размер очереди |

|

|

|

|

|

||||

•Полно- или полудуплексная передача |

|

Smartcard |

|

M•CORE |

отладчик |

•Двойной доступ 1024 x 16-бит |

|||

|

|

|

интерфейс |

|

|

• |

|||

Модуль интерфейса Smartcard |

|

|

Опрос или сообщение о прерывании |

||||||

|

|

µRISC |

JTAG |

|

|||||

•3V Smartcard интерфейс |

|

|

|

Порты отладчика OnCE |

|||||

|

|

ядро MCU |

|

||||||

•Стандарт ISO7816 |

|

Интерфейс |

|

||||||

|

|

|

|

|

• Отладка M·CORE&DSP56600 |

||||

Внешняя шина MCU |

|

|

внешней |

|

|

|

MUX |

•Доступ через порт JTAG |

|

•22-битный адрес |

Порт клавиатуры |

шины |

|

ОЗУ |

|

Тестовый порт доступа JTAG |

|||

•16-битные данные |

|

512 x 32 |

|

||||||

•Раздельная |

•Сканирование 8x8 |

Интерфейс |

|

•Стандарт IEEE 1149.1 |

|||||

|

|

|

|

||||||

системная интеграция |

• |

|

|

|

|

UART |

•Для системной диагностики |

||

|

|

|

|

|

|||||

Или GPIO |

|

клавиатуры |

|

ПЗУ |

•Доступ к M·CORE и DSP |

||||

Таймер протокола |

|

|

|

4K x 32 |

|

|

|||

|

|

Таймер |

|

|

|

|

Послед. коммуникационный порт |

||

•Синхронизация радио-канала |

|

|

|

|

GPT |

||||

•Номер и позиция фрейма |

|

|

протокола |

|

|

|

•Полнодуплексная передача |

||

|

|

|

|

|

|

||||

•Макро-возможности |

|

|

Таймер/PIT |

|

• |

||||

•Двойные счетчики фреймов |

|

|

|

7- или 8-битные операции |

|||||

|

|

Сторожевой таймер |

|

•8-проводной послед. интерфейс |

|||||

•Двойные таблицы событий ОЗУ |

|

|

|

|

|

|

•Поддержка стандарта IrDA |

||

•8 выходов, 4 QSPI триггера |

|

|

|

|

|

|

•выборка/фильтрация приемника |

||

•16 векторных прерываний DSP |

Периодический таймер/Сторожевой |

Таймер общего назначения MCU |

|||||||

•16-байтный стек FIFO |

|||||||||

•“Пробуждение” DSP |

|

•16-бит прерываний “set & forget” |

|

•8-битное масштабирование |

|||||

|

|

•Скорость передачи от 300 до 525Kбит/с |

|||||||

•Рестарт таблицы фреймов/свопинг |

•Обратный счет/свободный счет |

|

•Два 16-битных счетчика |

||||||

|

•Режимы экономия энергии |

||||||||

|

|

•Сторожевой аппаратный сброс |

|

•3 вых. сравнения/2 вх. захвата |

|||||

|

|

|

|

||||||

|

|

•Период Watchdog : от 0.5 до 32 с |

|

•Возможности ШИМ |

|

||||

|

|

|

Москва, 10-13 мая 2000г. |

|

|||||