- •Развитие семейств микроконтроллеров

- •Области использования микроконтроллеров

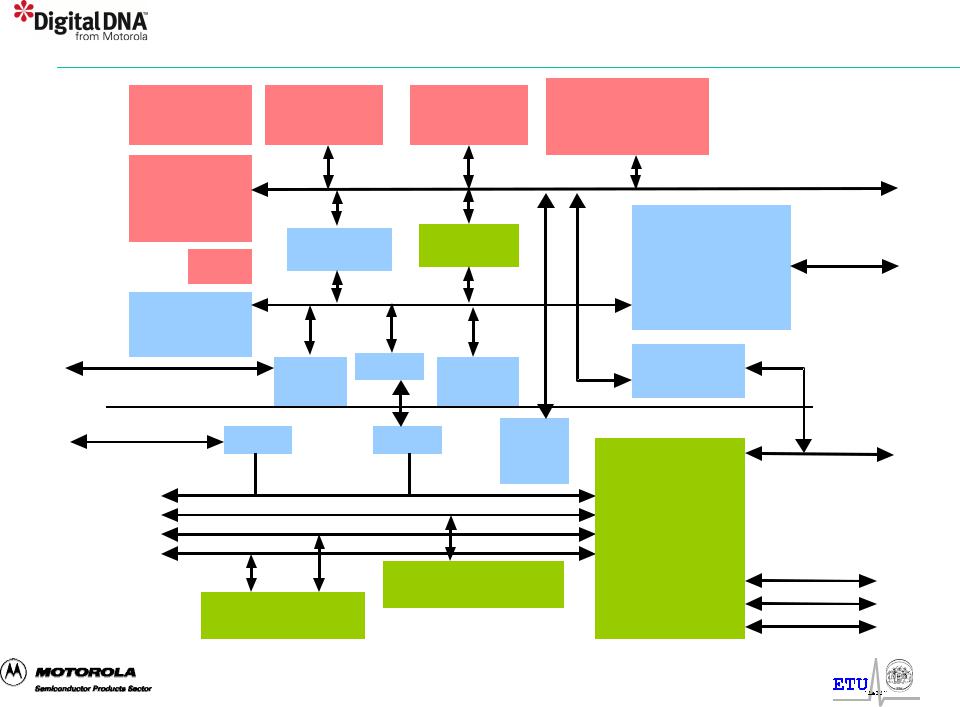

- •Обобщенная модель микроконтроллера

- •Сопроцессоры

- •Таймерные модули

- •Модули связи

- •Модули системной интеграции

- •Средства отладки

- •Модули памяти

- •Cемейство 16-разрядных МК М68НС12

- •Семейство М68НС12

- •Семейство МК М68НС16

- •Программная модель CPU16 и НС11

- •Сравнительная характеристика 8- и 16-разрядных МК

- •Семейство 32-разрядных МК 68300

- •Программная модель CPU32

- •Семейство МК М68300 (Интегрированные процессоры)

- •Семейство МК 68300

- •Семейство 32-разрядных процессоров ColdFire

- •Семейство процессоров ColdFire

- •Характеристики процессоров семейства ColdFire

- •Семейство СoldFire

- •Семейства на базе PowerPC

- •Ядро RCPU PowerPC

- •Характеристики МК Power QUICC

- •Управление энергопотреблением

- •Средства отладки

- •Средства отладки (MMDS1632)

- •Средства отладки (MEVB1632)

- •Операционные системы реального времени

- •Корпуса типа PGA и QFP

- •Корпус типа BGA

- •Операционный базис процессоров DSP. Фильтрация

- •Операционный базис процессоров DSP. Спектральный анализ

- •Обобщенная структура процессора семейства DSP68356

- •Семейство DSP 56000 (ядро процессора)

- •Семейство DSP 56000 (ядро процессора)

- •Семейство DSP 56000 (ядро процессора)

- •Семейство DSP 56000 (ядро процессора)

- •Семейство DSP 56000 (Порты ввода-вывода - A, B, C)

- •ХАРАКТЕРИСТИКИ DSP56300

- •ОСОБЕННОСТИ DSP56300

- •ОСОБЕННОСТИ DSP56300

- •ОСОБЕННОСТИ DSP56300

- •ОСОБЕННОСТИ DSP56300

- •ОСОБЕННОСТИ DSP56300

- •ВАРИАЦИИ DSP56300

- •ВАРИАЦИИ DSP56300

- •ВАРИАЦИИ DSP56300

- •ВАРИАЦИИ DSP56300

- •ВАРИАЦИИ DSP56300

- •ОСОБЕННОСТИ DSP56307

- •ОСОБЕННОСТИ DSP56307

- •ЦЕЛЕВЫЕ ПРИЛОЖЕНИЯ DSP56307

- •ОБЗОР DSP56307

- •DSP56652 - процессор с двойным ядром

- •Redcap2 - 5665_

- •Redcap2 (продолжение)

Корпус типа BGA

Шаг |

MC68356 |

|

1.27мм |

MC68360 |

|

|

MPC860 |

25 мм |

1.2 мм

357 шариковый PBGA MC68356,DP356

MC68360,MH360,EN360

MPC860,860EN,860DC,860DE,860MH

Microcontrollers CISC & RISC

Операционный базис процессоров DSP. Фильтрация

x |

|

|

|

|

Ф и л ь т р а ц и я |

|

|

|

|

||

|

|

|

|

|

|

|

Б И Х -ф и л ь т р |

|

|

x |

|

|

|

|

|

|

|

|

|

|

|

||

|

x (n ) |

К И Х -ф и л ь т р |

|

|

|

y (n ) |

|

|

|||

t |

|

|

|

|

|

t |

|||||

|

А Ц П |

N |

1 |

|

|

M 1 |

|

|

|

Ц А П |

|

|

b k |

x n k |

|

a k |

y |

|

|

|

|||

|

|

n k |

|

|

|

||||||

|

|

k |

0 |

|

|

k 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

З а д е р ж к а |

|

|

|

|

|

|

|

X |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Д и с к р е т н а я |

|

|

|

|

|

|

|

|

|

|

|

с в е р т к а |

|

|

|

|

|

|

|

|

M A C |

|

|

|

|

|

|

|

|

|

|

Москва, 10-13 мая 2000г. |

|

|

|

|||||

Операционный базис процессоров DSP. Спектральный анализ

Операционный базис процессоров DSP. Спектральный анализ

x

t x(n) АЦП

t x(n) АЦП

Перестановка

входныхотсчетов (бит-реверсивная адресация)

|

Спектральныйанализ |

|

|

|

|

|

|

|

|

|

|

БПФ |

|

|

|

|

|

Расчет |

|

|

p |

N1 p j(2/Nn)k |

|

|

|

амплитуды |

|||

|

k |

|

|

|

|

|

|

|

|

|

X x e |

|

|

|

|

|

ифазы |

||

|

|

n |

|

|

|

|

|

||

|

|

n0 |

|

|

|

|

|

гармоник |

|

|

Базоваяоперация“бабочка” |

|

|

|

X X спектр |

||||

|

повременипочастоте |

|

|

2 |

2 |

||||

|

|

|

Re Im |

||||||

|

|

k |

X=A+B |

|

|

N , |

|||

|

X=A+BWА |

|

|

|

X |

||||

А |

|

n |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Re |

||

|

+ |

|

+ |

|

|

|

|

arct, |

|

|

|

|

k |

|

|

|

X |

||

|

k |

|

|

|

|

|

|

Im |

|

|

n |

|

- |

W |

|

logx, |

|||

B |

W - |

B |

|

n |

|

||||

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

2 |

|

||

|

|

k |

|

|

|

k |

|

|

|

|

Y=A-BW |

Y=(A-B)W 2 |

|

||||||

|

|

n |

|

|

|

n |

|

x |

|

|

|

|

|

|

|

|

|

||

|

X |

|

|

|

|

|

|

Таблицыsin,cos |

|

|

|

|

|

|

|

|

илитаблица |

||

|

|

|

|

|

|

|

|

|

k |

|

|

|

|

|

|

|

|

значенийW |

|

|

|

|

|

|

|

|

|

|

n |

|

|

|

|

|

X |

|

|

|

|

Москва, 10-13 мая 2000г.

|

Обобщенная архитектура процессора DSP |

||||

|

|

|

Процессорное ядро |

||

Блок управления |

Блок выполнения операций |

Блок отладки |

|||

|

|

с фиксированной |

с плавающей |

||

Блок |

Блок |

и контроля |

|||

точкой |

точкой |

||||

|

|||||

генерации |

управления |

bk,ak xn-k,yn-k |

|

OnCE, JTAG, |

|

адреса |

программой |

|

|

||

|

|

Блок |

Сопроцессоры: |

WDТ |

|

|

|

|

|||

Синтезатор |

Контроллер |

задержки |

фильтр-сопроцессор, |

|

|

|

витерби-сопроцессор, |

|

|||

тактовой |

прерываний |

|

сопроцессор |

|

|

частоты |

|

МАС, АЛУ |

циклического кода |

|

|

|

|

|

|

||

Подсистема ввода/вывода

Периферийные устройства

Кодек, порты ввода/вывода, host-интерфейс, таймеры и т.п.

Подсистема хранения

Внутренняя память

Память |

|

|

|

|

|

|

|

Память |

|

|

Память |

|

|

данных |

|

|

|

|

||

|

данных |

|

|

значений sin, |

|

|

Х |

|

|

|

|

||

|

Y |

|

|

arctg и т.д. |

|

|

|

|

|

|

|

||

Память |

|

|

|

|

|

|

Память |

|

|

Память |

|

||

значений |

|

|

|

|

||

|

загрузки |

|

|

программ |

|

|

Wnk |

|

|

|

|

Москва, 10-13 мая 2000г.

|

Обобщенная структура процессора семейства DSP56K |

|||||||||

Порт В или |

|

|

|

|

|

|

|

|

|

|

host- |

|

|

|

|

|

|

|

|

|

|

интерфейс |

Периферийные |

Память |

Память |

Память |

|

|

|

|||

|

|

|

|

|||||||

|

модули |

программ |

данных |

данных |

|

|

|

|||

|

|

|

ОЗУ/ПЗУ |

|

X |

Y |

|

|

|

|

Порт С или |

|

|

|

|

ОЗУ/ПЗУ |

ОЗУ/ПЗУ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SSI, SCI, |

|

|

|

|

|

|

|

|

|

|

SAI, GPIO, |

|

Устройство |

|

|

|

|

|

Переключатель |

16 |

|

T, PWM |

|

|

|

|

XAB |

|

|

|||

|

|

генерации |

|

|

|

|

внешних шин |

|

|

|

|

|

|

|

|

PAB |

|

|

|

||

|

|

адреса |

|

|

|

|

адреса |

Адрес |

|

|

|

|

|

|

|

|

|

|

Управление |

7 |

Порт А |

|

|

|

|

|

|

|

|

шинами |

|

|

|

|

|

|

|

|

|

|

Управ- |

или |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

YDB |

|

|

|

EMI |

|

Переключатель |

|

|

|

|

|

Переключатель |

ление |

|||

|

|

|

XDB |

|

|

|

|

|||

внутренних |

|

|

|

|

PDB |

|

|

внешних шин |

24 |

|

шин данных |

|

|

|

|

|

|

данных |

|

|

|

|

|

|

|

GDB |

|

|

Данные |

|

||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

Генератор |

Контрол- |

Контрол-лер |

Генера- |

АЛУ данных |

OnCE |

|

|

|||

|

24х24+56 56-бит МАС |

|

|

|||||||

PLL |

лер |

декоди- |

|

тор |

|

|

||||

|

Два 56-битных |

|

|

|

||||||

|

преры- |

рования |

адреса |

|

|

|

||||

|

аккумулятора |

|

|

|

||||||

|

ваний |

программ |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|||

RESET |

MODC/ NMT |

|

|

|

16 бит |

|

|

|

||

MODB/ IRQB |

|

|

|

|

|

|

||||

|

|

|

24 бита |

|

|

|

||||

|

|

MODA/ IRQA |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||

|

|

|

. |

|

|

|

|

|

|

|

|

Обобщенная структура процессора семейства DSP56300 |

|||||||||||||

|

|

52 |

6 |

6 |

3 |

|

|

|

|

|

|

|

|

|

Сопроцес- |

Утро- |

|

ESSI0 |

|

SCI |

ПЗУ |

|

|

Память |

Память |

|

|

||

соры FCOP, |

енный |

Host |

ESSI1 |

|

программ |

|

|

Х |

|

Y |

|

|

||

VCOP, CCOP |

таймер |

|

|

|

|

|

|

|

|

ОЗУ |

|

ОЗУ |

|

|

|

|

|

|

|

|

|

|

|

|

ПЗУ |

|

ПЗУ |

Управление |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

энергопо- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

треблением |

|

|

Устройство |

|

PIO_EB |

PM_EB |

|

XM_EB |

YAB |

YM_EB |

Переключатель |

|

||||

|

|

|

|

|

|

|

|

|

XAB |

|

24 |

|||

|

генерации |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

PAB |

|

внешних шин |

|

||

|

адреса |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

адреса |

|

||

|

|

|

|

|

|

|

|

|

|

DAB |

|

Адрес |

||

|

Контроллер |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

ПДП |

|

|

|

|

|

|

|

|

|

|

|

Управление |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Загрузочное |

|

|

|

|

|

|

|

|

|

|

внешними |

14 |

|

|

ПЗУ |

|

|

|

|

|

|

|

|

|

|

|

шинами и кэш |

Управ- |

|

|

|

|

|

|

|

|

|

|

|

|

|

команд |

|

|

Переключатель |

|

|

|

|

|

|

|

DDB |

|

|

Переключатель |

ление |

|

|

|

|

|

|

|

|

|

YDB |

|

|

24 |

|||

|

внутренних |

|

|

|

|

|

|

|

XDB |

|

|

внешних шин |

||

|

|

|

|

|

|

|

|

|

|

|

||||

|

шин данных |

|

|

|

|

|

|

|

|

|

данных |

|

||

|

|

|

|

|

|

|

|

PDB |

|

|

Данные |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

GDB |

|

|

|

|

|

Генератор |

|

|

|

|

|

|

|

|

|

АЛУ данных |

OnCE |

6 |

|

|

Контрол- |

|

Контрол-лер |

Генера- |

|

|

||||||||

|

и PLL |

|

24х24+56 56-бит МАС |

JTAG |

||||||||||

|

|

лер |

|

декоди- |

|

|

тор |

|

||||||

|

|

|

|

|

|

|

|

Два 56-битных |

JTAG |

|

||||

|

|

преры- |

|

рования |

|

адреса |

|

|

||||||

|

|

|

|

|

аккумулятора |

|

|

|||||||

|

|

|

ваний |

|

программ |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

2 |

|

|

|

MODD/ IRQD |

|

|

|

|

|

|

|

||

|

RESET |

|

|

MODC/ IRQC |

|

|

|

|

|

|

|

|

||

|

PINIT/ N |

|

|

MODB/ IRQB |

|

|

|

|

|

|

|

|

||

|

|

|

|

MODA/ IRQA |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

. |

|

|

|

|

|

|

|

|

|

Обобщенная структура процессора семейства DSP68356

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 таймера |

|

|

|

||

|

Управление |

|

|

|

Контроллер |

|

|

|

|

|

|

1 основной |

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 сигнала выбора |

|

|

|

||||||||||||||||||

|

энергопотреб- |

|

|

|

прерываний |

|

|

|

|

|

|

|

|

канал |

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIO |

|

|

|

|||||||||||||||

|

лением |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DMA |

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Системный контроль |

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Cистемная шина |

||||||||||||

|

Статическое |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

68000 |

|

|

|

|

|

||||||||||||

|

ядро |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

М68000 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Интерфейс |

|

|||||

|

|

|

|

|

|

|

|

|

|

6 каналов |

|

|

|

|

|

1152 байт |

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

SDMA |

|

|

|

|

|

|

|

RAM |

|

|

|

|

|

ведомого PCMCIA |

|

||||||||||

|

|

|

PIT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

+ |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Интерфейс |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16550 UART |

|

||

|

RISC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

Контроллер |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Режим |

|

|

|

|

|

|

|

|

|

|

|

SCC2& |

|

|

SCC1 |

|

|

|

SCP + |

|

|

|

|

|

прямого |

|

|

||||||||||||

68302 |

|

|

|

|

|

|

SCC3 |

|

|

|

|

|

|

|

|

|

|

|

|

2 SMCs |

|

|

|

|

|

|

|

доступа |

|

|

|||||

56002 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Glue |

|

|

|

|

|

|

|

|

|||||||

|

SSI |

|

|

|

|

|

|

|

|

SCI+ |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Внешняя шина I/F |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Host |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

Периферийная шина |

|

|

|

|

|

i/f |

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ядро 56002 |

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

Программная шина |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

Шина данных Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

Шина данных Х |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

512х24 ОЗУ программ |

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PLL&Clocks |

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

64х24 загрузочное ПЗУ |

|

|

|

|

|

|

|

|

||||||||||

|

|

|

5.5Kx24 ПЗУ данных |

|

|

|

|

|

|

|

Прерывания |

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5.5Кх24 ОЗУ данных |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OnCE |

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

.

Семейство DSP 56000 (ядро процессора) |

|||

MAC и логическое устройство |

|||

Шина данных Х |

|

|

|

Шина данных Y |

|

|

|

|

24 |

24 |

|

|

X0 |

|

|

|

X1 |

|

|

|

Y0 |

|

|

|

Y1 |

|

|

|

24 |

24 |

|

|

Умножитель |

|

|

|

Аккумулятор, и |

56 |

|

|

логическое устройство |

|

|

56 |

|

|

|

Устройство |

56 |

|

|

сдвига |

А (56) |

|

|

|

|

|

|

|

В (56) |

|

|

|

56 |

56 |

|

|

Устройство сдвига/ограничения |

|

|

|

|

|

24 |

|

|

|

24 |

Семейство DSP 56000 (ядро процессора)

Устройство генерации адреса - AGU

|

|

|

А Л У н и ж н и х а д р е с о в |

|

|

|

|

|

|

|

|

|

|

|

|

А Л У в е р х н и х а д р е с о в |

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

X A B |

Y A B |

P A B |

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 6 |

|

1 6 |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

1 6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

Т р о й н о й м у л ь т и п л е к с о р |

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

N 0 |

|

M 0 |

|

|

|

|

|

|

R 0 |

|

|

|

R 4 |

|

|

|

|

|

|

|

|

M 4 |

|

N 4 |

||||||||

|

|

|

|

|

|

А Л У |

|

|

R 1 |

|

|

|

R 5 |

|

|

|

|

А Л У |

|

|

|

|

|

|

|

||||||||

|

N 1 |

|

M 1 |

|

|

|

|

|

|

|

|

|

|

|

|

M 5 |

|

N 5 |

|||||||||||||||

|

|

|

|

|

|

|

а д р е со в |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а д р ес о в |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

R 2 |

|

|

|

R 6 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

N 2 |

|

M 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

M 6 |

|

N 6 |

||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

R 3 |

|

|

|

R 7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

N 3 |

|

M 3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

M 7 |

|

N 7 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Г л о б а л ь н а я ш и н а д а н н ы х

.

Семейство DSP 56000 (ядро процессора)

Линейная модификация: постинкремент со смещением

R0=R0+N0

Модульная модификация:

П р и м е р : M O V E X 0 ,X (R 2 )+ N

M 2 |

0 0 ...........0 0 1 0 1 0 0 |

|

М о д у л ь = 2 1 |

|||||||

N 2 |

|

|

|

|

С м е щ е н и е = 1 5 |

|||||

0 0 ...........0 0 0 1 1 1 1 |

|

|||||||||

R 2 |

|

|

|

|

У к а з а т е л ь = 7 5 |

|||||

0 0 ...........1 0 0 1 0 1 1 |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(9 0 ) |

|

|

|

|

|

|

|

+ |

|

|

|

|

(8 4 ) |

|

|

|||

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|||||

|

(7 5 ) |

N 2 |

|

|

Ш и н а X D |

|||||

|

|

|

||||||||

R 2 |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 1 |

|

|

|||

|

|

|

|

|

|

|

|

|||

|

|

|

(6 9 ) |

|

|

|||||

|

|

|

|

|

|

|

|

X 0 |

||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(6 4 ) |

|

|

||

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

Бит-реверсивная модификация

В х о д н а я |

В ы х о д н а я |

п о с л е д о в а т е л ь н о с т ь |

п о с л е д о в а т е л ь н о с т ь |

0 0 0 |

0 0 0 |

1 0 0 |

0 0 1 |

0 1 0 |

0 1 0 |

1 1 0 |

0 1 1 |

0 0 1 |

1 0 0 |

1 0 1 |

1 0 1 |

0 1 1 |

1 1 0 |

1 1 1 |

1 1 1 |

Начальные значения: |

|

|

|

|

7 6 |

|

|

|

|

||

|

|

|

|

||

|

|

|

|

||

|

|

|

|

||

M 0=0, R0=64, N0=8 |

|

|

|

|

7 2 |

|

|

|

|

||

|

|

|

|

||

Постинкремент со смещением N0: |

|

|

|

|

6 8 |

|

|

|

|

||

1) R0=72 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

||

|

|

|

|

|

|

2) R0=68 |

R 0 |

|

|

|

6 4 |

|

|||||

|

|

||||

3) R0=76 |

|

|

|

|

|

|

|

|

|

|

.