- •Развитие семейств микроконтроллеров

- •Области использования микроконтроллеров

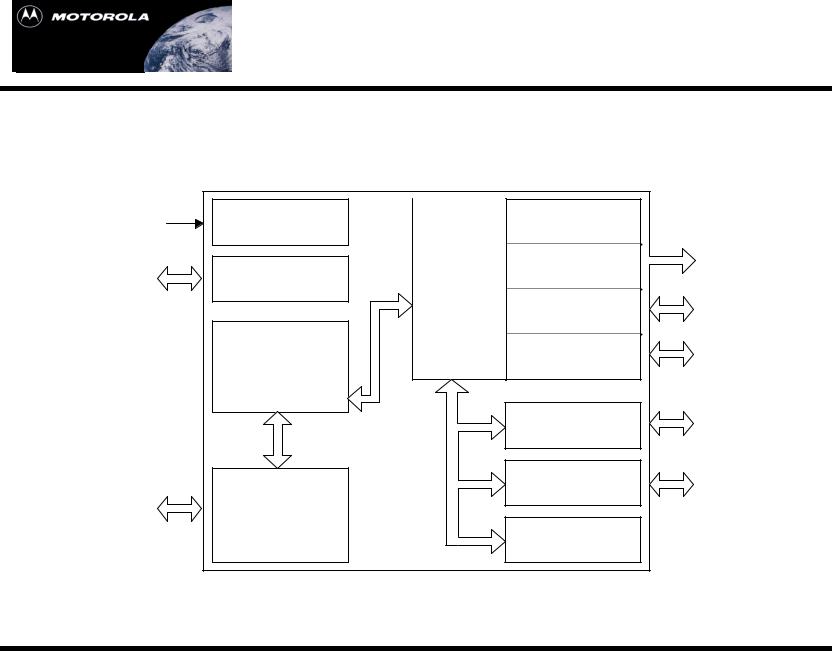

- •Обобщенная модель микроконтроллера

- •Сопроцессоры

- •Таймерные модули

- •Модули связи

- •Модули системной интеграции

- •Средства отладки

- •Модули памяти

- •Cемейство 16-разрядных МК М68НС12

- •Семейство М68НС12

- •Семейство МК М68НС16

- •Программная модель CPU16 и НС11

- •Сравнительная характеристика 8- и 16-разрядных МК

- •Семейство 32-разрядных МК 68300

- •Программная модель CPU32

- •Семейство МК М68300 (Интегрированные процессоры)

- •Семейство МК 68300

- •Семейство 32-разрядных процессоров ColdFire

- •Семейство процессоров ColdFire

- •Характеристики процессоров семейства ColdFire

- •Семейство СoldFire

- •Семейства на базе PowerPC

- •Ядро RCPU PowerPC

- •Характеристики МК Power QUICC

- •Управление энергопотреблением

- •Средства отладки

- •Средства отладки (MMDS1632)

- •Средства отладки (MEVB1632)

- •Операционные системы реального времени

- •Корпуса типа PGA и QFP

- •Корпус типа BGA

- •Операционный базис процессоров DSP. Фильтрация

- •Операционный базис процессоров DSP. Спектральный анализ

- •Обобщенная структура процессора семейства DSP68356

- •Семейство DSP 56000 (ядро процессора)

- •Семейство DSP 56000 (ядро процессора)

- •Семейство DSP 56000 (ядро процессора)

- •Семейство DSP 56000 (ядро процессора)

- •Семейство DSP 56000 (Порты ввода-вывода - A, B, C)

- •ХАРАКТЕРИСТИКИ DSP56300

- •ОСОБЕННОСТИ DSP56300

- •ОСОБЕННОСТИ DSP56300

- •ОСОБЕННОСТИ DSP56300

- •ОСОБЕННОСТИ DSP56300

- •ОСОБЕННОСТИ DSP56300

- •ВАРИАЦИИ DSP56300

- •ВАРИАЦИИ DSP56300

- •ВАРИАЦИИ DSP56300

- •ВАРИАЦИИ DSP56300

- •ВАРИАЦИИ DSP56300

- •ОСОБЕННОСТИ DSP56307

- •ОСОБЕННОСТИ DSP56307

- •ЦЕЛЕВЫЕ ПРИЛОЖЕНИЯ DSP56307

- •ОБЗОР DSP56307

- •DSP56652 - процессор с двойным ядром

- •Redcap2 - 5665_

- •Redcap2 (продолжение)

Семейство МК 68300

(коммуникационные контроллеры)

|

|

CPU |

SIM |

|

Модуль системной интеграции |

МС68302 |

|

|

|

|

|

||

Шина М68000 |

|

|

|

|

Контроллер памяти |

Управление |

ЯДРО |

|

|

|

|

|

|

|

|

|

|

Контроллер прерываний |

|

|

М68000 |

|

|

|

|

|

|

|

|

|

|

|

Арбитр шины |

|

|

|

|

|

|

Логика CS & WS |

|

|

|

|

CPM |

|

|

|

Параллельный В/В |

1152 байт |

|

|

6 каналов SDMA |

|

|

|

|

RAM |

|

|

|

|

Генератор |

|

|

1 IDMA |

|

||

|

|

|

|

|||

Параллельный В/В |

|

|

|

|

|

|

Параллельный |

16-битный RISC МК и |

|

|

|

||

порт интерфейса |

программное ПЗУ |

|

|

|

||

|

|

|

|

|

МС68302 |

|

SCC1 |

SCC2 |

SCC3 |

SMC1 |

SMC2 |

SCP |

|

|

|

Последовательный интерфейс |

|

|

||

Microcontrollers CISC & RISC

|

|

|

|

|

|

Семейство МК 68300 |

||

|

|

|

|

|

|

(коммуникационные контроллеры) |

||

Управление |

|

|

|

1 основной |

|

3 таймера |

|

|

|

|

|

|

4 сигнала выбора |

|

|

||

энергопотреб- |

|

Контроллер |

канал |

|

MC68356 |

|

||

|

|

PIO |

|

|||||

лением |

|

прерываний |

DMA |

Системный контроль |

|

|

||

|

|

|

|

|

|

|

||

|

|

|

|

|

Cистемная |

|

|

|

Статическое |

|

|

|

|

шина |

|

|

|

ядро |

|

|

|

|

|

|

|

|

М68000 |

|

|

|

|

|

|

|

адреса 24 |

|

|

|

|

1152 байт |

|

Интерфейс |

||

|

|

6 каналов |

|

данные 8/16 |

||||

PIT |

|

SDMA |

|

RAM |

|

ведомого PCMCIA |

|

|

|

|

|

|

|

+ |

|

|

|

|

|

|

|

|

|

Интерфейс |

адреса 12 |

|

|

|

|

|

|

|

16550 UART |

||

RISC |

|

|

|

|

|

|

|

данные 8/16 |

|

|

|

|

|

|

|

|

|

Контроллер |

|

|

|

|

|

|

|

|

|

|

SCC2& |

SCC1 |

SCP + |

|

Режим |

|

|

|

|

|

прямого |

|

|

|||

68302 |

|

SCC3 |

|

2 SMCs |

|

доступа |

|

|

56002 |

|

|

|

|

Glue |

|

|

Системная |

SSI |

|

SCI+ |

|

|

|

шина |

||

|

|

|

Host |

Внешняя шина I/F |

|

|||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

Периферийная шина |

|

i/f |

|

|

адреса 16 |

||

|

|

|

Ядро 56002 |

|

данные 24 |

|||

|

|

Программная шина |

|

|

|

|||

|

|

|

|

|

|

|

||

|

|

Шина данных Y |

|

|

|

|

|

|

|

|

Шина данных Х |

|

|

|

|

||

|

|

|

5.25х24 ОЗУ программ |

PLL&Clocks |

|

|

||

|

|

|

64х24 загрузочное ПЗУ |

|

|

|||

5.5Kx24 ПЗУ данных |

Прерывания |

|

|

|||||

|

|

|

|

|

||||

5.5Кх24 ОЗУ данных |

|

|

|

OnCE |

|

357-контактный |

||

|

|

|

|

|

|

|

|

PBGA |

Microcontrollers CISC & RISC

|

|

|

|

|

|

|

Семейство МК 68300 |

|

|

|

|

|

|

|

|

|

(сопроцессор ЦОС) |

|

|

|

|

|

|

|

|

Основные параметры: |

|

|

|

|

|

|

|

|

• |

Ядро сопроцессора - DSP56002 |

|

|

производительность |

|||||

|

|

-30MIPS |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

на частоте 60 Мгц |

|

|

|

|

|

|

|

|

• |

|

|

|

|

|

|

|

|

параллельный 24-битный |

|

|

|

|

|

|

|

|

умножитель-аккумулятор |

|

|

|

|

|

|

|

|

24-разрядная шина данных |

|

|

|

|

Кшине |

|

|

|

• |

|

|

КSCC |

68000 |

|

|

|

• |

|

|

|

|

|

|

|

Системная |

|

16-разрядная шина адреса |

56002 |

|

|

|

Host- |

|

шина |

|

программное ОЗУ 5.25Кх24 |

|

|

|

|

|

56002 |

|

• |

|

|

SSI |

|

SCI+ |

интерфей |

ВнешняяшинаI/F |

|

|

• |

|

|

с |

|

|

||||

|

|

|

|

|

|

Адрес -16 |

|

ПЗУ начальной загрузки |

|

Периферийная шина |

|

|

|

64х24 |

|||

|

|

Ядро56002 |

Данные -24 |

|

||||

|

Программная шина |

|

|

|||||

|

|

|

|

|

• |

|||

|

|

|

|

|

|

|

|

|

|

|

ШинаданныхY |

|

|

|

|

ОЗУ Х данных 3Кх24 |

|

|

|

ШинаданныхХ |

|

|

|

|

• |

|

|

|

|

512х24ОЗУпрограмм |

PLL&Clocks |

|

|

ОЗУ Y данных 2.5Кх24 |

|

|

|

|

|

|

|

|

• |

|

15Kx24ПЗУданных |

|

|

Прерывания |

|

|

|||

|

|

|

64х24 загрузочноеПЗУ |

|

Управление |

|

|

|

|

|

|

37Кх24ПЗУпрограмм |

|

|

|

• |

|

5.5Кх24ОЗУданных |

|

|

OnCE |

357-контактный |

|

|||

|

|

|

|

|

|

PBGA |

|

• |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

прямой доступ из DSP в |

|

|

|

|

|

|

|

|

• |

|

|

|

|

|

|

|

|

магистраль 68000 |

Microcontrollers CISC & RISC

|

|

|

|

|

|

Семейство МК 68300 |

|

|

|

|

|

(коммуникационные контроллеры) |

|

|

|

CPU |

SIM |

|

|

Модуль системной интеграции |

Шина |

|

|

|

|

|

Контроллер памяти |

CPU32+ |

|

|

|

|

|

|

ЯДРО |

|

|

|

|

|

Контроллер DRAM |

CPU32+ |

|

|

|

|

|

Контроллер SRAM |

|

|

|

|

|

|

Арбитр шины |

|

|

|

|

|

|

Системные функции |

BDM |

|

|

|

|

|

Логика CS & WS |

|

|

|

|

|

МС68360 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Управление |

|

|

|

CPM |

|

|

|

Параллельный В/В |

2.5K |

Контроллер |

4 |

|

14 каналов |

|

Генератор |

RAM |

прерываний |

Таймера |

SDMA |

||

|

|

|

|

2 |

||

В/В |

|

|

|

|

|

IDMA |

Параллельный |

32-битный RISC МК и |

|

||||

|

|

|||||

порт интерфейса |

программное ПЗУ |

|

|

|

||

SCC1 |

SCC2 |

SCC3 |

SСC4 |

SMC1 |

SMC2 |

SPI |

|

|

|

|

Последовательный интерфейс |

||

Распределитель временных |

|

Распределитель временных |

||||

|

слотов А |

|

|

слотов В |

М68360 |

|

|

|

|

|

|

|

|

Microcontrollers CISC & RISC

Семейство 32-разрядных процессоров ColdFire

Промышленные системы управления, устройства связи, Области применения коммуникационное и сетевое оборудование,

высокопроизводительные системы при низкой стоимости, портативная техника

Формула семейства

ColdFire=CORE&SI&BDM&JTAG&CI/Dv CORE&BDM&JTAG&CI/D&((T&UART)v(T&UART&I2C))

Основные характеристики |

Совместимость с М68000. Встроенный отладчик |

|

и тестовый интерфейс. RISC-ядро с переменной |

|

длиной команд |

Microcontrollers CISC & RISC

Семейство процессоров ColdFire

|

|

|

MCF 5204 |

|

|

|

C L O C K |

|

С и с т е м н а я |

|

|

|

|

|

з а щ и т а |

В ы б о р |

|

J T A G |

J T A G |

К о н т р о л л е р |

В ы б о р |

||

и н т е р ф е й с |

м и к р о с х е м ы |

м и к р о с х е м ы |

|||

|

с и с т е м н о й |

||||

(д и а г н о с т и к а |

и |

К о н т р о л л е р |

П о д д е р ж к а |

||

ш и н ы |

|||||

т е с т и р о в а н и е |

|

п р е р ы в а н и й |

п р е р ы в а н и й |

||

|

|

||||

|

5 1 2 к э ш |

|

И н т е р ф е й с |

В н е ш н я я |

|

|

|

в н е ш н е й ш и н ы |

ш и н а |

||

|

и н с т р у к ц и й |

|

|||

|

|

|

|

||

|

5 1 2 б а й т S R A M |

|

|

П о с л е д о в а - |

|

|

|

|

U A R T |

||

|

|

|

|

т е л ь н ы й |

|

|

|

|

|

и н т е р ф е й с |

|

B D M |

|

|

Т а й м е р 1 |

П о д д е р ж к а |

|

Я д р о |

|

|

т а й м е р а |

||

и н т е р ф е й с |

C O L D F IR E |

|

Т а й м е р 2 |

|

|

( ф о н о в ы й |

|

|

|||

|

|

|

|||

р е ж и м о т л а д к и ) |

|

|

|

||

Microcontrollers CISC & RISC

Характеристики процессоров семейства ColdFire

Процессор |

f, |

Uп, |

ColdFire |

МГц |

V |

MCF5102 |

16 |

|

|

20 |

|

|

25 |

3,3 |

|

33 |

|

|

40 |

|

MCF5202 |

16 |

|

|

25 |

5 |

|

33 |

|

MCF5203 |

16 |

|

|

25 |

5 |

|

33 |

|

MCF5204 |

16 |

|

|

25 |

5 |

|

33 |

|

MCF5206 |

16 |

|

|

25 |

5 |

|

33 |

|

P |

MIPS на макс. |

|

частоте |

0,64W |

27 |

268mW |

27 |

348mW |

|

0,3W |

25 |

284mW |

13,5 |

369mW |

|

325mW |

17 |

425mW |

|

Размер

шины

32 бита (динам.)

32 бита (динам.)

16 бит (динам.)

32 бита адрес/

16 бит данные

32 бита (динам.)

Размер кэша |

Память |

|

Модули |

Технология/ |

I/D |

|

|

|

корпус |

2Кб/1Кб |

-- |

Встроенный |

0,65 /TLM14 |

|

|

|

отладочный модуль |

4 |

|

|

|

|

|

TQFP |

2 Кб |

-- |

Встроенный |

100 pin TQFP |

|

Unified |

|

отладочный модуль |

|

|

2 Кб |

-- |

Встроенный |

100 pin TQFP |

|

Unified |

|

отладочный модуль |

|

|

512 байт/- |

512 байт |

1 |

посл. интерфейс, |

100 pin TQFP |

|

RAM |

2 |

таймера, |

|

|

|

6 |

сигналов выборки, |

|

|

|

8 |

I/O, |

|

|

|

отладочный модуль |

|

|

512 байт/- |

512 байт |

Контроллер DRAM, |

0,65 /TLM |

|

|

RAM |

2 UART, |

160 QFP |

|

|

|

2 |

таймера, |

|

|

|

8 |

сигналов выборки, |

|

|

|

8 |

I/О, |

|

|

|

I2C, |

|

|

|

|

отладочный модуль |

|

|

Microcontrollers CISC & RISC

Семейство СoldFire

Факторы успеха семейства ColdFire

•RISC-архитектура

•Высокая производительность

•Переменная длина команд

•Компактный двоичный код

•Развитый отладочный интерфейс

•Поддержка JTAG

•Эффективные режимы энергопотребления

•Разнообразные портативные приложения

Microcontrollers CISC & RISC

Семейства на базе PowerPC

MPC600

МРС700

Процессоры

MPC500

Контроллеры

MPC800

Контроллеры

Портативные компьютеры, настольные системы,серверыВысочайшая производительность(до 350Мгц)

Поддержка ведущих ОС(Unix, MacOS, WinNT)

32 или 64-битовые шины для обеспечения гибкости

МРС505 и МРС509 основаны на PowerPC с плавающей точкой однокристальной периферии

МРС505 является первой реализацией семейства PowerPC

микроконтроллеровОбеспечивает 32-битовые эффективные адреса

Обрабатывает 8-, 16-, 32-разрядные данные целого типа; 32- и разрядные данные с плавающей точкойРазличные контроллерные приложения; системы реального времени

Процессоры основаны на РowerPC с однокристальной периферией

Поддержка функций ЦОС, Ethernet и PCMCIAОсновные реализации:

-портативные приложения (МРС821, МРС823) -недорогая версия МРС860 - МРС801

-недорогие сетевые и коммуникационные приложения - МРС850 -работа в Internet, передача данных (MPC860 - несколько вариантов исполнения)

Microcontrollers CISC & RISC

Ядро RCPU PowerPC

Архитектура POWER - Perfomance Optimization With Enhanced RISC

|

|

|

|

|

К э ш -п а м я т ь к о м а н д |

|

|

|

|

|

|

|

|

||||||

П а м я т ь |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Б л о к |

|

|

|

|

Б л о к |

|

|

|

Б л о к |

|

||||

|

|

|

|

|

п е р е х о д о в |

|

|

ф и к с и р о в а н - |

|

|

п л а в а ю щ е й |

|

|||||||

|

|

|

|

|

|

|

|

|

|

н о й т о ч к и |

|

|

т о ч к и |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

К э ш -п а м я т ь д а н н ы х |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ядро RCPU PowerPC

Состав: -целочисленный блок IU

-блок выполнения переходов BPU -блок плавающей точки FPU -кэши инструкций и данных

|

I-ADDR |

|

|

I-DATA |

|

L-ADDR |

|

L-DATA |

|

||

|

ПЛАНИРОВЩИК |

|

|

|

|

|

|

|

|

||

|

КОМАНД |

|

|

|

|

|

|

|

RCPU |

|

|

|

|

|

|

|

|

|

|

|

|

||

ГЕНЕРАЦИЯ |

БЛОК ПРО- |

ОЧЕРЕДЬ ПРЕД- |

|

|

|

|

|

|

|||

СЛЕДУЮЩЕ- |

ЦЕССОРА |

ВЫБОРКИ |

|

|

|

|

|

|

|||

ГО АДРЕСА |

ПЕРЕХОДОВ |

КОМАНД |

|

|

|

|

|

|

|

||

|

ШИНА УПРАВЛЕНИЯ |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

ДАННЫЕ С |

FRP |

FRP |

FPU |

|

|

|

|

|

|

|

|

ПЛАВАЮ- |

(32X64) |

ИСТОРИИ |

|

РЕГИСТРЫ |

GPR |

|

GPR |

IMUL/ |

ALU/ |

АДРЕСА |

ЦЕЛЫЕ |

ЩЕЙ |

|

|

|

|

ТОЧКОЙ |

|

|

|

|||||||

УПРАВ- |

(32X32) |

ИСТРИИ |

IDIV |

BFU |

ЗАГРУЗКИ/ |

ДАННЫЕ |

ЗАГРУЗКИ/ |

|

|

|

|

ЛЕНИЯ |

|

|

|

|

|

ХРАНЕНИЯ |

ЗАГР./ХРАН. |

ХРАНЕНИЯ |

|

|

|

|

|

ШИНЫ ИСТОЧНИКА |

|

|

|

|

|

|

|

||

|

(4СЛОТА/ТАКТ) |

|

|

|

|

|

|

|

|||

Состав: -целочисленный блок IU

-блок выполнения переходов BPU -блок плавающей точки FPU -блок загрузки/хранения LSU

-кэши инструкций и данных (в ядро не входят)

Microcontrollers CISC & RISC

|

|

Семейство МК МРС500 |

||

Однокристальная |

Однокристальная |

МРС505 |

||

|

периферия |

периферия |

|

|

Внутримодульная шина 2 (IMB2) |

|

|

|

|

|

Блок управления периферией (PCU) |

|

|

|

|

Порт Q |

|

|

|

|

Контроллер прерываний |

|

|

|

|

Программный Watchdog |

Системный |

||

|

L-шина/ IMB2 интерфейс (LIMB) |

|||

|

|

блок (SIU) |

||

|

|

|

|

|

RISC- |

Внутренняя L-шина |

|

|

|

|

|

|

|

|

процессор |

4К байт |

|

Chip selects |

|

MCU (RCPU) |

Внутренняя |

Ports |

||

|

SRAM |

|

PIT/DEC |

|

|

|

шина команд (I-шина) |

Clocks |

|

|

|

|

||

|

|

|

Debug |

|

|

|

4К байт |

|

EBI |

|

|

|

|

|

Поддержка |

|

Кэш команд |

|

Порт |

|

|

|

||

разработки |

|

|

|

|

|

|

|

разработки |

|

|

|

|

|

|

Microcontrollers CISC & RISC

|

|

|

|

|

|

|

|

Семейство МРС800 |

||

|

|

|

|

CPU |

SIM |

|

|

Устройство системной |

|

|

|

|

|

4К I-кэш |

|

|

|

|

|||

Шина |

|

|

|

|

|

|

|

интеграции |

|

|

Power PC |

ЯДРО |

|

IMMU |

|

|

|

|

Контроллер памяти |

|

|

|

|

|

|

|

|

|

|

|||

|

PowerPC |

|

|

|

|

|

|

Внутреннее |

Внешнее |

|

|

|

|

|

|

|

|

|

BIU |

BIU |

|

|

|

|

4К D-кэш |

|

|

|

Системныефункции |

|

||

|

|

|

|

|

|

|

|

|

||

|

|

|

DMMU |

|

|

|

|

Часыреальноговремени |

MPC860 |

|

|

|

|

|

|

|

|

Интерфейс сокетаPCMCIA |

|||

|

|

|

|

|

|

|

|

Управление |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CPM |

|

|

|

|

|

|

Параллельный В/В |

5K |

Контроллер |

4 |

|

16 каналов |

|

|

||

|

Генератор |

RAM |

прерываний |

Таймера |

SDMA |

|

|

|||

В/В |

|

|

|

|

2 Виртуальны[ |

|

|

|||

Параллельный порт |

32-битный |

|

RISC |

|

IDMA |

|

|

|||

|

|

|

|

|

||||||

|

|

|

|

|

|

|

||||

|

интерфейса |

микроконтроллер |

MAC |

|

|

|

МРС860 |

|

||

|

|

|

ипрограммноеПЗУ |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|||

|

SCC |

SCC2 |

SCC3 |

SСC4 |

SMC |

SMC2 |

SPI |

2 |

|

|

|

IC |

|

|

|||||||

|

|

|

|

|

|

Последовательный интерфейс |

|

|||

|

Распределитель временных |

Распределительвременных |

|

|

|

|||||

|

|

слотовА |

|

|

слотовВ |

|

|

|

|

|

Microcontrollers CISC & RISC