- •Санкт-Петербургский государственный электротехнический университет «лэти»

- •Логические элементы

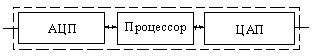

- •Структурная схема системы сбора данных

- •Датчики

- •29.09.07 Задача

- •Оцифровка

- •Ацп параллельного преобразования

- •Сигма-Дельта ацп

- •Ацп последовательного типа

- •Ацп двойного интегрирования

- •6.10.07 Типичный измерительный канал. Фильтры

- •Интерфейсы

- •13.10.07 Задача

- •Способы организации интерфейсов ацп или цап

- •Протокол

- •Параллельный и последовательный интерфейсы

- •20.10.07 Последовательная передача данных

- •Программа, позволяющая прибору общаться с компьютером

- •Работа приборов без участия компьютера Микроконтроллер

- •27.10.07

- •Архитектуры микроконтроллера

- •Архитектура компьютера

- •Интерфейсы

- •I2c (Inter- Intrgrated Circuit)

- •3.11.07

- •Программа, реализующая сопряжение устройств

- •Spi (Serial peripheral interface)

- •10.11.07 Microwire

- •Jtag (Join Test Action Group)

- •Интегральная среда разработки (ide) микроконтроллеров

- •24.11.07

- •8.12.07 Программируемая система на кристалле

- •Драйвер

- •Примеры:

- •15.12.07 Беспроводное подключение измерительных устройств

- •Bluetooth

- •Компьютерные пакеты графического моделирования измерительных устройств

Архитектуры микроконтроллера

CISC (Complex Instruction Set Computer)

RISC (Reduced Instruction Set Computer)

Архитектура компьютера

- Гарвардская

- Фон-Нейманская

Архитектура фон Неймана

Это принцип совместного хранения программ и данных в памяти компьютера. Когда говорят о данной архитектуре, подразумевают физическое отделение процессорного модуля от устройств хранения программ и данных

Гарвардская архитектура

Типичные операции (сложение и умножение) требуют от любого вычислительного устройства нескольких действий: выборку 2-х операндов, выбор инструкции и ее выполнение, сохранение результата. Идея заключалась в физическом разделении линии передачи команд и данных (здесь присутствует отдельная шина для данных)

![]()

При выборе оцениваются следующие параметры:

- система команд

- архитектура

- частота

- стоимость

- встроенный (невстроенный)

- количество портов

- объем памяти (сегодня появилась кэш-память, она «ближе» к процессору)

- температурный режим работы

- техническая поддержка (microchip.ru)

Отличие сигнального процессора (DSP) от микроконтроллера

- вычислительная мощь

DSP (Digital Signal Processor):

ASIC-DSPспециального назначения.

Также в схему на рис.47 входит аналоговый компаратор.

![]()

Порт: регистр состояния, регистр данных, регистр регулирования.

Двунаправленный порт- комбинация проводов и регистров

Каждый порт- 8-разрядный регистр.

Интерфейсы

I2c (Inter- Intrgrated Circuit)

Задачей появления шины I2Cявлялось перейти от параллельной передачи данных, неизбежно имеющей число проводников равное разрядности шины к последовательной передаче данных по 3-м проводам. В стандартном режиме шина обеспечивает передачу последовательных 8-битных данных со скоростью до 100 кбит/с. Для осуществления процесса обмена информацией по шинеI2Cиспользуется всего два сигнала: линия данныхSDA, линия синхронизацииSCL

I2C– последовательный синхронный интерфейс для соединения компонентов (АЦП, ЖКИ, микроконтроллера).

4 режима работы при организации обмена данными:

1) полный дуплекс

![]()

Дуплексный режим позволяет вести передачу и прием одновременно в двух встречных направлениях.

2) полудуплексный

![]()

Полудуплексный режим позволяет выполнять поочередный обмен данными в обоих направлениях. В каждый момент времени передача может вестись только в одном направлении: один передает, другой принимает. И пока передача не закончилась, принимающий ничего не может сообщить передающему

3) однодуплексный

![]()

В симплексном режиме передача данных может вестись только в одном направлении: один передает, другой принимает

Скорость передачи 80 Кбит/сек.

В I2C7 бит, что соответствует 128 устройствам (т.к. ширина адреса 7 бит).

Если ширина адреса 10 бит, тогда можно адресовать 2^10= 1024 устройств.

Рис.48

вывод для данных

провод для «клоков»

Условия передачи: «старт» и «стоп»

«Старт»

Процедура обмена начинается с того, что формируется состояние «Старт»- генерируется переход сигнала линии SDAиз высокого состояния в низкое при высоком уровне на линииSCL. Этот переход воспринимается всеми устройствами , подключенными к шине, как признак начала процедуры обмена.

Рис.49

т.е.

на 2 провода подаются 1 и 1. Питание: 5В

т.е.

на 2 провода подаются 1 и 1. Питание: 5В

2) «Стоп»

Обмен завершается тем, что формируется состояние «Стоп» - переход состояния линии SDAиз низкого состояния в высокое при высоком состоянии линииSCL(см рис.49, но наоборот):SDA=0,clockменяется от 0 до 1.

Состояния «Старт» и «Стоп» всегда вырабатываются ведущим. Считается, что шина занята после фиксации состояния «Старт», свободна- через некоторое время после фиксации состояния «Стоп».