- •Санкт-Петербургский государственный электротехнический университет «лэти»

- •Логические элементы

- •Структурная схема системы сбора данных

- •Датчики

- •29.09.07 Задача

- •Оцифровка

- •Ацп параллельного преобразования

- •Сигма-Дельта ацп

- •Ацп последовательного типа

- •Ацп двойного интегрирования

- •6.10.07 Типичный измерительный канал. Фильтры

- •Интерфейсы

- •13.10.07 Задача

- •Способы организации интерфейсов ацп или цап

- •Протокол

- •Параллельный и последовательный интерфейсы

- •20.10.07 Последовательная передача данных

- •Программа, позволяющая прибору общаться с компьютером

- •Работа приборов без участия компьютера Микроконтроллер

- •27.10.07

- •Архитектуры микроконтроллера

- •Архитектура компьютера

- •Интерфейсы

- •I2c (Inter- Intrgrated Circuit)

- •3.11.07

- •Программа, реализующая сопряжение устройств

- •Spi (Serial peripheral interface)

- •10.11.07 Microwire

- •Jtag (Join Test Action Group)

- •Интегральная среда разработки (ide) микроконтроллеров

- •24.11.07

- •8.12.07 Программируемая система на кристалле

- •Драйвер

- •Примеры:

- •15.12.07 Беспроводное подключение измерительных устройств

- •Bluetooth

- •Компьютерные пакеты графического моделирования измерительных устройств

3.11.07

Рис.50

I2Cпозволяет подключать 5 -6 устройств на одной плате.

АСК- acknowledge

Программа, реализующая сопряжение устройств

Undersat( );

Assert( );

TTL 5B

Release( ); - работает как ключ (переход из 0 в 1)

Delay…( );

I2C Master Data send ( );

(I2C Master Data receive ( );)

I2CMasterADDRsetup( ); - определяет как соединить микроконтроллер с датчиком, АЦП и т.д.

#define…. – здесь все функции, осуществляет обращение по адресу

Условие «стоп»:

Если шина адреса 7 бит (10бит), то теоретически можно подключить 128 устройств (1024 устройства).

Недостатки:

- плохая помехоустойчивость

Для работы с I2C–параллельный порт:

Рис.51

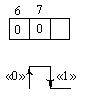

Рис.52. Двухбитный выходной порт

Рис.53. Двухбитный входной порт (2 линии данных)

Рис.54.

На рис.54 «1» и «1» на вход для прохождения импульса.

Spi (Serial peripheral interface)

SPI- последовательный периферийный интерфейс, обеспечивающий высокоскоростной синхронный обмен данными между микроконтроллерами и периферийными устройствами. Его легко программировать. Применяется в мобильных телефонах. Скорость передачи- 10 Мбайт/сек.

Основные характеристики SPI интерфейса:

полнодуплексный 3-проводный синхронный обмен данными,

режим работы ведущий или ведомый,

обмен данными с передаваемыми первыми старшим или младшим битами,

4 программируемые скорости обмена данными,

Флаг прерывания по окончании работы,

Активация из Idle режима

Соединения между ведущим и ведомым CPU, использующими SPI интерфейс показано ниже. Вывод PB1(SCK) является выходом тактового сигнала ведущего микроконтроллера и входом тактового сигнала ведомого. По записи ведущим CPU данных в SPI регистр начинает работать тактовый генератор SPI и записанные данные сдвигаются через вывод выхода PB2(MOSI) ведущего микроконтроллера на вывод входа PB2 (MOSI) ведомого микроконтроллера. После сдвига одного байта тактовый генератор SPI останавливается, устанавливая флаг окончания передачи (SPIF). Если в регистре SPCR будет установлен бит разрешения прерывания SPI (SPIE), то произойдет запрос прерывания. Вход выбора ведомого PB0(SS), для выбора индивидуального SPI устройства в качестве ведомого, устанавливается на низкий уровень. При установке высокого уровня на выводе PB0(SS) порт SPI деактивируется и вывод PB2(MOSI) может быть использован в качестве вывода входа. Режим ведущий/ведомый может быть установлен и программным способом установкой или очисткой бита MSTR в регистре управления SPI.

При разрешенном SPI направления данных выводов MOSI, MISO, SCK и SS настраиваются в соответствии со следующей таблицей:

Вывод Направление, ведущий SPI <Направление, ведомый SPI/b>

MOSI Определяется пользователем Вход

MISO Вход Определяется пользователем

SCK Определяется пользователем Вход

S S Определяется пользователем Вход

Рис.55

MOST, MISO – передача данных (M- master, S- slave, O- out);

SCKL- передача clock;

CS(Cheap/Select) – адрес.

Существуют 4 мода работы: 0 и 0 (см рис.56), 0 и 1, 1 и 1, 1 и 0

Рис.56

Передача осуществляется по фронту или по спаду (см рис.56 (нижний)).

SPIможет использоваться какI2C.

Сопряжение двух приборов:

Сопряжение трех: