- •Лабораторная работа №2 Исследование комбинационных схем.

- •1. Краткие теоретические сведения.

- •2. Типовые комбинационные схемы.

- •2.1 Дешифратор (декодер)

- •2.1.1 Создание принципиальной схемы

- •2.1.2 Проверка работоспособности схемы

- •2.1.3 Реализация на языке vhdl

- •2.2 Шифратор.

- •2.2.1 Создание принципиальной схемы

- •2.3 Мультиплексор

- •2.4 Демультиплексор

- •3.Задание к работе

- •Содержание отчета

- •Контрольные вопросы

2. Типовые комбинационные схемы.

2.1 Дешифратор (декодер)

Дешифратор (декодер) служит для преобразования n-разрядного позиционного двоичного кода в единичный выходной сигнал на одном из 2n выходов. При каждой входной комбинации сигналов на одном из выходов появляется 1 . Таким образом, по единичному сигналу на одном из выходов можно судить о входной кодовой комбинации. Таблица истинности для декодера с двумя входами изображена в таблице 2.1.

Таблица 2.1 – Таблица истинности двухразрядного дешифратора

x2 |

x1 |

y3 |

y2 |

y1 |

y0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

Для построения схемы декодера по таблице истинности воспользуемся методикой, изложенной выше. Например, устройство должно иметь 4 выхода. Для каждого выхода записываем логическое выражение. На основе СДНФ:

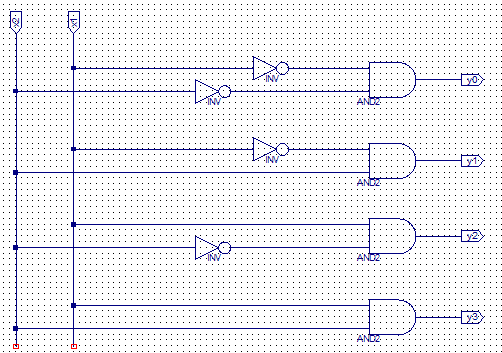

По этой системе выражений несложно построить схему требуемого дешифратора (рис.4).

Рис. 4 – схема дешифратора

Условное графическое изображение дешифратора (рис.5).

Рис. 5

2.1.1 Создание принципиальной схемы

В первую очередь следует запустить программу Xilinx. Создадим новый проект, задаем название FPGA_lab2. Вызываем мастер создания нового источника New Source Wizard, чтобы создать новую схему Schematic, необходимую для дальнейшей работы. Зададим имя нового модуля, File name – DC.

Нарисуем принципиальную схему дешифратора (рис.6).

Рис. 6

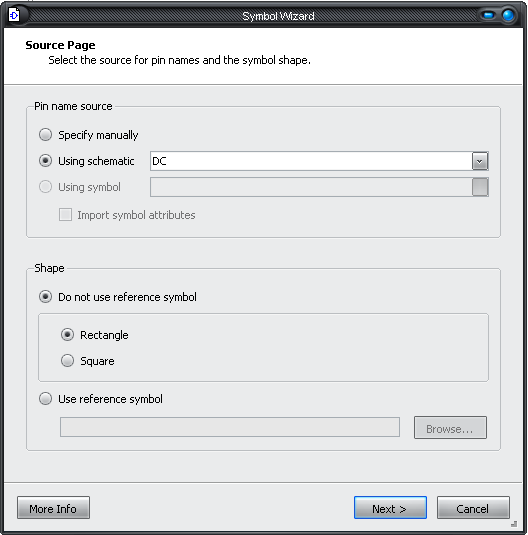

Теперь нам необходимо представить данную схему дешифратора в виде отдельного элемента, назовём его DC. На главной панели выбираем вкладку ToolsSymbol WizardОткроется окно (рис.7) В строке Using schematic выберем имя элемента – DCNextОткроется окно (рис.8).

Рис. 7

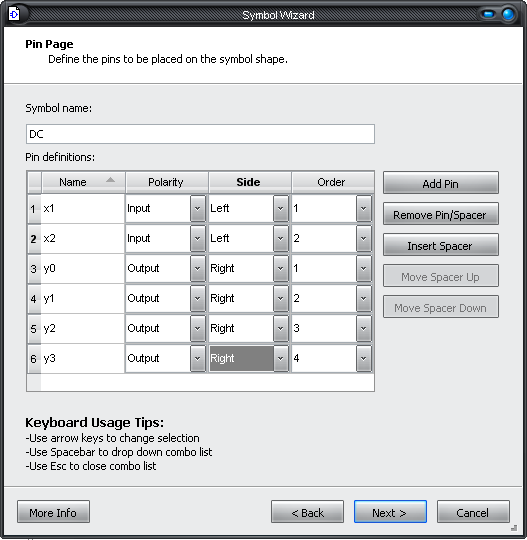

В этом окне нужно задать параметры нашего дешифратора. Нажатием на кнопку Add Pin – добавится новая строка в которой можно задать параметры входной или выходной ножки. Нажмём на эту кнопку шесть раз, т.к у нас две входных и четыре выходных ножки. Зададим параметры (рис.8).

Рис. 8

Важно чтобы порядок расположения входных и выходных ножек был выбран в правильной последовательности. Далее нажимаем NextFinish элемент создан (рис.9).

Новый элемент добавился в библиотеку элементов, и теперь мы можем его использовать в любой схеме.

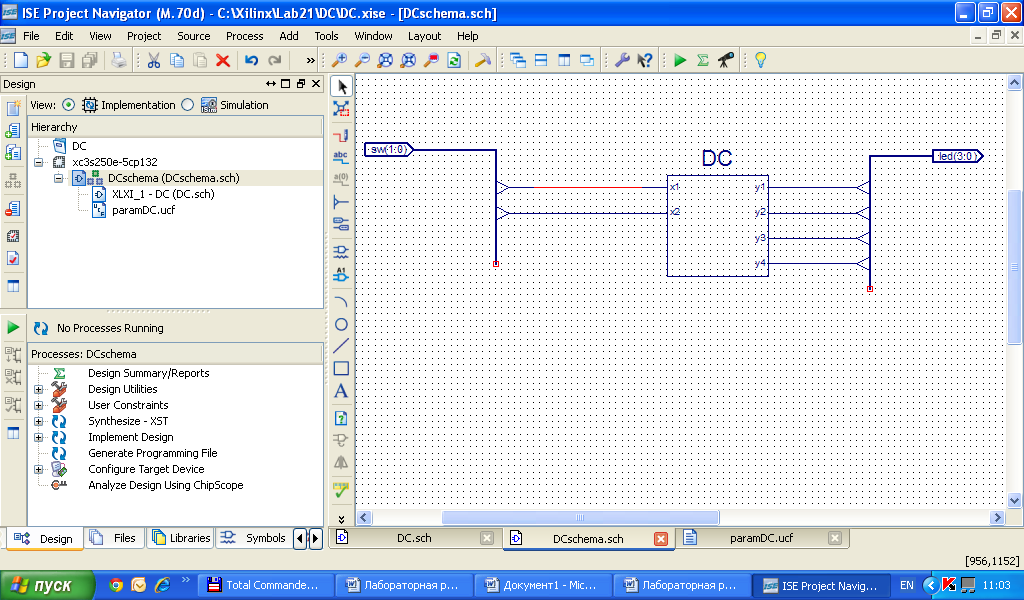

Рис. 9

Вызываем мастер создания нового источника New Source Wizard, чтобы создать новую схему Schematic, необходимую для дальнейшей работы. Зададим имя нового модуля, File name –Lab2_schema. Начертите схему (рис.10).

Рис. 10

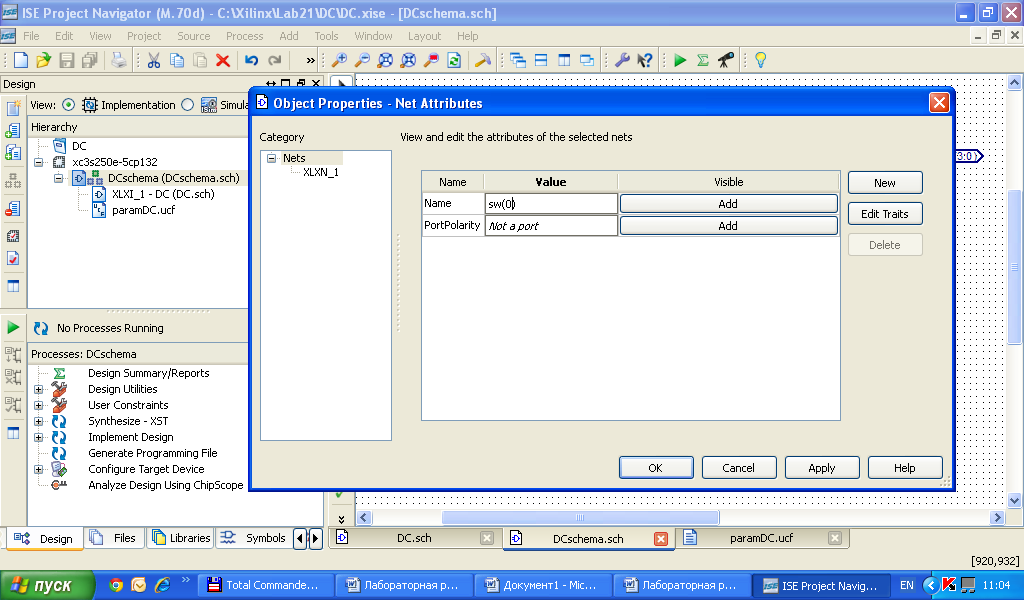

После создания схемы необходимо обозначить каждый проводник, подходящий к шинам sw(1:0) и led(3:0) (рис.11).

Рис.11 Обозначение проводников, подходящих к общим шинам.

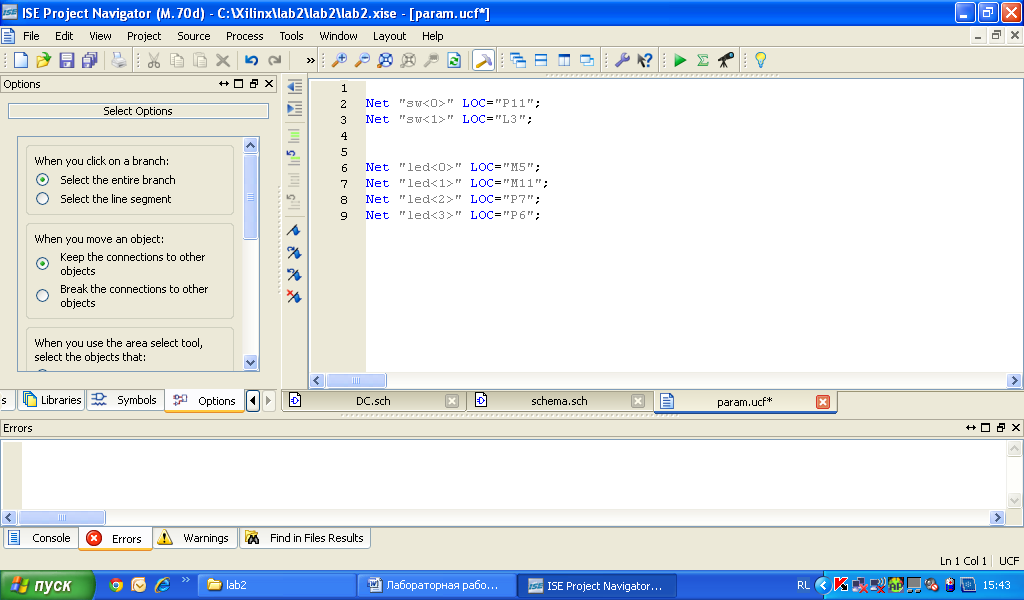

Теперь осталось создать файл param с расширением *.ucf. В нём опишем привязку выводов проекта к входам-выводам кристалла. Пропишем в нём следующие строки (рис.12).

Рис. 12. Описание схемы.

Далее проведём запуск автоматизированного размещения проекта в кристалле и анализ генерируемых отчетов для выявления предупреждений и ошибок, а при отсутствии таковых и не критичных переходим к следующему этапу. Верификация проекта, т. е. окончательное временное моделирование (Post-Fit Simulation) после размещения проекта в кристалле при всех реальных задержках распространения сигналов внутри микросхемы ПЛИС.

В окне

Hierarchy

выбирается проект, а в области окна

процессов (Processes) нужно запустить

Implement

Top

Module

![]() .

Происходит автоматизированное размещение

проекта в кристалле (Implement Disign) и запуск

генерации программируемого файла.

.

Происходит автоматизированное размещение

проекта в кристалле (Implement Disign) и запуск

генерации программируемого файла.