- •Краткие сведения о системе автоматизированного проектирования цифровых устройств – Xilinx ise.

- •Программируемые логические интегральные схемы

- •Система автоматизированного проектирования Xilinx ise.

- •2. Создание проекта

- •2.2. Создание принципиальной схемы.

- •3. Проверка работоспособности схемы

- •Реализация на языке vhdl

- •Содержание отчета

- •Контрольные вопросы

Лабораторная работа №1

«Исследование логических элементов на основе программируемых логических интегральных схем (ПЛИС) в среде Xilinx ISE»

Цель работы: Изучить принципы создания компьютерных моделей цифровых схем, их анализа и реализации на ПЛИС. Исследовать принцип работы логических элементов. Составить таблицы истинности для логических элементов согласно заданию. Реализовать схему на языке программирования VHDL.

Краткие сведения о системе автоматизированного проектирования цифровых устройств – Xilinx ise.

Программируемые логические интегральные схемы

Программируемые логические интегральные схемы – ПЛИС являются одними из самых перспективных элементов цифровой схемотехники. ПЛИС представляет собой кристалл, на котором расположено большое количество простых логических элементов. Изначально эти элементы не соединены между собой. Соединение элементов осуществляется с помощью электронных ключей, расположенных в этом же кристалле. Электронные ключи управляются памятью, в ячейки которой заносится код конфигурации цифровой схемы. Таким образом, записав в память ПЛИС определенные коды, можно собрать цифровое устройство любой степени сложности. В отличие от микропроцессоров, в ПЛИС можно организовать алгоритмы цифровой обработки на аппаратном (схемном) уровне. При этом быстродействие цифровой обработки резко возрастает. Достоинствами технологии проектирования устройств на основе ПЛИС являются:

минимальное время разработки схемы;

в отличие от обычных элементов цифровой схемотехники, отпадает необходимость в разработке и изготовлении сложных печатных плат;

быстрое преобразование одной конфигурации цифровой схемы в другую (замена кода конфигурации схемы в памяти);

для создания устройств на основе ПЛИС не требуется сложное технологическое производство. ПЛИС конфигурируется с помощью персонального компьютера на столе разработчика.

В зависимости от сложности решаемых задач, выбирается тот, или иной тип ПЛИС. Если требуется не большое число триггеров и эквивалентное число вентилей, то подходит CPLD или младшие серии FPGA. Для более крупных проектов практически выбираются кристаллы FPGA большей емкости по числу триггеров и эквивалентных вентилей, иногда требуется использовать несколько кристаллов в проекте.

Система автоматизированного проектирования Xilinx ise.

Одним из мировых лидеров по производству ПЛИС является фирма Xilinx. Для создания цифровых устройств на основе своих изделий, Xilinx разработала специальную программную среду Xilinx ISE. Эта среда позволяет:

с помощью графического редактора ввести в память персонального компьютера электрическую схему;

проверить работоспособность и исправить ошибки;

определить параметры и характеристики разработанного устройства;

сформировать файл конфигурации для конкретного вида ПЛИС;

загрузить полученный файл в память интегральной схемы.

2. Создание проекта

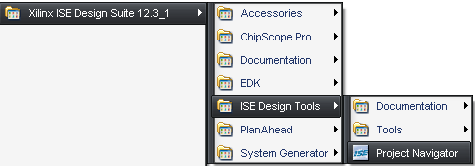

2.1. Работа в среде Xilinx ISE начинается с создания проекта. В первую очередь следует запустить программу Xilinx. Пусквсе программы Xilinx ISE Design 12.3_1 ISE Design Tools Project Navigator (рис.1.)

Рис.1. Запуск программы Xilinx ISE

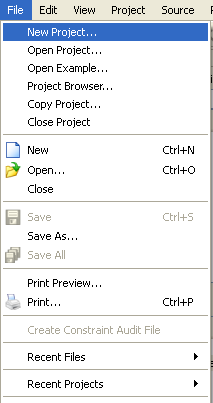

Открыв пакет, Xilinx ISE выбираем из меню File пункт New Project - мастер создания новых проектов (рис.2).

Рис.2. Создание нового проекта.

В открывшемся окне New Project Wizard в поле Name задаем название проекту FPGA_lab1 и указываем папку для хранения файлoв проекта в поле Project Location. Имя папки и проекта желательно вводить латинскими буквами. В поле Top – Level Source Type выбираем тип проектирования Schematic и переходим к следующему этапу - Next (рис. 3.)

Рис.3. Окно New Project Wizard.

В появившемся окне Project Settings выбираем тип ПЛИС, используемой в проекте (рис.4.) В строке Family выбираем Spartan3E, а в строке Device – XC3S250E.

Рис. 4. Начальные настройки проекта.

В итоге получаем отчет о проделанной работе и нажимаем на кнопку Finish.

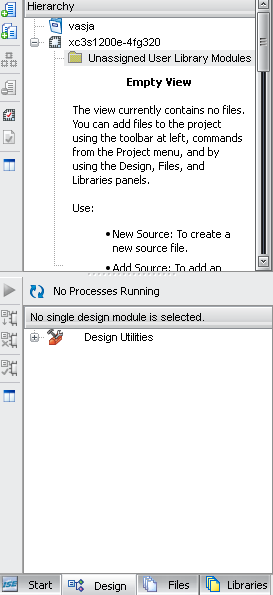

Для создания нового проекта используется следующая панель. На этой панели выбираем вкладку –Design (рис.5.)

Рис.5

Вызываем

мастер создания нового источника New

Source,

чтобы создать новую схему Schematic,

необходимую для дальнейшей работы. Для

вызова данного мастера нужно в окне

Hierarchy

навигатора проекта правой кнопкой мыши

нажать на Unassigned

User

Library

Modules

и в появившемся окне диалога выбрать

New Sources(или кнопка![]() )

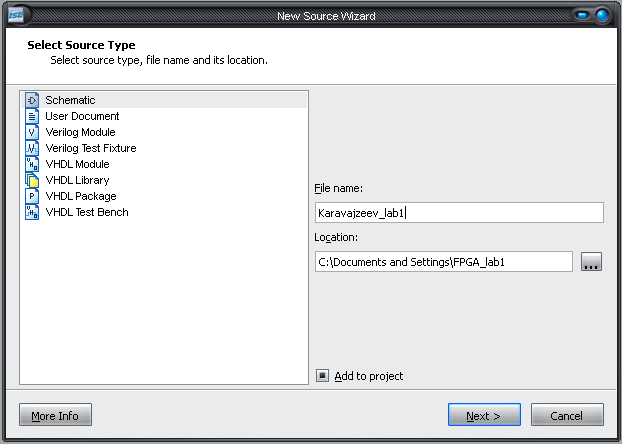

Schematic

File nameВводится

имя создаваемого модуля (Фамилия_lab1).

Галочку Add

to

project

оставляем (рис.6.)

)

Schematic

File nameВводится

имя создаваемого модуля (Фамилия_lab1).

Галочку Add

to

project

оставляем (рис.6.)

Рис. 6. Добавление проекта.

Нажимаем на кнопку Next, после чего появляется итоговое окно, где нажимаем на кнопку Finish.

В дальнейшем автоматически открывается окно схемотехнического редактора (FPGA Editor) принципиальных схем входящий в состав навигатора проекта (Project Navigator).

При этом в окне навигатора проекта (Project Navigator) в области окна(Hierarchy) появится созданный файл с расширением *.sch, в который будут добавляться и пополняться различными файлами и модулями по мере их создания в дальнейшем.