- •Методические указания к комплексному курсовому проекту / Составители: в.Г. Лобода, а.С. Шкиль, е.Е. Сыревич.- Харьков, хнурэ, 200___. – 8 с. Введение

- •1 Цели и задачи курсового проектирования. Тематика курсовых проектов. Общие вопросы организации комплексного курсового проектирования

- •Этапы процесса проектирования

- •Традиционная методика проектирования

- •Анализ методики проектирования с использованием современной элементной базы

- •3. Общая структура проекта

- •4. Методические указания к выполнению курсового проекта

- •Математическое моделирование;

- •Выбор схемотехнического решения;

- •Спецификация всего устройства.

поиск готовых решений;

выбор семейства кристалла;

Математическое моделирование;

Выбор схемотехнического решения;

Спецификация всего устройства.

Поиск готовых решений нам не принес никакого результата, поэтому мы проектируем данное устройство по известному нам алгоритму. Так как устройство простое, то мы не используем никаких программ для математического моделирования.

4.2.1 Спецификация всего устройства

В таблице 4.3 приведены данные для определения коэффициента деления частоты при помощи старших четырех бит информационной последовательности.

Таблица 4.3 – Коэффициенты деления частоты

N |

Ki |

Nki |

1 |

1011 |

0001 |

2 |

999 |

0010 |

3 |

820 |

0100 |

4 |

733 |

0101 |

5 |

645 |

1000 |

6 |

551 |

1001 |

7 |

483 |

1010 |

Формат слова – CNkiNj, где С – бит четности, Nki – старшие четыре разряда слова, Nj – младшие четыре разряда слова.

Ki – коэффициент деления частоты.

n1 – число бит, необходимых для представления коэффициента деления частоты в двоичной системе исчисления.

n2 – разрядность выходной импульсной последовательности.

m – число одноразрядных коммутирующих импульсов.

n1=10; n2=7;m=8.

В таблице 4.4 представлены данные для коммутатора импульсов, где Код – m-разрядная последовательность.

Таблица 4.4 – Данные для коммутатора импульсов

N |

Nj |

Код |

1 |

0110 |

1000111 |

2 |

0111 |

0111000 |

3 |

0101 |

1100110 |

4 |

1000 |

1110011 |

5 |

1001 |

0101100 |

6 |

1100 |

1111000 |

7 |

0011 |

0001111 |

8 |

0010 |

1010101 |

Интерфейс данного проектируемого устройства приведен ниже, на рисунке 4.1.

Рисунок 4.1 - Интерфейс проектируемого устройства

4.2.2 Выбор семейства кристалла

FPGA имеет типичную структуру вентильной матрицы. На рис. 4.2 представлен FPGA фирмы Xilinx – Spartan II (модель XC2S15).

ПЛИС типа FPGA фирмы Xilinx выполнены по SRAM КМОП технологии. Характеризуются высокой гибкостью структуры и изобилием на кристалле триггеров. При этом логика реализуется посредством матрицы так называемых LUT – таблиц (Look Up Table), а внутренние межсоединения – посредством разветвлённой иерархии металлических линий, коммутируемых специальными быстродействующими транзисторами.

Большая стоимость микросхем FPGA с встроенной RAM по сравнению со стоимостью заказных микросхем ограничивает использование FPGA для изготовления опытных образцов или мелкосерийной продукции. Этот недостаток FPGA устранен фирмой Xilinx выпуском новой серии микросхем FPGA – серий Spartan и Spartan-II, параметры которых приведены в таблице 4.3.

Таблица включает шесть устройств серии Spartan-II и их основные характеристики (логические ячейки, число системных вентилей, размерность массива CLB, кол-во CLB и др.).

Таблица 4.5 – Параметры семейства FPGA Spartan2

Device |

Logic Cells |

System Gates (Logic and RAM) |

CLB Array (C*R) |

Total CLBs |

Maximum Available User I/O |

Total Distributed RAM Bits |

Total Block RAM Bits |

XC2S15 |

432 |

15000 |

8*12 |

96 |

86 |

6144 |

16K |

XC2S30 |

972 |

30000 |

12*18 |

216 |

132 |

13824 |

24K |

XC2S50 |

1728 |

50000 |

16*24 |

384 |

176 |

24576 |

32K |

XC2S100 |

2700 |

100000 |

20*30 |

600 |

196 |

38400 |

40K |

XC2S150 |

3888 |

150000 |

24*36 |

864 |

260 |

55296 |

48K |

XC2S200 |

5292 |

200000 |

28*42 |

1176 |

284 |

75264 |

56K |

Семейство FPGA Spartan-II имеет рекордно низкую стоимость в расчете на один вентиль при плотности упаковки до 200 тысяч вентилей. В кристалле имеется несколько блоков ОЗУ каждый по 4КБита, также возможна реализация 16 бит памяти на каждом 4-х входовом функциональном генераторе.

Устройства Spartan-II сочетают черты гибкой, регулярной архитектуры, которая охватывает матрицу конфигурируемых логических блоков (CLB), окруженную программируемыми блоками ввода - вывода, связанных между собой богатой иерархией быстрых, многосторонних ресурсов межсоединений.

Изобилие таких ресурсов позволяет семейству Spartan-II реализовывать чрезвычайно громоздкие и сложные проекты.

Устройства Spartan-II имеют более высокую производительность по сравнению с предыдущими семействами FPGA. Проекты могут работать с системной частотой синхронизации до 200 МГц, включая блоки ввода/вывода (Input/Output – I/O).

Кроме этого чипы Spartan-II отличает целый ряд достоинств:

низкая стоимость разрабатываемых устройств

высокая скорость проектирования

большая размерность чипа (до 200,000 системных вентилей).

высокое быстродействие

Рисунок 4.2 – Структура кристалла Spartan-II.

Программируемая пользователем вентильная матрица Spartan-II, показанная на рисунке 4.2, охватывает: конфигурируемые логические блоки (configurable logic blocks - CLBs) и блоки ввода - вывода (IOBs). CLB блоки служат для создания функциональных логических элементов, а блоки I/O создают интерфейс между контактами микросхемы и CLB блоками.

Архитектура Spartan-II также включает следующие цепи:

специальные блоки памяти размером 4096 бит каждый;

схемы автоподстройки задержек (DLL) для выравнивания задержек стробирующих сигналов, а также внутреннего управления стробированием.

Базовым строительным элементом CLB блока является логическая ячейка. Логическая ячейка включает 4-х входовой функциональный генератор, логику ускоренного переноса и запоминающий элемент. Выход каждого функционального генератора в каждой логической ячейке подсоединен к выходной линии CLB-блока и к D-входу триггера.

Каждый CLB-блок в серии Spartan-II содержит четыре логические ячейки, организованные в виде двух одинаковых секторов (Slice). На рис. 4.3 один сектор изображен более детально.

В дополнение к четырем базовым логическим ячейкам, CLB-блок серии Spartan-II содержит логику, которая позволяет комбинировать ресурсы функциональных генераторов для реализации функций от пяти или шести входов.

Рисунок 4.3 – Сектор (Slice) FPGA Spartan-II.

Функциональные генераторы реализованы в виде 4-х входовых функциональных таблиц (LUT). Кроме использования в качестве функциональных генераторов, каждый LUT-элемент может быть также использован как синхронная память типа RAM размерностью 16x1 бит. Более того, из двух LUT-элементов в рамках одного сектора (Slice) можно реализовать синхронную RAM-память размерностью 16х2 бита или 32х1 бит, либо двухпортовую синхронную RAM-память размерностью 16х1 бит.

На LUT-элементе микросхемы Spartan-II может быть реализован 16-битный сдвиговый регистр, который идеально подходит для захвата высокоскоростных или пакетных потоков данных. Этот режим может также использоваться для запоминания данных в таких приложениях, как цифровая обработка сигналов (Digital Signal Processing - DSP).

Запоминающие элементы в каждом секторе CLB-блока Spartan-II могут конфигурироваться как динамические триггеры (чувствительные к фронту сигнала) D-типа, либо как защелки, чувствительные к уровню сигнала. D-вход триггера может управляться либо от функционального генератора в рамках того же сектора CLB-блока, либо непосредственно от входов данного сектора.

Мультиплексор F5 в каждом секторе объединяет выходы преобразователя. Эта комбинация позволяет реализовать любую функцию 5-ти переменных или некоторые функции до девяти переменных. Точно так же мультиплексор F6 объединяет выходы изо всех четырех LUTов в CLB. Это позволяет реализацию любой функции 6-ти переменных или некоторые функции до 19 переменных. У каждого CLB имеется четыре, прямых пути. Эти пути обеспечивают дополнительные линии ввода данных или дополнительную маршрутизацию, которая позволяет сэкономить логические ресурсы.

Специальная логика переноса обеспечивает возможность быстрого переноса при реализации арифметических функций. CLB-блок Spartan-II поддерживает две отдельные цепочки переноса, одна на каждый сектор (Slice) CLB. Размерность цепочек переноса – два бита на CLB-блок.

В FPGA Spartan-II встроена особая блочная память. Она создана в дополнение к распределенной памяти небольшой емкости (Select RAM), реализованной на функциональных таблицах (Look Up Table RAM – LUTRAM).

Блоки памяти организованы в виде столбцов. Все устройства Spartan-II содержат два таких столбца, по одному вдоль каждой вертикальной кромки. Эти колонки увеличивают полный размер кристалла.

Для реализации выбирается кристалл типа FPGA семейства Spartan-II серии XC2S100-6 фирмы Xilinx.

4.3 Эскизный проект

После анализа технического предложения переходим к следующему этапу проектирования, а именно эскизному проекту. Данные, размером 9 бит, заносятся в регистр (RG), после чего они оттуда поступают на блок проверки на нечетность (mod). Если последовательность четная, то сигналу "ОК" присваивается "1", который запускает генератор импульсов (ГИ). Он, в свою очередь, вырабатывает частоту, равную 65 МГц, которая поступает на управляемый делитель частоты (УДЧ). Старшие 4 разряда слова Nki поступают на шифратор (ШФ), который преобразует поступающие на него данные в последовательность, разрядностью n1, которая и будет являться делителем частоты для УДЧ. С УДЧ частота, деленная на делитель, поступает на распределитель импульсов (РИ). Он служит для последовательной передачи n2 импульсов на формирователь выходных последовательностей, а также сигнала готовности "ГТ". Эти импульсы поступают на блок дизъюнкторов (БД), который предназначен для формирования m выходных последовательностей, которые поступают на коммутатор импульсов (КИ). Он производит коммутацию импульсных последовательностей, поступающих с БД. Выбор той или иной последовательности осуществляется с помощью младших 4 разрядов данных Nj, приходящих от входного регистра (RG).

Рисунок 4.4 – Подробная структурно-блочная схема устройства

4.3.1 Спецификация блоков

Блок «Шифратор». Данный блок выполняет шифрование данных, т.е. на вход поступают старшие разряды слова, с помощью которых определяется коэффициент деления частоты, уменьшенный на единицу. Входные параметры и данные для данного блока представлены в таблицах 4.6 и 4.7 соответственно.

Таблица 4.6 – Входные параметры для блока «Шифратор»

Data |

4- разрядный входной сигнал, предназначенный для определения коэффициента частоты |

DataOut |

9 – разрядный выходной сигнал, который и является двоичным представлением коэффициента частоты уменьшенным на единицу |

Таблица 4.7 – Данные для блока «Шифратор»

N |

Ki |

Nki |

1 |

1011 |

0001 |

2 |

999 |

0010 |

3 |

820 |

0100 |

4 |

733 |

0101 |

5 |

645 |

1000 |

6 |

551 |

1001 |

7 |

483 |

1010 |

Интерфейс данного блока приведен ниже.

Рисунок 4.5 – Интерфейс блока «Шифратор»

Блок «Проверки на нечетность». Данный блок предназначен для проверки на четность данные разрядностью девять бит. Формат данных выглядит следующим образом: формат слова – CNkiNj, где С – бит четности, Nki – старшие четыре разряда слова, Nj – младшие четыре разряда слова. Входные параметры написаны в таблице 4.8.

Таблица 4.8 – Входные параметры для блока «проверки на нечетность»

Data |

9-разрядный сигнал данных, формат которого описан выше |

Error |

битовый сигнал, сигнализирующий о том, что существует ошибка |

OK |

битовый сигнал, сигнализирующий о том, что ошибки нет |

Принцип работы данного устройства определяется формулой

![]()

Интерфейс данного устройства приведен ниже.

Рисунок 4.6 – Интерфейс блока «Проверка на четность»

4.4 Технический проект

Осуществив, все выше изложенные этапы проектирования и проанализировав эскизный проект, мы переходим к следующей стадии проектирования – технический проект, а именно к описанию проекта для ввода в САПР.

Существует несколько способов ввода описания проекта: структурный (в виде схемы из функциональных блоков), автоматный (в виде графа переходов, ГСА и т.д.), кодовый (использую языки описания аппаратуры типа VHDL или Verilog), в виде списка соединений и т.д.

Для моделирования и верификации выбран программный пакет Active-HDL 6.1. Он позволяет автоматизировать процесс ввода проекта и TestBench к нему, а также эффективно осуществлять анализ проектных решений. Помимо прочего у нас не имеется другой более-менее подходящей альтернативы.

Для синтеза проекта выбран программный продукт фирмы Synplicity Synplify 7.0.2, так как он имеет следующие преимущества по сравнению с программами синтеза других производителей:

высокая скорость синтеза (основное);

визуальное представление результатов синтеза (нетлиста);

наличие библиотек под современную элементную базу крупнейших мировых производителей.

Ввод проекта с помощью языкового описания на ЯОА является наиболее гибким вариантом, хотя требует больше времени и знаний специфики используемого ЯОА.

Описание блоков проекта на ЯОА

В качестве ЯОА для описания выбран VHDL. Это обусловлено высокой адаптацией средств языка для нужд проектировщика, наличием эффективной среды моделирования (Active-HDL), а также среды синтеза, использующей VHDL (Synplify).

При описании проекта на языке VHDL удобно представлять сложный проект в виде иерархической структуры, все более детализируя его описание на низших уровнях. Тем самым упрощается процесс написания VHDL-моделей отдельных компонент проекта а также их отладка. После анализа структурно-функциональной схемы была определена иерархия данного проекта, и она представлена на рисунке.

Рисунок 4.7 – Файловая иерархия проекта

Файловая структура содержит: BlackPack.vhdl, gi.vhdl, UDC.vhdl, rasp_imp.vhdl, kod.vhdl, mod2.vhdl, RG.vhdl, kom_imp.vhdl, BlockD.vhdl.

Блок проверки на нечетность. В заголовке объекта проектирования (entity) указаны входные и выходные сигналы данных блока:

Data: std_logic_vector (8 downto 0);

Error: std_logic;

OK: std_logic.

В архитектуре (architecture) реализуется выражение (4.1), а также инверсия выхода Error:

OK<= not (Error) (4.2)

Входные данные описаны, как вектор типа std_logic_vector разрядностью 9 бит.

Старший бит входных данных – бит четности.

Если Error равен “1”, то входные данные нечетны, что остановит действие всего проекта.

Текст программы моделирования приведен в приложении. Результаты моделирования приведены ниже.

Рисунок 4.8 – Результаты моделирования блока проверки на нечетность

Блок “шифратор”. В заголовке объекта проектирования (entity) указаны входные и выходные сигналы данных блока:

Data: std_logic_vector (3 downto 0);

K: std_logic_vector (9 downto 0).

Входные данные Data имеют разрядность 4 бит, так как нам минимально необходимо всего лишь они, с помощью которых мы определяем коэффициент деления частоты. Выходной сигнал К имеет разрядность 10 бит, так как это минимальное число бит необходимое для представления коэффициента деления частоты в двоичной форме.

Архитектура состоит из одного процесса. При описании процесса будем использовать список чувствительности, содержащий все входные сигналы интерфейса устройства, так как временные параметры приостановки процесса отсутствуют. Для реализации выбора нужного коэффициента деления в структуре процесса используем оператор case. Он реализует 8 условий, при котором коэффициент равен определенному числу, представленному в двоичной форме:

when "0001" => K <= "1111110010";

when "0010" => K <= "1111100110";

when "0100" => K <= "1100110011";

when "0101" => K <= "1011011100";

when "1000" => K <= "1010000100";

when "1001" => K <= "1000100110";

when "1010" => K <= "0111100010";

when others => null;

Текст программы моделирования приведен в приложении. Результаты моделирования приведены ниже.

Рисунок 4.9 – Результаты моделирования блока «Шифратор»

Глядя на рисунок 4.9, можно сказать, что данный блок работает правильно.

4.4.2 Описание проекта на ЯОА

Весь проект состоит из множества файлов, которые мы объединяем при помощи одного, BlackPack.vhdl, он то и является верхней частью иерархии. Данный файл состоит из компонентов, которые мы объединяем в один файл с помощью операторов port map, которые и являются связывающими файлы нижней иерархии. Вышеуказанный файл является реализацией на языке описания аппаратуры спецификации всего устройства. Он состоит из entity, в котором описаны все входные и выходные сигналы данного продукта:

Reset: in STD_LOGIC;

Str : in STD_LOGIC;

Data: in STD_LOGIC_VECTOR (8 downto 0);

Ready: out STD_Logic;

OutData: out STD_LOGIC.

Данное описание в данном разделе проекта соответствует его спецификации, поэтому для подробной информации можно посмотреть таблицы 4.1 и 4.2.

Далее идет соединение блоков:

m1: rg port map (Str=>Str, DataRG=>Data, DataOut_RG=>Data_in, Reset=>Reset);

m2: mod2 port map (Str=>Str, Data_mod => Data_in, OK => OK);

m3: GI port map (OK => OK, F => Clk);

N_k1 <= Data_in(7)& Data_in(6)& Data_in(5)& Data_in(4);

N_k2 <= Data_in(3)& Data_in(2)& Data_in(1)& Data_in(0);

m4: Kod port map (Data_Kod => N_k1, K =>D_K);

m5: UDC port map(Clk_in => Clk, K_in => D_K, Clk_out => Clk_out);

m6: Rasp_imp port map(Clk=>Clk_out, Ready=>Ready, DataOut_R =>Data_n2);

m7: BlockD port map(Data_B => Data_n2, DataOut_B => Data_m);

m8: Kom_imp port map(Data_N=>N_k2, Data_BD=>Data_m, DataOut_K=>OutData);

Сигналы N_k1 и N_k2 являются промежуточными, которые приобретают значения старших четырех бит информации и младших соответственно.

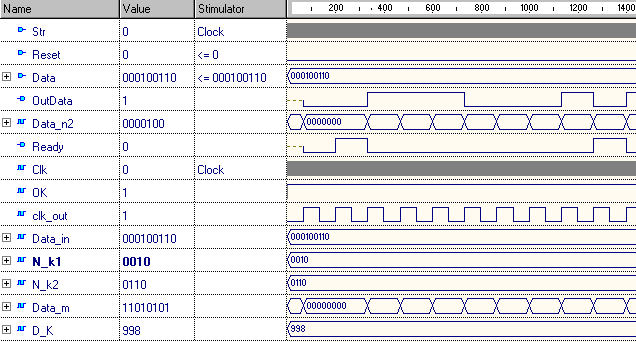

Пример моделирования одного из наборов представлен на рис. 4.10. На вход поступает такой набор – Str (строб ввода), на который поступает сигнал тактовой частоты 65 МГц, Reset (сброс) устанавливает данное устройство в начальное состояния, когда он равен ‘1’, а потом при установлении в ‘0’ данное устройство начинает свою работу, и Data, которые и являются информационными данными, которые заносятся в регистр, после которого данные присваиваются переменной Data_in. Информационные данные поступают на блок проверки на нечетность, и если входные данные являются нечетным числом, то сигнал ОК равен ‘1’, иначе ‘0’. Этот сигнал дает старт для работы генератора импульсов clk с частотой 65 МГц. Импульсы с данной частотой поступают на управляемый делитель частоты. А параллельно с этим информационные данные разделяются на два полубита N_k1 и N_k2.

N_k1 <= Data_in(7)& Data_in(6)& Data_in(5)& Data_in(4);

N_k2 <= Data_in(3)& Data_in(2)& Data_in(1)& Data_in(0);

С помощью сигнала N_k1, который поступает на шифратор, определяется коэффициент деления частоты, D_K. Значение D_K поступает на управляемый делитель частоты, на выходе которого имеем сигнал clk_out, который представляет собой clk/D_K. Теперь с этого момента синхроимпульсом для распределителя является clk_out. После того, как сигнал Ready стал равен ‘1’, это означает то, что распределитель импульсов готов к формированию сигнала Data_n2. Этот сигнал поступает на блок дизъюнкторов, где собственно и формируются импульсные последовательности, результатом его работы является сигнал Data_m. Он поступает на коммутатор импульсов, где при помощи сигнала N_k2 и определяется какой импульсной последовательности и будет равен выходной сигнал OutData.

Рисунок 4.10 – Пример моделирования

Глядя на рисунок 4.10 можно сказать, что данное устройство работает правильно.

Полный текст (в теле пояснительной записки приводить полный текст не надо – его выносят в приложения).

BlackPack.vhdl

library IEEE;

use IEEE.std_logic_1164.all;

entity osn is

port (Reset: in STD_LOGIC;

Str : in STD_LOGIC;

Data: in STD_LOGIC_VECTOR (8 downto 0);

Ready: out STD_Logic;

OutData: out STD_LOGIC);

end osn;

architecture osn of osn is

component Mod2 is

port (Data_Mod: in STD_LOGIC_VECTOR (8 downto 0);

Str : in std_logic;

Error: out Std_logic;

OK: out Std_logic);

end component Mod2;

component Kod is

port (

Data_Kod: in STD_LOGIC_VECTOR (3 downto 0);

K: out STD_LOGIC_VECTOR (9 downto 0));

end component Kod;

component UDC is

port(K_in : in std_logic_vector(9 downto 0);

clk_in: in std_logic;

clk_out: inout std_logic := '0');

end component UDC;

component RG is

port (Reset:in std_logic;

Str:in Std_logic;

DataRG: in STD_LOGIC_VECTOR (8 downto 0);

DataOut_RG: out STD_LOGIC_VECTOR (8 downto 0));

end component RG;

component GI is

port ( Ok: in Std_logic;

F: buffer Std_logic);

end component GI;

component Rasp_imp is

port(Clk : in STD_LOGIC;

Ready : out STD_LOGIC;

DataOut_R : out STD_LOGIC_VECTOR(6 downto 0));

end component Rasp_imp;

component BlockD is

port (Data_B: in STD_LOGIC_VECTOR (6 downto 0);

DataOut_B: out STD_LOGIC_VECTOR (7 downto 0));

end component BlockD;

component Kom_imp is

port (Data_N: in STD_LOGIC_VECTOR (3 downto 0);

Data_BD: in STD_LOGIC_VECTOR (7 downto 0);

DataOut_K: out STD_LOGIC);

end component Kom_imp;

signal Clk, OK, Clk_out : std_logic;

signal Data_in : std_logic_vector (8 downto 0);

signal N_k1, N_k2 : std_logic_vector (3 downto 0);

signal Data_n2 : std_logic_vector (6 downto 0);

signal Data_m : std_logic_vector (7 downto 0);

signal D_K : STD_LOGIC_VECTOR (9 downto 0);

begin

m1: rg port map (Str=>Str, DataRG => Data, DataOut_RG => Data_in, Reset => Reset);

m2: mod2 port map (Str=>Str, Data_mod => Data_in, OK => OK);

m3: GI port map (OK => OK, F => Clk);

N_k1 <= Data_in(7)& Data_in(6)& Data_in(5)& Data_in(4);

N_k2 <= Data_in(3)& Data_in(2)& Data_in(1)& Data_in(0);

m4: Kod port map (Data_Kod => N_k1, K =>D_K);

m5: UDC port map(Clk_in => Clk, K_in => D_K, Clk_out => Clk_out);

m6: Rasp_imp port map ( Clk => Clk_out, Ready => Ready, DataOut_R =>Data_n2);

m7: BlockD port map(Data_B => Data_n2, DataOut_B => Data_m);

m8: Kom_imp port map(Data_N => N_k2, Data_BD => Data_m, DataOut_K=> OutData);

end osn;

GI.vhdl

library IEEE;

use IEEE.std_logic_1164.all;

entity GI is

generic (Delay : Time := 7.69 ns);

port ( Ok: in Std_logic;

F: buffer Std_logic);

end GI;

architecture arch_GI of GI is

signal Clk : Std_logic :='0';

begin

Clk_1: process

begin

L1: while (Ok='1')loop

F <= Clk;

wait for Delay;

Clk <= not F;

wait for Delay;

end loop L1;

wait on Ok;

end process Clk_1;

end arch_GI;

Mod2.vhdl

library IEEE;

use IEEE.std_logic_1164.all;

entity Mod2 is

port (Str: in STD_logic;

Data_Mod: in STD_LOGIC_VECTOR (8 downto 0);

Error: out Std_logic;

OK: out Std_logic);

end Mod2;

architecture arch_mod2 of Mod2 is

signal NError : std_logic;

begin

process(Str, Data_Mod)

begin

if (Str'Event and Str='1') then

NError <= not( Data_Mod(0) xor Data_Mod(1) xor Data_Mod(2) xor Data_Mod(3) xor Data_Mod(4) xor Data_Mod(5) xor Data_Mod(6) xor Data_Mod(7) xor Data_Mod(8));

end if;

end process;

Error <= NError;

Ok <= not NError;

end arch_mod2;

RG.vhdl

library IEEE;

use IEEE.std_logic_1164.all;

entity RG is

port (Reset: in std_logic;

Str:in Std_logic;

DataRG: in STD_LOGIC_VECTOR (8 downto 0);

DataOut_RG: out STD_LOGIC_VECTOR (8 downto 0));

end RG;

architecture arch_RG of RG is

signal Data : std_logic_vector (8 downto 0);

begin

process(Str, Reset, DataRG)

begin

if Reset='1' then Data <= "000000000";

elsif (Str'event and Str='1') then

Data <= DataRG;

end if;

end process;

Dataout_RG <= Data;

end arch_RG;

Kod.vhdl

library IEEE;

use IEEE.std_logic_1164.all;

entity Kod is

port (Data_Kod: in STD_LOGIC_VECTOR (3 downto 0);

K: out STD_LOGIC_VECTOR (9 downto 0));

end Kod;

architecture arch_kod of Kod is

begin

process (Data_Kod)

begin

case Data_Kod is

when "0001" => K <= "1111110010";

when "0010" => K <= "1111100110";

when "0100" => K <= "1100110011";

when "0101" => K <= "1011011100";

when "1000" => K <= "1010000100";

when "1001" => K <= "1000100110";

when "1010" => K <= "0111100010";

when others => null;

end case;

end process;

end arch_kod;

UDC.vhdl

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use ieee.std_logic_unsigned.all;

entity UDC is

port(K_in : in std_logic_vector(9 downto 0);

clk_in: in std_logic;

clk_out: inout std_logic := '0');

end UDC;

architecture arch_UDC of UDC is

begin

process(clk_in, K_in)

variable rise_count:std_logic_vector(9 downto 0):="0000000001";

begin

if rising_edge(clk_in)then

rise_count:=rise_count+'1';

if rise_count=(K_in+'1') then

rise_count:="0000000001";

clk_out<=not clk_out;

end if;

end if;

end process;

end arch_UDC;

Rasp_imp.vhdl

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use ieee.std_logic_unsigned.all;

entity Rasp_imp is

port(Clk : in STD_LOGIC;

Ready : out STD_LOGIC;

DataOut_R : out STD_LOGIC_VECTOR(6 downto 0));

end Rasp_imp;

architecture arch_imp of Rasp_imp is

signal Data : std_logic_vector (7 downto 0):= "00000000";

begin

process (Clk)

variable d: integer:=7;

begin

if (Clk'event and Clk = '1') then

case d is

when 0 => Data <= "10000000";

when 1 => Data <= "01000000";

when 2 => Data <= "00100000";

when 3 => Data <= "00010000";

when 4 => Data <= "00001000";

when 5 => Data <= "00000100";

when 6 => Data <= "00000010";

when 7 => Data <= "00000001";

when others => Data <= "00000000";

end case;

Ready <= Data(0);

DataOut_R <= Data(7) & Data(6) & Data(5) & Data(4) & Data(3) & Data(2) & Data(1);

d := d - 1;

if d=-1 then d:=7;

end if;

end if;

end process;

end arch_imp;

BlockD.vhdl

library IEEE;

use IEEE.std_logic_1164.all;

entity BlockD is

port (Data_B: in STD_LOGIC_VECTOR (6 downto 0);

DataOut_B: out STD_LOGIC_VECTOR (7 downto 0));

end BlockD;

architecture arch_bd of BlockD is

begin

DataOut_B(0) <= Data_B(6) or Data_B(2) or Data_B(1) or Data_B(0);

DataOut_B(1) <= Data_B(5) or Data_B(4) or Data_B(3);

DataOut_B(2) <= Data_B(6) or Data_B(5) or Data_B(2) or Data_B(1);

DataOut_B(3) <= Data_B(6) or Data_B(5) or Data_B(4) or Data_B(1) or Data_B(0);

DataOut_B(4) <= Data_B(5) or Data_B(3) or Data_B(2);

DataOut_B(5) <= Data_B(6) or Data_B(5) or Data_B(4) or Data_B(3);

DataOut_B(6) <= Data_B(3) or Data_B(2) or Data_B(1) or Data_B(0);

DataOut_B(7) <= Data_B(6) or Data_B(4) or Data_B(2) or Data_B(0);

end arch_bd;

Kom_imp.vhdl

library IEEE;

use IEEE.std_logic_1164.all;

entity Kom_imp is

port (Data_N: in STD_LOGIC_VECTOR (3 downto 0);

Data_BD: in STD_LOGIC_VECTOR (7 downto 0);

DataOut_K: out STD_LOGIC);

end Kom_imp;

architecture arch_kom of Kom_imp is

begin

process (Data_N, Data_BD)

begin

case Data_N is

when "0110" => DataOut_K <= Data_BD(0);

when "0111" => DataOut_K <= Data_BD(1);

when "0101" => DataOut_K <= Data_BD(2);

when "1000" => DataOut_K <= Data_BD(3);

when "1001" => DataOut_K <= Data_BD(4);

when "1100" => DataOut_K <= Data_BD(5);

when "0011" => DataOut_K <= Data_BD(6);

when "0010" => DataOut_K <= Data_BD(7);

when others => null;

end case;

end process;

end arch_kom;

4.4.3 Отладка описания

Для проведения моделирования целесообразно воспользоваться утилитой, предоставляемой системой Active-HDL, а именно средой TestBench, которую схематично можно представить следующим образом:

Рисунок 4.11 - Система тестирования VHDL-моделей

Структура тестовой программы при этом описывается на VHDL так, как если бы она сама была цифровой системой. Верификация выполняется в соответствии с планом верификации. Он представляет собой некую таблицу, которая описывает режимы работы действия устройства. В данном проекте существует 3 режима работы: «Старт», «Стоп», «Генерация». Рассмотрим верификацию этих режимов более подробно.

Режим «Старт». Данный режим представлен в таблице 4.9, а результаты, которые были получены в процессе моделирования, представлены на рисунках 4.12 и 4.13.

Таблица 4.9 – Таблица верификации режима «Старт»

Reset |

Data |

OK |

Str |

Clk_out |

Ready |

Действие |

1 |

XXXXXXXXX |

U |

X |

U |

U |

общий сброс |

0 |

000100110 |

1 |

0-1 |

0-1 |

1 |

устройство готово к генерации импульсов |

Рисунок 4.12 – Временная диаграмма верификации режима «Общий сброс»

Рисунок 4.13 – Временная диаграмма верификации режима «Устройство готово к генерации импульсов»

Сравнивая таблицу верификации и результаты моделирования, приходим к выводу, что данный режим работает правильно. Следовательно, можно переходить к следующему режиму верификации – режим «Стоп».

Режим «Стоп». Данный режим представлен в таблице 4.10, а результаты, которые были получены в процессе моделирования, представлены на рисунках 4.14 и 4.15.

Таблица 4.10 – Таблица верификации режима «Стоп»

Data |

OK |

Clk |

Действие |

100100110 |

0 |

const |

остановка работы генератора импульсов |

000100110 |

1 |

clock |

возобновление работы генератора импульсов |

Рисунок 4.14 – Временная диаграмма верификации режима «Остановка работы генератора импульсов»

Рисунок 4.15 – Временная диаграмма верификации режима «Возобновление работы генератора импульсов»

Сравнивая таблицу верификации и результаты моделирования, приходим к выводу, что данный режим работает правильно. Следовательно, можно переходить к следующему режиму верификации – режим «Генерации».

Режим «Генерация». Данный режим представлен в таблице 4.11, а результаты, которые были получены в процессе моделирования, представлены на рисунках 4.16 и 4.17.

Таблица 4.11 – Таблица верификации режима «Генерации»

Data |

D_K |

Clk_out |

Reset |

Clk |

DataOut |

000100110 |

998 |

65,13 kHz |

0 |

65 MHz |

1110001 |

110100101 |

482 |

134,85 kHz |

0 |

65 MHz |

0110011 |

Рисунок 4.16 – Временная диаграмма верификации результата моделирования входного набора 110100101

Рисунок 4.17 – Временная диаграмма верификации результата моделирования входного набора 000100110

Сравнивая таблицу верификации и результаты моделирования, приходим к выводу, что данный режим работает правильно.

Проверив все режимы верификации данного устройства можно прийти к выводу, что данное устройство работает правильно. После этого можно приступать к следующему этапу проектирования – схемной реализации.

4.5 Схемная реализация

4.5.1 Синтез и оптимизация проекта

Синтез проводился с использованием системы синтеза Synplify 7.0 Pro фирмы Synplicity. Результатом синтеза является RTL схема вентильного уровня, схема Technology View и файл отчета. RTL - схема и отчет приведены в приложениях.

RTL – схема блока проверки на нечетность

RTL – схема блока «Шифратор»

RTL – схема устройства

4.5.2 Постсинтезное моделирование

Для проведения постсинтезного моделирования необходимо сгенерировать файл с расширением *.vhm, содержащий описания списка соединений на VHDL. (по умолчанию после выполнения синтеза генерируется файл в формате edif, однако данный формат недостаточно изучен и менее нагляден. Поэтому в Synplify предусмотрена возможность генерировать файлы со списками соединений либо в формате VHDL, либо в формате Verilog.).

Далее в Active-HDL выбирается режим поддержки множественных интерфейсов (Multiple-Unit) и соответствующая архитектура верхнего уровня. Результаты моделирования блоков проверки на нечетность и «шифратора» приведены на рис.4.18 и рис.4.19 соответственно.

Рисунок 4.18 – Временная диаграмма постсинтезного моделирования блока проверки на четность

Рисунок 4.19 – Временная диаграмма постсинтезного моделирования блока «Шифратор»

Сравнив результаты постсинтезного моделирования данных блоков, можно сказать то, что данные устройства отсинтезированы правильно.

Результаты постсинтезного моделирования всего устройства приведены ниже.

Рисунок 4.20 – Временная диаграмма постсинтезного моделирования всего устройства

Сравнив результаты постсинтезного моделирования устройства, можно сказать то, что устройство отсинтезировано правильно.

4.5.4 Реализация и программирование

Т.к. рассматриваемые блоки являются частью более сложного и большого устройства, то его реализация на ПЛИС выполняться не будет. Процедуры размещения и трассировки целесообразно выполнять для целого проекта, а не для его функциональных блоков. Таким образом, файл прошивки ПЛИС будет представлять собой битовый файл, сформированный после отладки всего устройства. Данный файл будет загружен через JTAG порт в FPGA

ПЕРЕЧЕНЬ ИСПОЛЬЗУЕМЫХ ИСТОЧНИКОВ

Перспективы развития вычислительной техники: В 11 кн.: справ. пособие / Под ред. Ю.М. Смирнова. Кн.6: специализированные ЭВМ. – М.: Высш. шк.; 1989. – 144 с.

Лямец В.И., Тевяшев А.Д. Системный анализ: Учеб. пособие. – Харьков: ХТУРЭ, 1998. – 252 с.

Лобода В.Г. и др. Проектирование встроенных устройств на микропроцессорах: Учеб. пособие. – К.: УМК ВО, 1988. – 128 с.

Методы автоматизированного проектирования специализированных микропроцессорных устройств: Учеб. пособие / В.А. Гулиус, В.Г. Лобода и др. – Харьков: ХТУРЭ, 2001. – 228 с.

Коровин Б.Г. и др. Системы программного управления промышленными установками и робототехническими комплексами: Учеб. пособие. – Л.: Энергоатомиздат, 1990. – 352 с.

Применение управляющих вычислительных машин : / А.Н. Морозевич и др. – Мн.: Выш.шк., 1988. – 238 с.

Каляев А. В. Многопроцессорные системы с программируемой архитектурой. – М.: Радио и связь, 1984. – 240 с.

Неслуховский К.С. Цифровые дифференциальные анализаторы. – М. : Машиностроение, 1968. – 260 с.

Цифровые аналоги для систем автоматического управления / Под.ред. А.А. Воронова. – М.:,Л.: АН СССР, 1960. – 196 с.

Рабинович З.Л., Раманаускас В.А. Типовые операции в вычислительных машинах. – К. : Техніка, 1980. – 264 с.

ГСТУ 3008 – 95. Документация. Отчёты в сфере науки и техники. Структура и правила оформления. Госстандарт Украины. Киев, 1995.

Балашов Е.П. и др. Микро- и мини ЭВМ: Учеб. пособие. – Л.: Энергоатомиздат, 1984. – 376 с.

Бибило П.Н. Основы языка VHDL. – М.: Солон-Р, 2000. – 200 с.

Ткаченко С. Н., Лобода В.Г., Блогадарный Н.П. Основы построения микропроцессорных систем. – МО СССР, 1987. – 240 с.

Гуртовцев А.Л., Гудыменко С.В. Программы для микропроцессоров: Справочное пособие. – Мн.: вш, 1989. – 352 с.

Майоров В.Г., Гаврилов А.И. Практический курс программирования микропроцессорных систем. – М.: Машиностроение, 1989. – 272 с.

Спец ЦВМ: Учебник для вузов/ Смолов В.Б. и др.; Под редакцией В. Б. Смолова. – М.: Высшая школа 1981. – 280 с.

IEEE VHDL STD 1076-1993 Language Reference Guide

Белоус А.И. и др. Микропроцессорный комплект БИС серии К1815 для ЦОС: справочник. – М.: Радио и связь, 1992. – 256 с.