- •1. Преобразование чисел в разных системах счисления

- •2. Выполнение арифметических операций

- •3. Логический синтез комбинационных схем

- •Литература

- •Введение

- •1. Преобразование чисел в разных системах счисления

- •1.1. Преобразование десятичных чисел в двоичную, восьмеричную и шестнадцатеричную системы счисления

- •1.2. Преобразование восьмеричных и шестнадцатеричных чисел в двоичные

- •1.3. Преобразование двоичного числа в восьмеричную и шестнадцатеричную системы счисления

- •1.4. Преобразование двоичных, восьмеричных и шестнадцатеричных чисел в десятичную систему счисления

- •1.5. Представление десятичных чисел в двоично-десятичном коде

- •2. Выполнение арифметических операций

- •2.1. Арифметические операции

- •2.2. Представление целых чисел в эвм

- •2.3. Арифметические действия над целыми числами

- •3. Логический синтез комбинационных схем

- •3.1. Базовые логические элементы

- •3.2. Составление таблицы истинности

- •3.3. Синтез одноразрядного сумматора

- •Контрольные вопросы

- •Задание на самостоятельную работу

3.2. Составление таблицы истинности

Таблица истинности логической формулы выражает соответствие между всевозможными наборами значений переменных и значениями формулы.

Для формулы, которая содержит две переменные, таких наборов значений переменных всего четыре: (0,0), (0,1), (1,0), (1,1).

Если формула содержит три переменные, то возможных наборов значений переменных восемь: (0,0,0), (0,0,1), (0,1,0), (0,1,1), (1,0,0), (1,0,1), (1,1,0), (1,1,1).

Количество наборов для формулы с четырьмя переменными равно шестнадцати и т.д.

Удобной формой записи при нахождении значений формулы является таблица, содержащая кроме значений переменных и значений формулы также и значения промежуточных формул.

1) Разберите пример

составления таблицы истинности для

формулы

![]() ,

которая содержит две переменные x

и y.

В первых двух столбцах таблицы запишем

четыре возможных пары значений этих

переменных, в последующих столбцах —

значения промежуточных формул и в

последнем столбце — значение формулы.

В результате получим таблицу:

,

которая содержит две переменные x

и y.

В первых двух столбцах таблицы запишем

четыре возможных пары значений этих

переменных, в последующих столбцах —

значения промежуточных формул и в

последнем столбце — значение формулы.

В результате получим таблицу:

Переменные |

Промежуточные логические формулы |

Формула |

|||||

|

|

|

|

|

|

|

|

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

Из таблицы видно, что при всех наборах значений переменных x и y формула принимает значение 1, т.е. является тождественно истинной.

2) Самостоятельно

составьте таблицы истинности для

формул:![]() и

и

![]() (обратите внимание, что последняя формула

содержит три логических переменных).

(обратите внимание, что последняя формула

содержит три логических переменных).

3.3. Синтез одноразрядного сумматора

Сумматор — это электронная логическая схема, выполняющая суммирование двоичных чисел. Сумматор является центральным узлом арифметико-логического устройства компьютера. Многоразрядный двоичный сумматор, предназначенный для сложения многоразрядных двоичных чисел, представляет собой комбинацию одноразрядных сумматоров.

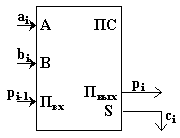

Условное обозначение одноразрядного сумматора:

При сложении чисел A и B в одном i-ом разряде приходится иметь дело с тремя цифрами:

цифра ai первого слагаемого;

цифра bi второго слагаемого;

перенос pi–1 из младшего разряда.

В результате сложения получаются две цифры:

цифра ci для суммы;

перенос pi из данного разряда в старший.

Таким образом, одноразрядный двоичный сумматор есть устройство с тремя входами и двумя выходами, работа которого может быть описана следующей таблицей истинности:

-

Входы

Выходы

Первое слагаемое ai

Второе слагаемое bi

Перенос pi–1

Сумма ci

Перенос pi

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

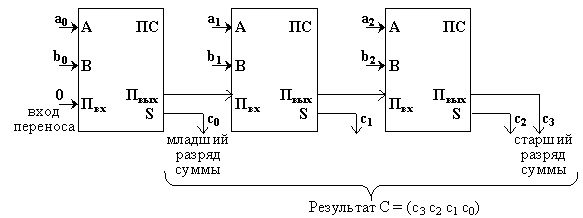

Если требуется складывать двоичные слова длиной два и более бит, то можно использовать последовательное соединение таких сумматоров, причём для двух соседних сумматоров выход переноса одного сумматора является входом для другого.

Например, схема вычисления суммы C = (с3 c2 c1 c0) двух двоичных трехразрядных чисел A = (a2 a1 a0) и B = (b2 b1 b0) может иметь вид, представленный на рис. 2.

Рис. 2.

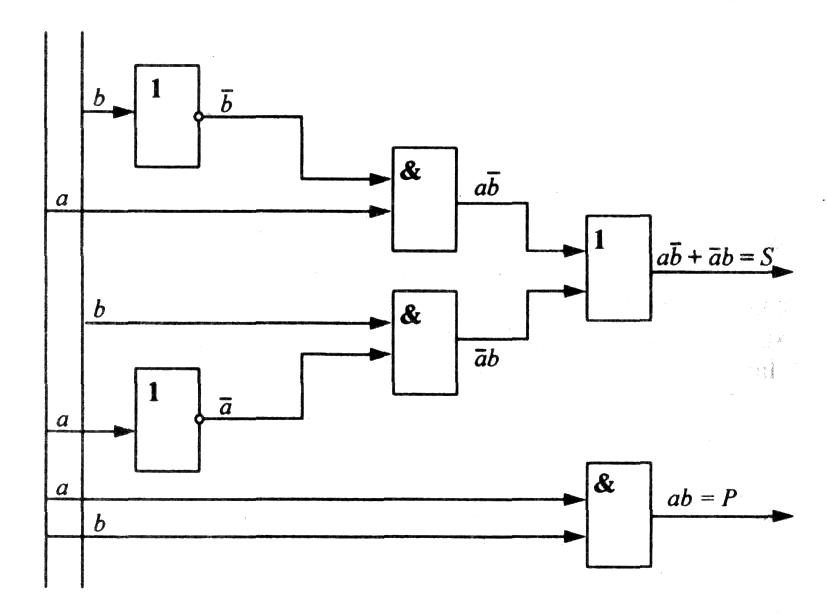

Постановка задачи: синтезировать комбинационную схему одноразрядного двоичного сумматора, имеющего два входа («а» и «b») и два выхода («S» - значение суммы и «Р» - перенос в следующий разряд.

Порядок выполнения синтеза:

Сформировать таблицу истинности.

Получить совершенные дизъюнктивные формы логических функций (СДНФ), реализуемых одноразрядным двоичным сумматором.

Используя базовый набор элементов И, ИЛИ, НЕ составить структурную схему одноразрядного двоичного сумматора комбинационного типа.

1. Одноразрядный двоичный сумматор реализует следующую таблицу сложения:

a + b |

a |

||

0 |

1 |

||

b |

0 |

0 |

1 |

1 |

1 |

10 |

|

При сложении двух единиц образуется разряд суммы S = 0 и перенос P = 1 в следующий разряд. Следовательно, одноразрядный комбинационный сумматор реализует две логических функции, таблицы истинности которых имеют вид:

а |

b |

f1(a, b) = S |

f2(a,b) = P |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

Здесь f1(a, b) = S - значение цифры суммы в данном разряде; f2(a, b) = P - цифра переноса в следующий (старший) разряд.

2. СДНФ для этих функций имеют вид:

![]()

Полученные СДНФ являются минимальными.

3. Логическая схема сумматора, реализующего полученные функции, представлена на рис. 3.

Рис. 3.

ВЫВОДЫ

Преобразование десятичных чисел в двоичную, восьмеричную и шестнадцатеричную системы счисления основано на применении правила последовательного деления к целой части числа и правила последовательного умножения к дробной части.

Преобразование восьмеричных и шестнадцатеричных чисел в двоичную систему счисления осуществляется путем замены каждой цифры эквивалентной ей двоичной триадой (тройкой цифр) или тетрадой (четверкой цифр). При этом незначащие нули слева от целой части числа, и справа от дробной части отбрасываются. Аналогично осуществляется обратное преобразование: двоичное число разбивается вправо и влево от точки, отделяющей целую часть от дробной, на триады (для восьмеричной системы счисления) или тетрады (для шестнадцатеричной системы счисления). При необходимости крайнюю левую триаду (тетраду) целой части и крайнюю правую триаду (тетраду) дробной части дополняют нулями, а затем каждую триаду (тетраду) заменяют восьмеричной (шестнадцатеричной) цифрой.

Для преобразования двоичных, восьмеричных и шестнадцатеричных чисел в десятичную систему счисления используется формула представления любого числа в виде полинома.

В двоично-десятичном коде целые числа представляются в упакованном и распакованном форматах. В упакованном формате для каждой десятичной цифры отводится по 4 двоичных разряда (полбайта), при этом знак числа кодируется в крайнем правом полубайте числа. В распакованном формате для каждой десятичной цифры отводится по целому байту, при этом старшие полубайты (зона) каждого байта (кроме самого младшего) заполняются кодом 0011, а в младших (левых) полубайтах обычным образом кодируются десятичные цифры. Старший полубайт (зона) самого младшего (правого) байта используется для кодирования знака числа.

В ЭВМ применяются три формы записи (кодирования) целых чисел со знаком: прямой код, обратный код, дополнительный код. Последние две формы позволяют упростить конструкцию арифметико-логического устройства компьютера путем замены разнообразных арифметических операций операцией сложения.

Логический элемент компьютера — это часть электронной логической схемы цифрового автомата, которая реализует элементарную логическую функцию. Логическими элементами компьютеров являются электронные схемы И (конъюнктор), ИЛИ (дизъюнктор), НЕ (инвертор), И—НЕ, ИЛИ—НЕ и другие (называемые также вентилями), а также триггер, как элемент памяти.

Сумматор — это электронная логическая схема, выполняющая суммирование двоичных чисел. Сумматор является центральным узлом арифметико-логического устройства компьютера. Многоразрядный двоичный сумматор, предназначенный для сложения многоразрядных двоичных чисел, представляет собой комбинацию одноразрядных сумматоров.