- •Структура алу.

- •2 Структура алу

- •Организация работы центрального процессора и оперативной памяти.

- •3. Устройство управления.

- •Основная память. Распределение адресного пространства ibm pc xt.

- •Распределение адресного пространства ibm pc at.

- •Страничная организация памяти. Структура страниц.

- •Виртуальная память при страничной организации.

- •8. Виртуальная память при сегментно-страничной организации.

Ответы по Архитектуре ПЭВМ

Структура алу.

Классификация АЛУ

а) По способу действия:

- Последовательные, где операнды в последовательном коде и операции производятся последовательно во времени над их отдельными разрядами.

- Параллельные, где операнды в параллельном коде, а операции идут параллельно над всеми разрядами операндов.

- Последовательно-параллельные.

б) По способу представления чисел

- Для чисел с ФЗ

- Для чисел с ПЗ

- Для десятичных чисел

в) по характеру использования элементов и узлов

- Блочные (функциональные), где все операции выполняются в отдельных блоках (высокая скорость, но очень большие затраты оборудования)

- Многофункциональные (универсальные), где все операции для всех форм представления чисел выполняются одними и теми же схемами

г) По связям с ОЗУ

-С непосредственной связью, где схема управления передачей информации соединены непосредственно с выходами соответствующих регистров АЛУ, при этом операнды, участвующие в конкретным микрооперациях считываются из одних регистров, а в других образуются результаты.

-С магистральной структурой, где схемы для преобразования информации выделены в отдельный блок, а регистры служат лишь для хранения данных. С магистралью связан лишь блок преобразования информации.

2 Структура алу

Функционально делится на 2 части:

- Устройство управления, задающее последовательность микрокоманд в соответствии с выбранной командой

- Операционное устройство (непосредственно АЛУ), в котором реализуется заданная последовательность микрокоманд

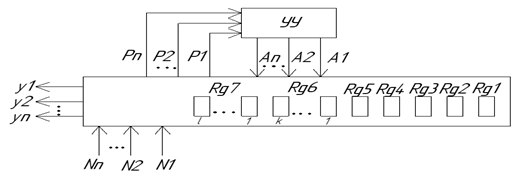

Рисунок 9 – Структурная схема АЛУ

В состав АЛУ входят регистры Rg1-Rg7, в который обрабатывается информация, поступающая по линиям N1-Nn из ОП, кэш, РОНов и так далее. Закон обработки информации задаёт некоторая микропрограмма М, которая состоит из последовательности микрокоманд А1-Аn, называемых внешними микрокомандами. P1-Pn – внутренние микрокоманды, которые генерируются в АЛУ и воздействуют на УУ, изменяя естественный порядок следования микрокоманд А1-Аn. То есть это признаки (0, отрицательного числа и так далее). Результаты вычислений передаются по линиям Y1-Yn в ОП, кэш и так далее.

Функции регистров:

Rg1 – сумматор(ы), в которых образуются результат вычислений. Rg2-Rg3 – регистры данных (операндов). Rg4-Rg5 – адресные регистры, служат для запоминания, иногда формирования адреса операндов и результата. Rg6 – это K индексных регистров, используемых для формирования адреса. Rg7 – это L вспомогательных регистров, которые используются программистом и по его желанию могут быть аккумуляторами, индексными регистрами, или использоваться для запоминания промежуточных результатов.

Часть регистров АЛУ программно доступны, то есть могут быть адресованы в команде: это сумматор, индексные регистры и некоторые вспомогательные. Разрядность регистров АЛУ равна разрядности РОНов МП.

Организация работы центрального процессора и оперативной памяти.

Организация работы ЦП и ОП

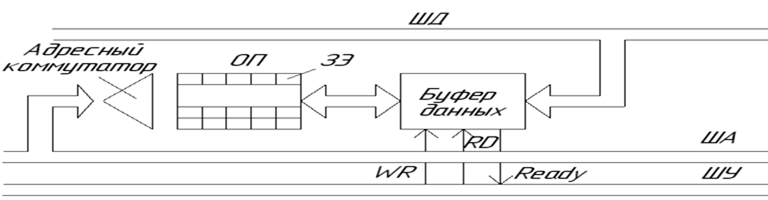

Рисунок 10 - Организация работы ЦП и ОП

Взаимодействие ЦП и ОП происходит по шинам: ША, ШД и ШУ. ОП состоит из n запоминающих ячеек, каждая из которых содержит запоминающие элементы ЗЭ, каждый ЗЭ равен одному биту информации. Разрядность ячейки ОП зависит от разрядности РОНов МП, а количество ячеек зависит от разрядности ША. Адресный коммутатор служит для выборки (селекции) ячейки ОП с заданным адресом, который формирует МП и выставляет на шину адреса. По шине управления МП высылает в ОП сигнал управления, который определяет тип доступа к ОП: чт или зп. Данные выставляются МП на шину данных. При записи при наличии сигнала Ready осуществляется запись данных в выбранную ячейку ОП. Чтение данных аналогично. Если отсутствует сигнал Ready, то МП находится в состоянии ожидания, который является частью машинного цикла.