- •Представление дробных чисел в двоичном коде с фиксированной запятой.

- •Представление чисел в двоичном коде с плавающей запятой.

- •Запись десятичных чисел.

- •Суммирование двоично-десятичных чисел.

- •Запись текстов в памяти процессора.

- •Арифметико-логические устройства

- •Команды микропроцессора

- •Принципы работы микропроцессора.

- •Блок обработки сигналов микропроцессора.

- •Блок микропрограммного управления

- •Микропрограммирование

- •Системная шина процессора.

- •Адресное пространство микропроцессорного устройства.

- •Способы расширения адресного пространства микропроцессора.

- •Причины широкого распространения микропроцессоров.

- •Выводы:

- •Классификация микропроцессоров.

- •Причины широкого распространения микропроцессоров.

- •Выводы:

- •Классификация микропроцессоров.

- •Универсальные микропроцессы.

- •Микроконтроллеры. Область применения

Системная шина процессора.

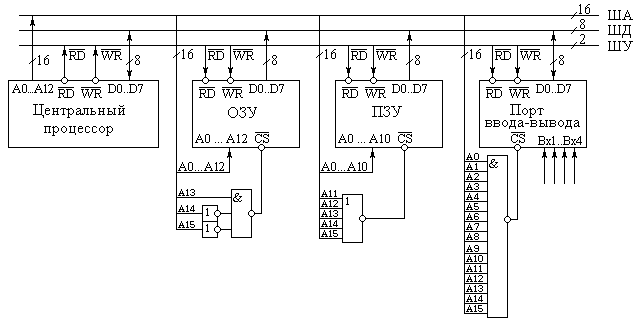

Системная шина процессора предназначена для обмена информацией микропроцессора с любыми внутренними устройствами микропроцессорной системы (контроллера или компьютера). В качестве обязательных устройств, которые входят в состав любой микропроцессорной системы, можно назвать ОЗУ, ПЗУ, таймер и порты ввода-вывода. Структурная схема простейшего микропроцессорного устройства приведена на рисунке 1.

В состав системной шины в зависимости от типа процессора входит одна или несколько шин адреса, одна или несколько шин данных и шина управления. Несколько шин данных и адреса применяется для увеличения производительности процессора и используется только в сигнальных процессорах. В универсальных процессорах и контроллерах обычно применяется одна шина адреса и одна шина данных.

В понятие шины вкладывают разное значение при рассмотрении различных вопросов. В простейшем случае под понятием шина подразумевают параллельно проложенные провода, по которым передаётся двоичная информация. При этом по каждому проводу передаётся отдельный двоичный разряд. Информация может передаваться в одном направлении, как, например, для шины адреса или шины управления, или в различных направлениях (для шины данных). По шине данных информация передаётся либо к процессору, либо от процессора в зависимости от операции записи или чтения, которую в данный момент осуществляет процессор.

В любом случае все сигналы, необходимые для работы системной шины формируются микросхемой процессора как это рассматривалось при изучении блока обработки данных. Иногда для увеличения скорости обработки информации функции управления системной шины берёт на себя отдельная микросхема (например контроллер прямого доступа к памяти или сопроцессор). Арбитраж доступа к системной шине при этом осуществляет контроллер системной шины (в простейшем случае достаточно сигнала занятости шины).

В некоторых случаях в понятие шина дополнительно включают требования по уровням напряжения, которыми представляются нули и единицы, передаваемые по её проводам. В состав требований могут быть включены длительности фронтов передаваемых сигналов, типы используемых разъёмов и их распайка, последовательность передаваемых сигналов и скорость их передачи.

Рисунок 1. Структурная схема подключения микропроцессорных устройств к системной шине.

При подключении различных устройств к системной шине возникает вопрос - как различать эти устройства между собой? Единственный способ сделать это использовать индивидуальный адрес для каждого устройства, подключенного к системной шине микропроцессора. Так как адресация производится к каждой ячейке устройства индивидуально, то возникает понятие адресного пространства, занимаемого каждым устройством и адресного пространства микропроцессорного устройства в целом.

Адресное пространство микропроцессорного устройства.

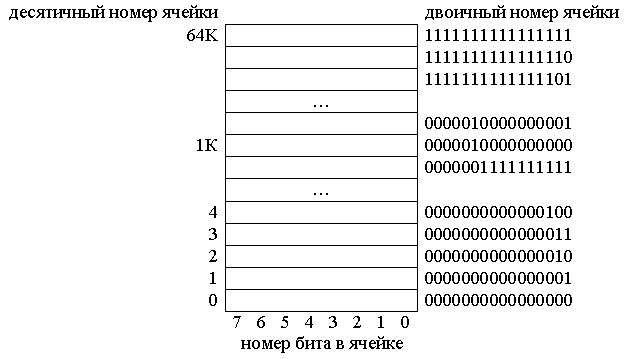

Адресное пространство микропроцессорного устройства изображается графически прямоугольником, одна из сторон которого представляет разрядность адресуемой ячейки этого микропроцессора, а другая сторона - весь диапазон доступных адресов для этого же микропроцессора. Обычно в качестве минимально адресуемой ячейки памяти выбирается восьмиразрядная ячейка памяти (байт). Диапазон доступных адресов микропроцессора определяется разрядностью шины адреса системной шины. При этом минимальный номер ячейки памяти (адрес) будет равен 0, а максимальный определяется из формулы:

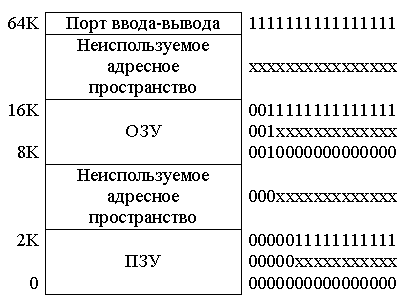

Для шестнадцатиразрядной шины это будет число 65535 (64K). Адресное пространство этой шины и распределение памяти микропроцессорной системы, изображённой на рисунке 1, приведено на рисунке 2, а распределение памяти микропроцессорной системы, изображённой на рисунке 1, приведено на рисунке 3.

Рисунок 2. Адресное пространство шестнадцатиразрядной шины адреса.

Рисунок 3. Распределение памяти микропроцессора с шестнадцатиразрядной шиной адреса.

Микропроцессоры после включения питания и выполнения процедуры сброса всегда начинают выполнение программы с определённого адреса, чаще всего нулевого. Однако есть и исключения. Например процессоры, на основе которых строятся универсальные компьютеры IBM PC или Macintosh стартуют не с нулевого адреса. Программа должна храниться в памяти, которая не стирается при выключении питания, то есть в ПЗУ.

Выберем для построения микропроцессорной системы микросхему ПЗУ объёмом 2 килобайта, как это показано на рисунке 1. При рассмотрении построения блока обработки сигналов мы договорились, что процессор после сброса начинает работу с нулевого адреса, поэтому разместим ПЗУ в адресном пространстве начиная с нулевого адреса. Для того, чтобы нулевая ячейка ПЗУ оказались расположенной по нулевому адресу адресного пространства микропроцессора, старшие разряды шины адреса должны быть равны 0.

При построении схемы необходимо декодировать старшие пять разрядов адреса (определить, чтобы они были равны 0). Это выполняется при помощи дешифратора адреса, который в данном случае вырождается в пятивходовую схему "ИЛИ-НЕ" Это связано с тем, что внутри ПЗУ уже есть одиннадцативходовый дешифратор адреса. При использовании дешифратора адреса, обращение к ячейкам памяти выше двух килобайт не приведёт к чтению ячеек ПЗУ, так как на входе выбора кристалла CS уровень напряжения останется высоким.

Теперь подключим микросхему ОЗУ. Для примера выберем микросхему объёмом 8 Кбайт. Для выбора любой из ячеек этой микросхемы достаточно тринадцатибитового адреса, поэтому необходимо дополнительно декодировать три оставшихся разряда адреса. Так как начальные ячейки памяти адресного пространства уже заняты ПЗУ, то использовать нельзя. Выберем следующую комбинацию цифр 001 и используем известные нам принципы построения схемы по произвольной таблице истинности. Дешифратор адреса выродится в данном случае в трёхвходовую схему "И-НЕ" с двумя инверторами на входе. Схема этого дешифратора приведена на рисунке 1. Приведённый дешифратор адреса обеспечивает нулевой уровень сигнала на входе CS только при комбинации старших бит 000. Обратите внимание, что так как объём ПЗУ меньше объёма ОЗУ, то между областью адресов ПЗУ и областью адресов ОЗУ образовалось пустое пространство неиспользуемых адресов памяти.

И, наконец, так как все микропроцессоры предназначены для обработки данных, поступающих извне, то в любой микропроцессорной системе должны присутствовать порты ввода-вывода. Порт ввода-вывода отображается в адресное пространство микропроцессорного устройства как одиночная ячейка памяти, поэтому порт ввода вывода можно разместить по любому свободному адресу. Проще всего построить дешифратор числа FFFFh. В этом случае дешифратор превращается в обычную 16-ти входовую схему "И-НЕ", поэтому и выберем эту ячейку памяти в адресном пространстве микропроцессора для размещения порта ввода-вывода.