- •Абсолютные способы формирования исполнительного адреса операндов

- •Встраиваемые и промышленные компьютеры

- •В чем суть mmx-технологии и потоковых simd-расширений?

- •В чем суть матричного и векторно-конвейерного способов организации simd-архитектуры

- •Иерархическая структура памяти компьютера

- •Как определяется энергоэффективность процессора?

- •Как осуществляется декодирование команд x86 в процессоре Intel Nehalem?

- •Как осуществляется декодирование команд x86 в ядре amd k10?

- •Какие новые возможности появились у процессора с введением расширения команд sse-2, sse-3?

- •Какими преимуществами обладают блейд-серверы?

- •Какими характеристиками должен обладать пк?

- •Классификация mimd-систем по способу взаимодействия процессоров

- •Классификация архитектуры sisd с краткой характеристикой классов

- •Классификация интерфейсов

- •Классификация ноутбуков

- •Классификация методов построения центрального устройства управления процессора

- •Классификация микро-эвм с краткой характеристикой классов

- •Классификация пк по способу использования

- •Классификация серверов с пояснениями

- •Классификация, состав, платформы, производители карманных пк

- •Классификация способов организации simd-архитектуры с пояснениями

- •Конвейерная технология выполнения команд

- •Концепция виртуальной памяти

- •Косвенная адресация операндов

- •Логическая организация центрального процессора эвм

- •Методы обновления строк в основной и кэш-памяти

- •Методы повышения пропускной способности оперативной памяти (организация памяти на ddr sdram)

- •Методы повышения пропускной способности оперативной памяти (расслоение обращений)

- •Методы преобразования виртуального адреса в физический при странично-сегментном распределении памяти с использованием tlb

- •Методы замещения строк в кэш-памяти

- •Методы ускорения процессов обмена информацией между оп и внешними запоминающими устройствами

- •Механизм преобразования виртуального адреса в физический при страничной организации памяти

- •Механизм стековой адресации по способу lifo

- •Модульная структура процессора Intel Nehalem

- •Обобщенная структура эвм и основные направления её развития

- •Обобщенный формат команд x86

- •Общие принципы организации оперативной памяти компьютера

- •Объяснить суть процедуры переименования регистров в современных процессорах

- •Определить назначение, количество, принцип действия исполнительных устройств процессора Intel Nehalem

- •Определить назначение, количество, принцип действия исполнительных устройств ядра amd k10

- •Определить назначение, структуру, количество регистров mmx-технологии и расширений sse, sse2

- •Определить назначение, структуру, количество основных функциональных регистров ia-32

- •Определить назначение, структуру, количество регистров процессора обработки чисел с плавающей точкой ia-32 (x87)

- •Регистры ммх-технологии

- •Организация многоуровневой кэш-памяти

- •Основные отличительные черты epic-концепции

- •Основные характерные черты cisc-архитектуры

- •Основные характерные черты risc-архитектуры

- •Основные характерные черты vliw-архитектуры

- •Основные характерные черты суперскалярной обработки

- •Особенности микроархитектуры Intel Core

- •Особенности микроархитектуры Intel Sandy Bridge

- •Особенности микроархитектуры процессоров Intel Nehalem

- •Особенности архитектуры процессоров x86-64 (amd64, Intel64)

- •Особенности процессоров семейства Intel Westmere

- •Особенности процессорного ядра amd k10

- •Особенности системы команд в ia-64

- •Охарактеризуйте все виды производительности компьютера

- •Перечислить основные требования, которые учитываются при проектировании серверов

- •Принцип работы кэш-памяти с полностью ассоциативным распределением

- •Принцип работы кэш-памяти с частично ассоциативным распределением

- •Программно-управляемая передача данных в компьютере

- •Программно-управляемый приоритет прерывающих программ

- •Прямой доступ к памяти в компьютере

- •Показать развитие и классификацию однопроцессорных архитектур

- •Почему появились многоядерные структуры процессоров и технологии многопоточности?

- •Развитие cisc-системы команд x86 (по годам)

- •Распределение оперативной памяти динамическими разделами

- •Распределение оперативной памяти перемещаемыми разделами

- •Распределение оперативной памяти фиксированными разделами

- •Расширение системы команд aes-ni, avx

- •Реализация адресации «Базирование с индексированием»

- •Реализация адресации операндов «Базирование способом совмещения составляющих исполнительного адреса Аи»

- •Реализация адресации операндов «Базирование способом суммирования»

- •Реализация индексной адресации операндов

- •Регистровые структуры процессоров ia-64

- •Регистровые структуры процессоров x86-64 архитектуры (amd64, Intel64)

- •Сегментное распределение виртуальной памяти

- •Сильносвязанные и слабосвязанные многопроцессорные системы

- •Системная организация эвм на базе чипсетов Intel

- •Страничное распределение виртуальной памяти

- •Стратегия развития процессоров Intel

- •Странично-сегментное распределение памяти

- •Структура кэш-памяти с прямым распределением данных

- •Теги и дескрипторы

- •Типовая структура кэш-памяти

- •Типы данных ia-32 (без mmx и sse)

- •Типы данных ia-64

- •Типы данных mmx-технологии

- •Типы данных sse, sse-2 расширений

- •Форматы команд risc-процессора

- •Формат команд в ia-64, структура пакета инструкций

- •Функции центрального устройства управления процессором

- •Функциональные возможности, назначение, платформы рабочих станций

- •Функциональные возможности, назначение, современные разработки ультра-мобильных и планшетных пк

- •Функциональные возможности, области применения, основные производители мэйнфреймов

- •Функциональные возможности, пути развития, современные разработки супер-эвм

- •Характеристики интерфейсов

- •Характеристики системы прерывания

- •Характерные черты современных универсальных микропроцессоров

- •Центральное устройство управления микропрограммного типа

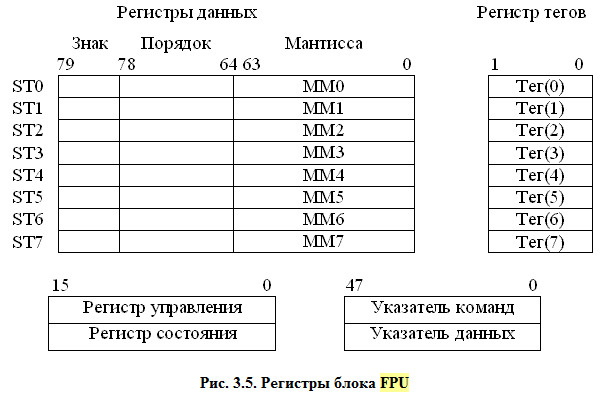

Определить назначение, структуру, количество регистров процессора обработки чисел с плавающей точкой ia-32 (x87)

Набор регистров, входящих в блок FPU, изображен на схеме ниже. При работе FPU 80-разрядные регистры ST0-ST7 образуют кольцевой стек, в котором хранятся числа с плавающей точкой, представленные в формате с расширенной точностью.

Регистр тегов FPU содержит 16-разрядное слово, включающее восемь двухбитовых тегов. Каждый тег (признак) характеризует содержимое одного из регистров данных. Тег определяет, является ли регистр пустым (незаполненным) – код 11 или в него введено конечное число – 00 (достоверное значение), или нуль – 01, неопределенное значение (бесконечность) – 10 (нет числа и неподдерживаемый формат). Слово тегов позволяет оптимизировать функционирование FPU посредством идентификации пустых и непустых регистров данных, проверить содержимое регистра без сложного декодирования хранящихся в нем данных.

Регистры ммх-технологии

При реализации ММХ-команд регистры данных FPU используются как 64-разрядные регистры ММ0 – ММ7 (схема выше), где могут храниться несколько целочисленных операндов (восемь 8-разрядных, четыре 16-разрядных, два 32-разрядных или один 64-разрядный), над которыми одновременно выполняется поступившая в процессор команда.

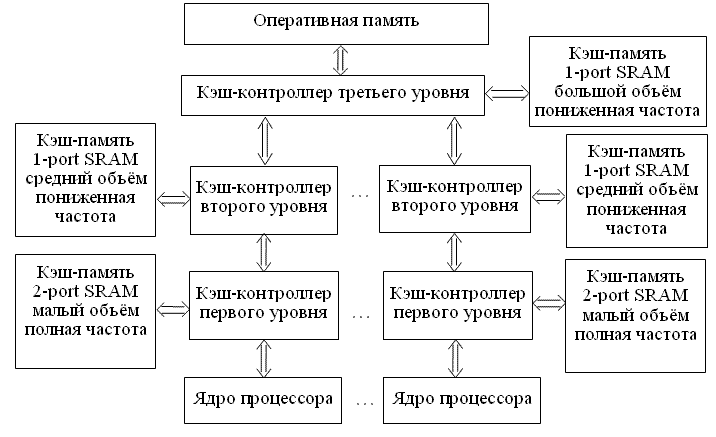

Организация многоуровневой кэш-памяти

Большинство современных компьютеров имеют два или три уровня кэш-памяти. Первый, наиболее «близкий» к ядру процессора (L1), обычно реализуется на быстрой двухпортовой синхронной статической памяти, работающей на полной частоте ядра. Объём L1-кэша весьма невелик, составляет 64 КВ или 128 КВ и разделяется пополам на два кэша данных и команд для каждого ядра процессора. Латентность кэша L1 измеряется 3-мя, 4-мя тактами. На втором уровне расположен кэш L2. Он реализуется на однопортовой конвейерной статической памяти и зачастую работает на пониженной тактовой частоте. Поскольку однопортовая память значительно дешевле, объём L2-кэша достигает нескольких мегабайт в двухъядерных структурах процессоров, когда он является общим для двух ядер (Intel Core 2 Duo), или несколько сотен килобайт (256 КВ или 512 КВ), когда в многоядерном процессоре каждое ядро имеет свой L2-кэш. Этот кэш хранит как команды, так и данные. Латентность L2 для процессоров Intel Nehalem 3,2 ГГц составляет 11 тактов, для Penryn 3,2 ГГц – 18 тактов.

На третьем уровне находится L3-кэш, который объединяет ядра между собой и является разделяемым. В результате, L2-кэш выступает в качестве буфера при обращениях процессорных ядер в разделяемую кэш-память, имеющую достаточно солидный объём (2 МВ – AMD K10, 8 МВ – Intel Nehalem). Латентность L3-кэша исчисляется 52-мя, 54-мя тактами.

При построении многоуровневой кэш-памяти используют включающую (inclusive) или исключающую (exclusive) технологии. Кэш верхнего уровня, построенный по inclusive-технологии, всегда дублирует содержимое кэша нижнего уровня. Если построить инклюзивный L3-кэш, то он будет дублировать данные, хранящиеся в кэшах первого и второго уровней, что снижает эффективную ёмкость всей кэш-подсистемы. С другой стороны, инклюзивный разделяемый L3-кэш способен обеспечить в многоядерных процессорах более высокую скорость работы подсистемы памяти. Это связано с тем, что, если ядро попытается получить доступ к данным, и они отсутствуют в кэше L3, то нет необходимости искать эти данные в собственных кэшах других ядер – там их нет. А благодаря тому, что каждая строка L3-кэша снабжена дополнительными флагами, указывающими владельцев (ядра) этих данных, не вызывает затруднений и процедура обратного изменения содержимого строки кэша. Так, если какое-то ядро модифицирует данные в L3-кэше, изначально принадлежащие другому (или другим) ядрам, то в этом случае обновляется содержимое L1 и L2-кэшей и этих ядер. Эта технология весьма эффективна для обеспечения когерентности персональных кэшей каждого ядра, поскольку она уменьшает потребность в обмене информацией между ядрами. По такой технологии организована кэш-память процессоров Intel Nehalem.

Кэш – подсистема, построенная по exclusive-технологии, никогда не хранит избыточных копий данных и потому эффективная ёмкость подсистемы определяется суммой ёмкостей кэш-памятей всех уровней. Кэш первого уровня никогда не уничтожает строки при нехватке места. Даже если они не были модифицированы, данные в обязательном по-рядке вытесняются в кэш второго уровня, помещаясь на то место, где находилась только что переданная кэшу L1 строка. Т. е. кэши L1 и L2 как бы обмениваются друг с другом своими строками, а потому кэш-память используется весьма эффективно.