- •Архітектура систем з базами даних

- •Інформаційне моделювання предметних середовищ

- •Ієрархічна, мережна та реляційна моделі даних

- •Операції реляційної алгебри та їх реалізація на мові sql.

- •Операции над множествами.

- •Специальные реляционные операции.

- •Мова запитів sql. Операція вибірки select.

- •Вкладені та корельовані підзапити в мові sql, агрегатні функції та квантори.

- •Операції модифікації даних у мові sql: update, insert, delete.

- •Теорія нормалізації. Функціональна залежність між атрибутами. Аномалії модифікації у ненормалізованій бд. Переваги нормальних форм. Способи одержання нормальних форм.

- •Моделі взаємодії в архітектурі “клієнт-сервер” та субд, що їх підтримують.

- •Проблеми одночасного доступу користувачів до бд та використання транзакцій.

- •Інтерфейси доступу до бд з різних програмних середовищ.

- •Характеристика сучасних реляційних субд.

- •Еталонна модель взаємодії відкритих систем.

- •Організація доступу до спільного середовища передачі даних csma/cd

- •Стандарти мережі Ethernet на мідному кабелі.

- •Стандарти мережі Ethernet на оптоволоконному кабелі.

- •Організація бездротових комп'ютерних мереж та їх стандарти.

- •Об’єднання сегментів у мережі Ethernet за допомогою концентраторів, комутаторів та маршрутизаторів.

- •Структура та робота комутатора в мережах Ethernet.

- •Інтелектуальні комутатори та віртуальні лом на їх основі.

- •Класифікація лом у відповідності з ieee 802.

- •Аналіз функціонування обчислювальних мереж. Можливості мережних аналізаторів.

- •Призначення та можливості протоколів сімейства tcp/ip.

- •Мережні транспортні протоколи: ipx/spx, NetBios. Особливості та застосування.

- •Кадр инициализации сессии. Кадр подтверждения сессии. Кадр опознания имени.

- •Протокол udp. Структура дейтаграм, застосування.

- •Протокол тср. Структура сегментів, застосування. Встановлення та завершення з'єднання.

- •Адресація у мережних транспортних протоколах.

- •Поняття маршрутизації. Приклад статичної маршрутизації в невеликій мережі.

- •Класифікація протоколів динамічної маршрутизації.

- •Протокол icmp. Призначення, основні типи повідомлень.

- •Система доменних імен dns. Правила делегування зон в Інтернеті.

- •Налагодження системи імен dns для корпоративної мережі. Структура прямої та зворотньої зони dns.

- •Інтерфейс сокетів та його застосування при програмуванні мережних задач. Типи сокетів та сімейства адрес.

- •Передача даних через сокети у режимі дейтаграм.

- •Передача даних через сокети у режимі та сесій.

- •Моделі програмування серверних потокових сокетів.

- •Програмування комунікаційних протоколів прикладного рівня.

- •Архітектура систем з базами даних

Структура та робота комутатора в мережах Ethernet.

Коммутатор делит общую среду передачи данных на логические сегменты. Как и многопортовые мосты коммутаторы передают пакеты между портами на основе адреса получателя, включенного в каждый пакет. реализация коммутаторов обычно отличается от мостов в части возможности организации одновременных соединений между любыми парами портов устройства - это значительно расширяет суммарную пропускную способность сети.

В настоящее время коммутаторы используют в качестве базовой одну из трех схем, на которой строится такой узел обмена: коммутационная матрица; разделяемая многовходовая память; общая шина.Часто эти три способа взаимодействия комбинируются в одном коммутаторе.

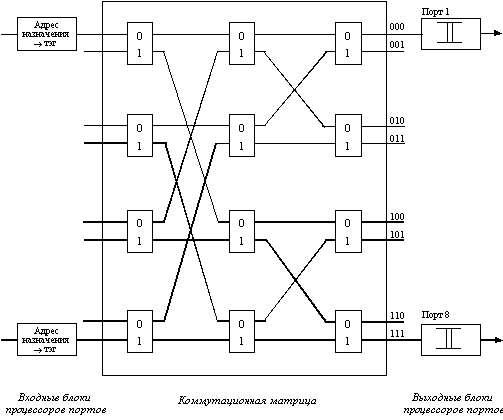

Коммутаторы на основе коммутационной матрицы Коммутационная матриц обеспечивает основной и самый быстрый способ взаимодействия процессоров портов. Однако реализ матрицы возможна только для определенного числа портов.

Матрица состоит из трех уровней двоичных переключателей, которые соединяют свой вход с одним из двух выходов в зависимости от значения бита тэга. Переключатели первого уровня управляются первым битом тэга, второго - вторым, а третьего - третьим. Процесор ЕРР буферизирует несколько первых байт кадра чтобы установить адрес получателя, затем процессор направляет пакет на указанный порте дожидаясь приема остальных байт пакета. После этого процессор обращается к коммутационной матрице для передачи пакета на требуемый порт. Передача возможна если порт свободен, если занят, то пакет полностью буферизируется процессором EPP выходного порта и процессор будет вновь пытатся получить доступ к порту, используя метод соперничества.

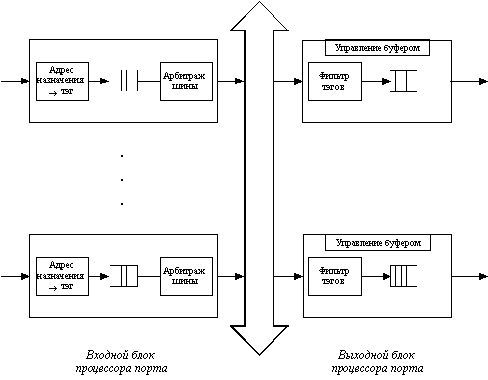

Коммутаторы с общей шиной В коммутаторах с общей шиной процессоры портов связывают высокоскоростной шиной, используемой в режиме разделения времени. Чтобы шина не блокировала работу коммутатора, ее производительность должна равняться по крайней мере сумме производительности всех портов коммутатора. Для модульных коммутаторов некоторые сочетания модулей с низкоскоростными портами могут приводить к неблокирующей работе, а установка модулей с высокоскоростными портами может приводить к тому, что блокирующим элементом станет, например, общая шина

Кадр должен передаваться по шине небольшими частями, по нескольку байт, чтобы передача кадров между несколькими портами происходила в псевдопараллельном режиме, не внося задержек в передачу кадра в целом. Размер такой ячейки данных определяется производителем коммутатора. Входной блок процессора помещает в ячейку, переносимую по шине, тэг, в котором указывает номер порта назначения. Каждый выходной блок процессора порта содержит фильтр тэгов, который выбирает тэги, предназначенные данному порту.

Шина, так же как и коммутационная матрица, не может осуществлять промежуточную буферизацию, но так как данные кадра разбиваются на небольшие ячейки, то задержек с начальным ожиданием доступности вых порта в такой схеме нет - здесь работает принцип коммутации пакетов, а не каналов.

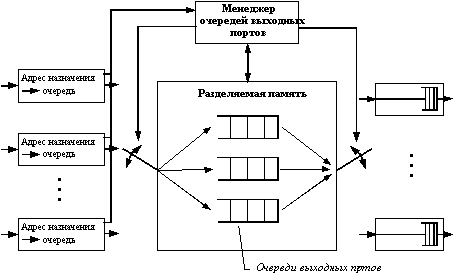

Коммутаторы с разделяемой памятью Входные блоки процессоров портов соединяются с переключаемым входом разделяемой памяти, а выходные блоки этих же процессоров соединяются с переключаемым выходом этой памяти. Переключением входа и выхода разделяемой памяти управляет менеджер очередей выходных портов. В разделяемой памяти менеджер организует несколько очередей данных, по одной для каждого выходного порта. Входные блоки процессоров передают менеджеру портов запросы на запись данных в очередь того порта, который соответствует адресу назначения пакета. Менеджер по очереди подключает вход памяти к одному из входных блоков процессоров и тот переписывает часть данных кадра в очередь определенного выходного порта.

По мере заполнения очередей менеджер производит также поочередное подключение выхода разделяемой памяти к выходным блокам процессоров портов, и данные из очереди переписываются в выходной буфер процессора.

Память должна быть достаточно быстродействующей для поддержания скорости переписи данных между N портами коммутатора. Применение общей буферной памяти, гибко распределяемой менеджером между отдельными портами, сниж требов к размеру буферной памяти процессора порта.