1.4

Структурная схема и основное назначение

блоков декодера. Основные этапы обработки

звука

1.4

Структурная схема и основное назначение

блоков декодера. Основные этапы обработки

звука

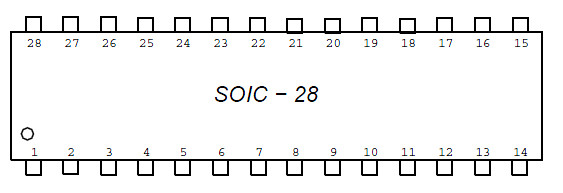

VS1011е — аудио-декодер на основе обновленного DSP ядра (VS DSP4). Внешний вид и корпус микросхемы представлены на рисунке 1.8. По сравнению с предшественниками в микросхеме присутствуют такие новые функции, как потоковое воспроизведение, поддержка режимов CBR и ABR, воспроизведение WAV, 320 кбит/с МРЗ (внешним кварцевым резонатором 12 МГц), контроль низких и высоких частот, возможность загрузки с Flash-памяти по SPI-интерфейсу для специальных применений. По сравнению с VS1001k увеличена внутренняя RAM-память до 5,5 Кб.

Рисунок 1.8 – Внешний вид и корпус VS1011e

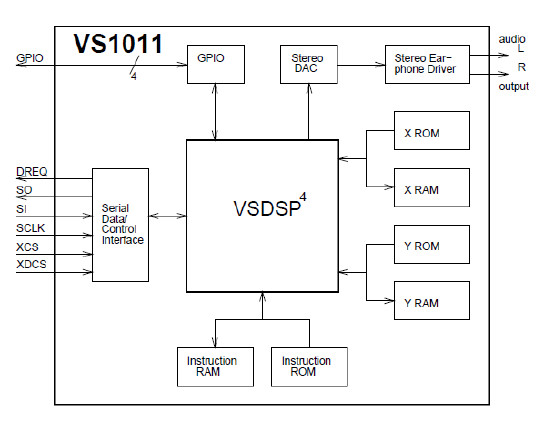

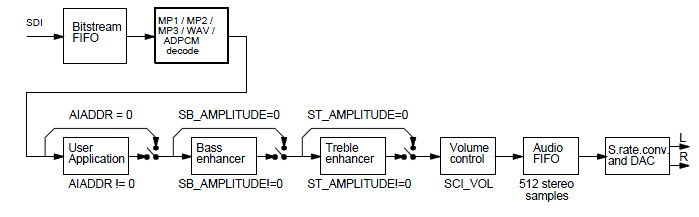

На рисунке 1.9 показана структурная схема VS1011e.

Микросхема содержит высокопроизводительный цифровой сигнальный процессор, с низким потреблением энергии, на основе ядра VS DSP4, с рабочей памятью (5 Кб памяти для инструкций и 0,5 Кб оперативной памяти для пользовательских приложений), последовательным контролем (SCI) и входными интерфейсами ввода данных (SDI и SPI), четырьмя пинами ввода/вывода общего назначения (GPIO), высококачественным цифро – аналоговым преобразователем (ЦАП), который способен обработать поток с переменным битрейтом, а также усилителем выходного сигнала и общим буфером.

Блок Serial Data Control Interface включает в себя два интерфейса типа SPI (синхронный последовательный порт): SCI и SDI.

SCI (последовательный командный интерфейс) используется для управления схемой декодирования. Обмен информации в нем осуществляется 16-разрядными словами. Прием цифровых данных осуществляется с помощью SDI (последовательный интерфейс данных).

Рисунок 1.9 – Структурная схема микросхемы VS1011e

Процессор VS DSP4 производит декодирование, изменение уровня низких частот, громкости, а также передачу информации на ЦАП с необходимой частотой.

Stereo DAC (ЦАП) преобразовывает данные в аналоговый сигнал, который затем усиливается в Stereo Earphone Driver и поступает на выход VS1011e.

В Instruction ROM содержатся программные инструкции, а Instruction RAM отдана под пользовательские приложения.

В X

и Y

памяти содержатся регистры микросхемы

(например, регистры, используемые для настройки

VS1011e,

располагаются в X-памяти).

регистры, используемые для настройки

VS1011e,

располагаются в X-памяти).

VS1011e получает входной поток через последовательную входную шину, которую он прослушивает как вторичное системное устройство. Входной поток декодируется и проходит через устройство контроля цифрового уровня на 18-битный ЦАП.

Декодирование контролируется последовательной шиной контроля. Вместе с простым декодированием возможно добавление в область памяти

для

пользовательских приложений специфических

программных установок, таких как цифровая

обработка сигналов. VS1011e может загружаться

напрямую через последовательный

периферийный интерфейс электронно-стираемого

программируемого постоянного запоминающего

устройства (ЭСППЗУ, EEPROM) для запуска

автономных приложений без отдельного микроконтроллера.

микроконтроллера.

Основные этапы обработки звука

Данные поступают в микросхему через шину данных SDI (или SCI , но тогда исключается прохождение потока данных через блок - декодер и поток данных представляет собой 16-разрядный линейный код). Поток данных проходит через декодер МР1/2/3/WAV/ADPCM (рисунок 1.10). При A1ADDR, отличным от нуля, данные попадают в блок User Application. Специалистами VLSI была предусмотрена возможность вносить изменения в звуковой поток при помощи пользовательской программы, для которой выделено 0,5 Кб в памяти микросхемы. Такое дополнение к функциональности позволяет реализовывать собственные фильтры, накладывать различные эффекты (например, эхо или реверберацию). Если регистр A1ADDR равен

Рисунок 1.10– Основные этапы обработки звука

нулю, то данные попадают сразу на эквалайзер. В том случае,

когда разработчик использует собственную программу, этот регистр должен быть равен адресу начала программы. На этом этапе можно либо увеличить уровень низких частот, либо уменьшить его. После этого сигнал поступает на

блок регулировки громкости, который также передает данные к Аудио FIFO. Буфер FIFO предназначен для того, чтобы своевременно выдавать данные на ЦАП с частотой, равной частоте дискретизации. После этого данные через ЦАП и усилитель передаются на наушники.

Установка частоты дискретизации

Частота дискретизации

— частота взятия отсчетов при

преобразовании аналогового звукового

сигнала в цифровой, или наоборот.

Выражается числом отсчетов в секунду

или в герцах.

VS1011e

позволяет проигрывать звуковые файлы

с максимальной возможной частотой

дискретизации 48000 Гц. При этом задающий

генератор (речь идет о кварцевом или

диэлектрическом резонаторе) должен

работать на частоте не менее 24,576 МГц,

именно эта частота рекомендована для

микросхемы. Если частота генератора

меньше, уменьшается и частота дискретизации.

Для ее расчета можно воспользоваться

формулой:

формулой:

Частота дискретизации = 48000 × частота генератора/24,576

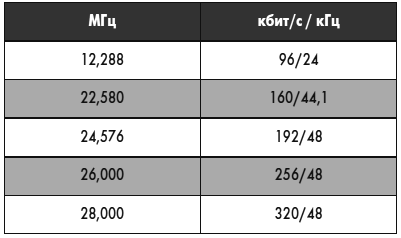

От частоты генератора напрямую зависит производительность DSP-процессора. На рисунке 1.11 представлена зависимость качества звука (скорость звукового потока и частоты дискретизации) и задающей частоты.

Рисунок 1.11 - Зависимость качества звука от задающей частоты

Таблица 1.2 – Регистры управления микросхемой

Название |

Чт/Зп |

Адрес |

Назначение |

MODE |

RW |

0 |

Управление VS1011e |

Продолжение таблицы 1.2

STATUS |

RW |

1 |

Состояние VS1011e |

BASS |

RW |

2 |

Встроенный эквалайзер |

CLOCKF |

RW |

3 |

Корректировка частоты |

DECODE_TIME |

RW |

4 |

Время декодирования в секундах |

AUDATA |

RW |

5 |

Дополнительная информация звукового потока |

WRAM |

RW |

6 |

Начальный адрес для записи приложений в RAM |

WRAMADDR |

RW |

7 |

Адрес для запуска приложений |

HDAT0 |

R |

8 |

Данные заголовка mp-3 файла |

HDAT1 |

R |

9 |

Данные заголовка mp-3 файла |

AIADDR |

RW |

10 |

Начальный адрес программы |

VOL |

RW |

11 |

Задает аппаратное ослабление сигнала |

AICTRL[X] |

RW |

12+X (X=0…3) |

Прикладной контроль регистра X |

В таблице 1.2 приведены регистры, которые применяются для настройки микросхемы с помощью интерфейса SCI.

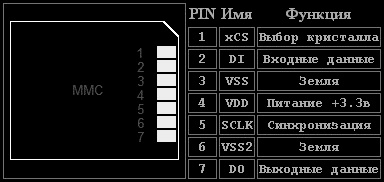

1.5 Архитектура памяти

Карты типа MultiMedia Card (MMC) были разработаны в 1997 г. компаниями SanDisk и Siemens на базе NAND-памяти Toshiba, имеют семиконтактный разъем (сконструированный так, чтобы минимизировать риск повреждения контактов), карточка состоит из пластиковой оболочки и печатной платы, на которой расположена микросхема памяти, микроконтроллер и контакты. Несмотря на последовательную природу

MMC,

данные и команды могут передаваться

одновременно.

MMC,

данные и команды могут передаваться

одновременно.

MMC совместима с разработанной чуть позднее SD - картой и может использоваться вместо SD. В обратном направлении замена чаще всего невозможна, так как SD-карты толще MMC и просто механически могут не войти в слот для MMC-картыMMC карты имеют достаточно простое управление. Память разбита на сектора по 512 байт. Карты форматируются так же, как обычные винчестеры под DOS: с 1 разделом, файловая система - FAT16. Чтение возможно как отдельными байтами, так и блоками. Напряжение питания карты должно быть в пределах +2.7...+3.6 Вольт, скорость обмена до 20 Мбит/с. При простое более 5мс карточка переводится в sleep - режим с малым энергопотреблением, и выходит из него автоматически при возобновлении обмена.

Интерфейс карты

MMC карты могут работать в двух режимах обмена – MultiMedia Card protocol и SPI protocol. Первый более скоростной, а второй удобен тем, что много контроллеров имеют встроенный SPI интерфейс. На рисунке 1.13 представлена разводка MMC именно для работы в режиме SPI.

Рисунок 1.12 - Разводка MMC для работы в режиме SPI

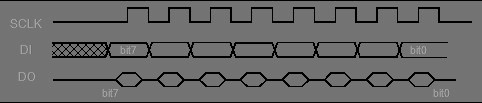

Принцип обмена данными в SPI режиме.

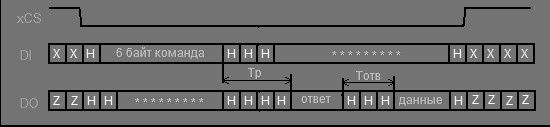

Сигнал выборки имеет активный уровень "0". SPI порт в управляющем контроллере должен быть настроен так, чтобы активным был передний фронт SCLK, это представлено на рисунке 1.14

Фактически передача байта из контроллера (DO) осуществляется параллельно с приёмом по другой линии (DI).

Рисунок 1.13

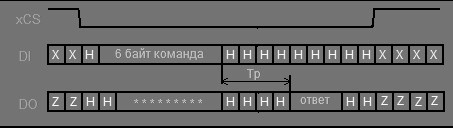

Чтобы начать приём/передачу через SPI в PIC контроллере,в буфер приёмопередатчика SSPBUF нужно что-то записать, а после окончания пересылки из SSPBUF считать принятое. В простейшем случае обмен с картой имеет вид "команда - ответ" (рисунок 1.15)

Рисунок 1.1 4

4

На рисунках 1.13 – 1.15 используются обозначения: одна клетка - 8 бит; X - произвольно, Z - третье состояние, H - 0xFF, L - 0x00; Тр = 1÷8 байт, Тотв = 1÷… байт.

Обмен начинается с того, что микроконтроллер (МК) выставляет сигнал 0 на xCS, что и представлено на рисунке 1.15. Сначала посылается 6 байт команды - последовательно пишется в нужные байты регистра SSPBUF, перед записью очередного необходимо дождаться окончания передачи предыдущего (бит SSPSTAT,BF). Далее нужно дождаться ответа карты: пишется в SPI байт 0xFF и по окончании каждой передачи (контролируем SSPSTAT,BF), считываются принятые данные в SSPBUF. Первый байт, отличный от 0xFF, будет первым байтом ответа карточки (а для команд, которые используются в плеере, ответ всегда состоит из 1 байта). Данные, если требуется, передаются после ответа блоком заданной ранее длины.

Начало блока данных инициализируется также: его первый байт отличен от 0xFF. После окончания обмена нужно подать 1 на xCS.

Рисунок 1.15