- •До лабораторних робіт з дисципліни

- •Частина 2

- •1 Середовище сапр active–hdl

- •1.1 Загальні відомості про Active-hdl

- •1.2 Створення нового проекту

- •1.3 Створення нового документа (введення тексту програми)

- •1.4 Компіляція проекту

- •1.5 Моделювання

- •1.6 Порядок виконання роботи

- •1.8 Контрольні запитання

- •2 Мова програмування vhdl

- •2.1 Теоретична довідка

- •2.1.1 Опис об'єктів мовою vhdl

- •2.1.2 Типи даних і операції

- •2.1.3 Оператори мови vhdl

- •2.2 Порядок виконання роботи

- •2.4 Контрольні запитання

- •3 Індивідуальні завдання

- •3.1 Семисегментний індикатор

- •3.2 Клавіатурні прапори

- •3.3 Шифратор коду Хеммінга

- •3.4 Дешифратор адреси інтерфейсу ieee 1284

- •3.5 Дешифратор адреси плати pcl-711b

- •3.6 Режими адресації мікропроцесора Intel 8086

- •3.7 Система команд мікропроцесору Intel 4004

- •3.8 Приклад виконання роботи

- •3.8.1 Створення проекту

- •3.8.2 Створення компоненту

- •3.8.3 Створення файлу верхнього рівня

- •Література

- •6 9063 М. Запоріжжя, знту, друкарня, вул. Жуковського, 64

МІНІСТЕРСТВО ОСВІТИ І НАУКИ УКРАЇНИ

Запорізький національний технічний університет

МЕТОДИЧНІ ВКАЗІВКИ

До лабораторних робіт з дисципліни

“Архітектура ЕОМ”

для студентів спеціальностей 8.091 501 "Комп'ютерні системи та мережі” та 7.091 503 ”Спеціалізовані комп'ютерні системи” всіх форм навчання

Частина 2

2004

Методичні вказівки до лабораторних робіт з дисципліни “Архітектура ЕОМ” для студентів спеціальностей 8.091 501 ”Комп'ютерні системи та мережі” та 7.091 503 ”Спеціалізовані комп'ютерні системи” всіх форм навчання. Частина 2. /Укл. А.К. Тімовський, О.О.Голдобін. - Запоріжжя: ЗНТУ, 2004. – 50 с.

Укладачі:

А.К.Тімовський, доцент, к.т.н.,

О.О. Голдобін, асистент.

Рецензент:

Р.К. Кудерметов, доцент, к.т.н.

Відповідальний за випуск:

О.О. Голдобін, асистент.

Затверджено

на засіданні кафедри КСМ

Протокол № 7

від 23.02.2004

ЗМІСТ

1 СЕРЕДОВИЩЕ САПР ACTIVE–HDL 4

1.1 Загальні відомості про Active-HDL 4

1.2 Створення нового проекту 8

1.3 Створення нового документа (введення тексту програми) 11

1.4 Компіляція проекту 15

1.5 Моделювання 16

1.6 Порядок виконання роботи 20

1.7 Зміст звіту 21

1.8 Контрольні запитання 22

2 МОВА ПРОГРАМУВАННЯ VHDL 23

2.1 Теоретична довідка 23

2.1.1 Опис об'єктів мовою VHDL 23

2.1.2 Типи даних і операції 28

2.1.3 Оператори мови VHDL 30

2.2 Порядок виконання роботи 33

2.3 Зміст звіту 33

2.4 Контрольні запитання 33

3 ІНДИВІДУАЛЬНІ ЗАВДАННЯ 34

3.1 Семисегментний індикатор 34

3.2 Клавіатурні прапори 34

3.3 Шифратор коду Хеммінга 35

3.4 Дешифратор адреси інтерфейсу IEEE 1284 37

3.5 Дешифратор адреси плати PCL-711B 38

3.6 Режими адресації мікропроцесора Intel 8086 40

3.7 Система команд мікропроцесору Intel 4004 41

3.8 Приклад виконання роботи 43

3.8.1 Створення проекту 43

3.8.2 Створення компоненту 44

3.8.3 Створення файлу верхнього рівня 47

ЛІТЕРАТУРА 51

1 Середовище сапр active–hdl

ЛАБОРАТОРНА РОБОТА № 6

Мета роботи. Вивчити структуру VHDL–проекту і функціональні можливості системи автоматизованого проектування (САПР) Aldec Active–HDL.

1.1 Загальні відомості про Active-hdl

САПР Aldec Active–HDL є інтерактивним інтегрованим середовищем розробки і функціонально–структурного моделювання проектів цифрових систем (ЦС) на НВІС програмованої логіки (НВІС ПЛ). Її основними компонентами є компілятори мов опису апаратури і засоби функціонального моделювання проектів. Вбудовані додаткові засоби – текстовий редактор з функцією перевірки синтаксису, редактор кінцевих автоматів, бібліотека конструкцій мови, розвинута система допомоги та ін. – дозволяють значно скоротити час проектування і моделювання. Підтримуються мови опису апаратури VHDL, Verilog та EDIF (Electronic Design Interchange Format).

Можлива спільна робота Active–HDL і програмних засобів фірм–виробників НВІС ПЛ. Це дозволяє вести крізне проектування цифрової системи від початку до кінця: від тексту програми до готових виробів в базисі FPGA і CPLD.

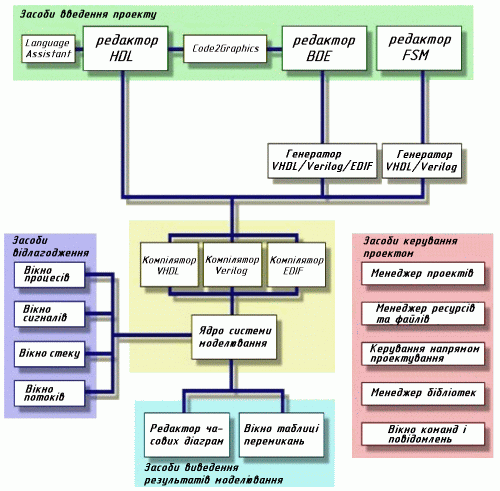

Користувачу доступні групи засобів розробки VHDL–проекту (див. рис. 1.1):

засоби введення проекту (Design Entry Tools);

засоби керування проектом (Control Tools);

засоби виведення результатів моделювання (Simulation Output Viewers);

засоби відлагодження проекту (Debugging Tools);

ядро системи та інструментальні засоби.

До засобів введення проекту належать функціональні одиниці САПР Active-HDL: текстовий редактор з перевіркою синтаксису (HDL Editor, HDE), графічний редактор логічних схем (Block Diagram Editor, BDE), графічний редактор кінцевих автоматів (State Diagram Editor, FSM), бібліотека конструкцій мови (Language Assistant), конвертер HDL–тексту в логічні схеми (Code2Graphics).

Засоби керування проектом: менеджер проектів (Design Explorer), менеджер файлів, ресурсів і структури проектів (Design Browser), менеджер керування напрямом проектування (Design Flow Manager), менеджер бібліотек (Library Manager), вікно команд і повідомлень (Console).

Функціональні одиниці, що є засобами виведення результатів моделювання: редактор часових діаграм (Waveform Editor), вікно таблиці перемикань (List Viewer).

До засобів відлагодження проекту належать: ядро системи моделювання (Simulator Kernel), вікно паралельних процесів (Processes), вікно сигналів користувача (Watch), стек викликів підпрограм (Call stack), вікно графічного відображення обміну інформацією усередині проекту (Dataflow).

Ядро системи та інструментальні засоби Active-HDL складають: генератор VHDL–проектів (VHDL Generator), генератор Verilog–проектів (Verilog Generator), генератор документів у форматі EDIF (EDIF Generator), компілятор мови VHDL (VHDL Compiler), компілятор мови Verilog (Verilog Compiler), компілятор EDIF (EDIF Compiler).

Рисунок 1.1 – Організація САПР Aldec Active–HDL

Часто буває достатньо скласти опис поведінки цифрової системи, алгоритму її роботи. З погляду автоматизації проектування ЦС, якщо не визначений базис її реалізації, такий підхід є більш раціональним.

Будь–який об'єкт може мати декілька варіантів алгоритмічного опису архітектури. Різні за формою (синтаксисом), але єдині за значенням (семантикою) представлення одного і того ж алгоритму можуть задавати однакову поведінку об'єкту, але мати різну структурну реалізацію.

Можливість за допомогою мови опису апаратури (HDL) різними способами задавати один і той же алгоритм дозволяє за допомогою САПР Active–HDL автоматично синтезувати відмінні за складністю (рівнем деталізації) функціонально–структурні описи ЦС. Перевага, яку дає використання САПР Active–HDL, полягає в тому, що користувач, за допомогою конструкцій мови опису апаратури, сам указує рівень деталізації моделі ЦС.

Відповідно до цього складається VHDL–проект – формальний опис поведінки ЦС на мові VHDL. Користувач сам вибирає рівень деталізації опису цифрової системи (абстракції) з чотирьох можливих:

поведінковий рівень (опис алгоритму роботи ЦС);

рівень регістрових передач (рівень RTL);

функціонально–логічний рівень (враховуються часові затримки розповсюдження сигналів);

рівень логічних елементів (враховується час спрацьовування логічних елементів).

VHDL–проект складається з логічних файлів (Design Files) опису компонентів ЦС, з’єднаних згідно формально визначеного закону функціонування ЦС. Логічні файли організовуються відповідно до ієрархії опису проектованої цифрової системи. Один з логічних файлів VHDL–проекту є файлом верхнього рівня ієрархії описів (Top–level Design File). Він грає роль організатора, що визначає архітектуру, склад ЦС і алгоритм її поведінки. Логічні файли нижніх рівнів ієрархії (Low–level Design files) містять детальний опис блоків і модулів ЦС. Ім'я проекту завжди співпадає з ім'ям логічного файлу верхнього рівня ієрархії проекту. До складу VHDL–проекту можуть бути залучені різноманітні допоміжні файли (Ancillary Files).

В САПР Active–HDL кожний проект зберігається в окремому каталозі, що зветься каталогом проекту. Проект і каталог, де він зберігається, мають однакові імена. Кожний каталог проекту містить файл опису проекту (розширення .ADF) і підкаталоги SRC, GENERIC і ін. Підкаталог SRC містить текстові файли мовою VHDL (розширення .VHD), файли діаграм автоматів (розширення .ASF) тощо. Підкаталог GENERIC містить робочі файли, які використовуються при компіляції і моделюванні.

Бібліотеки Active–HDL діляться на два класи: системні бібліотеки і бібліотеки проектів.

Системні бібліотеки поставляються разом з САПР Active–HDL і знаходяться в каталозі VLIB.

Бібліотеки проектів автоматично створюються окремо для кожного проекту і зберігаються в підкаталозі GENERIC проекту.

Кожна бібліотека складається з двох файлів: бібліотечного індексного файлу (розширення .INI) і головного бібліотечного файлу (розширення .MFG), що містить дані, що використовуються середовищем Active-HDL. В підкаталозі VLIB присутній також бібліотечний файл конфігурації LIBRARY.CFG, загальний для всіх бібліотек.

Системні бібліотеки з каталогу VLIB наперед скомпільовані і готові до вживання у VHDL-програмах у вигляді пакетів (расkages). Деякі вбудовані стандартні пакети (табл. 1.1) містять підпрограми, які використовуються ядром системи функціонального моделювання (Simulator Kernel).

Таблиця 1.1 – Вбудовані стандартні пакети САПР Active–HDL

Пакет |

Призначення |

STD.STANDARD |

Стандартний пакет VHDL загального призначення (стандарт IEEE Std. 1076) |

STD.TEXTIO |

Стандартний пакет VHDL текстових операцій (стандарт IEEE Std. 1076) |

IEEE.STD_LOGIC_1164 |

Підпрограми багаторівневої логіки (стандарт IEEE Std. 1164) |

IEEE.VITAL_TIMING |

Примітиви VITAL'95 (стандарт IEEE Std. 1076.4) |

IEEE.VITAL_PRIMITIVES |

Примітиви VITAL'95 (стандарт IEEE Std. 1076.4) |

IEEE.STD_LOGIC_ARITH |

Математичні підпрограми (стандарт IEEE Std. 1076.2) |

IEEE.STD_LOGIC_SIGNED |

Підпрограми IEEE (стандарт IEEE Std. 1076.5) |

IEEE.STD_LOGIC_UNSIGNED |

Підпрограми IEEE (стандарт IEEE Std. 1076.5) |

Під час установки середовища Active–HDL пропонується підключити бібліотеки, що призначені для підтримки розробки проектів ЦС в базисі НВІС ПЛ ведучих виробників (Actel, Altera, Atmel, Cypress, Lattice, Lucent, Quicklogic, Synopsys і Xilinx). САПР Active–HDL включає також бібліотеку вбудованих примітивів оптимізації часу моделювання SIMPRIM.

Разом з середовищем поставляється докладна контекстна довідка та електронні підручники. В табл. 1.2 приведений опис основних файлів довідкової системи Active–HDL. Великий обсяг довідкових матеріалів зосереджено в навчальній системі Enhanced VHDL Tutorial (EVITA). Її можна викликати з САПР Active–HDL за допомогою пункту меню Help → Interactive VHDL Tutorial. В Інтернеті мається електронна сторінка, що містить переклади деяких довідкових матеріалів – www.aldec.com.ua. Електронна адреса фірми Aldec – www.aldec.com.

Таблиця 1.2 – Довідкова система САПР Active–HDL

Короткий опис |

Ім'я файлу |

Загальні відомості про САПР Active–HDL |

RELNOTES |

Докладна інформація про склад і призначення САПР Active–HDL і її підсистем |

AVHDL |

Керівництво по створенню і моделюванню цифрових систем в Active–HDL |

TUTAVHDL |

Керівництво проектування за допомогою редактора BDE САПР Active–HDL |

TUTBDE |

Керівництво проектування за допомогою редактора FSM САПР Active–HDL |

TUTFSM |

Довідник з мови VHDL |

TUTVHDL |

Опис засобів верифікації VHDL–проектів САПР Active–HDL |

TUTTBCH |

Розглянемо докладніше процес розробки VHDL–проекту нескладної ЦС в САПР Active–HDL. Наприклад треба виконати функціональне моделювання поведінки демультиплексора DM(3), таблиця дійсності якого наведена в табл. 1.3.

Таблиця 1.3 – Таблиця дійсності демультиплексору DM(3)

Входи |

Виходи |

||||||||||

w |

x(2) |

x(1) |

x(0) |

y(7) |

y(6) |

y(5) |

y(4) |

y(3) |

y(2) |

y(1) |

y(0) |

0 |

X |

x |

x |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |