- •1.Архитектуры вычислительных систем.

- •2.Архитектура многопроцессорных систем.

- •3.Классификация вычислительных систем.

- •4.Классификация процессоров.

- •5.Регистровая модель процессора x86.

- •6.Режимы работы процессора 80386.

- •1.Реальный режим

- •2. Защищенный режим

- •7.Процессор х86: непосредственная и регистровая адресация.

- •8.Процессор х86: прямая адресация и прямая со сдвигом.

- •9.Процессор х86: косвенная адресация и косвенная со сдвигом.

- •10.Процессор х86: индексная адресация и индексная с масштабированием.

- •11.Размещение в памяти многомерных статических массивов и доступ к их элементам.

- •15.Процессор х86: инструкции копирования данных.

- •16.Процессор х86: инструкции ввода-вывода.

- •17.Представление целых чисел: прямой код, дополнительный код, bsd.

- •18.Процессор х86: инструкции сложения, сложения с переносом.

- •19.Процессор х86: сложение чисел в формате bcd.

- •20.Процессор х86: инструкции вычитания, вычитания с заемом.

- •21.Процессор х86: инструкции умножения.

- •22.Процессор х86: инструкция деления.

- •23.Процессор х86: операции расширения знакового бита.

- •24.Процессор х86: поразрядные логические инструкции, использование масок.

- •25.Процессор х86: инструкции сдвига. Умножение и деление на константы.

- •26.Процессор х86: инструкции цикла. Отличие от циклах в языках высокого уровня.

- •27.Процессор х86: Ожидание готовности пу с тайм-аутом на основе цикла.

- •28.Процессор х86: безусловный переход и виды меток.

- •29.Процессор х86: вызов процедуры и прерывания (рамка стека функции в с).

- •30.Процессор х86: инструкции условного перехода.

- •31.Процессор х86: строковый примитив копирования данных.

- •32.Процессор х86: строковые примитивы сравнения данных, сканирования данных и заполнения данных.

- •33.Сегменты реального и защищенного режима. Глобальная и локальная таблицы дескрипторов.

- •34.Механизм преобразования линейного адреса в физический в процессоре x86.

- •46.Математический сопроцессор: инструкции вычисления функций.

- •47. Математический сопроцессор: инструкции сравнения и условный переход по результатам сравнения

- •48.Математический сопроцессор: регистры управления и состояния.

- •49.Математический сопроцессор: исключения и их маскирование.

- •50. Дисковые накопители. Логическая и физическая геометрия жесткого диска, линейная адресация.

- •51. Разделы жесткого диска. Осуществление загрузки.

- •53. Стек tcp/ip и его соответсвие 7 уровневой модели osi iso.

- •54.Пример передачи и приема пакета в стеке tcp/ip.

- •55. Ip и mac адреса. Служба arp. Классы ip адресов.

- •56.Маршрутизация и таблицы маршрутизатора.

- •57.Доменные имена и служба dns.

- •58.Статические и динамические ip адреса. Служба dhcp.

25.Процессор х86: инструкции сдвига. Умножение и деление на константы.

Команда: |

SAR приемник, счетчик |

Назначение: |

Арифметический сдвиг вправо |

Команда: |

SAL приемник, счетчик |

Назначение: |

Арифметический сдвиг влево |

Команда: |

SHR приемник, счетчик |

Назначение: |

Логический сдвиг вправо |

Команда: |

SHL приемник, счетчик |

Назначение: |

Логический сдвиг влево |

Процессор: |

8086 |

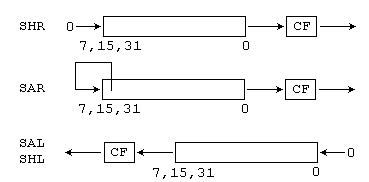

Эти четыре команды выполняют двоичный сдвиг приемника (регистр или переменная) вправо (в сторону старшего бита) или влево (в сторону младшего бита) на значение счетчика (число или регистр CL, из которого учитываются только младшие пять бит, которые могут принимать значения от 0 до 31), Операция сдвига на 1 эквивалентна умножению (сдвиг влево) или делению (сдвиг вправо) на 2. Так, число 0010b (2) после сдвига на 1 влево превращается в 0100b (4). Команды SAL и SHL выполняют одну и ту же операцию (на самом деле это одна и та же команда) — на каждый шаг сдвига старший бит заносится в CF, все биты сдвигаются влево на одну позицию, и младший бит обнуляется. Команда SHR выполняет прямо противоположную операцию: младший бит заносится в CF, все биты сдвигаются на 1 вправо, старший бит обнуляется. Эта команда эквивалентна беззнаковому целочисленному делению на 2. Команда SAR действует по аналогии с SHR, только старший бит не обнуляется, а сохраняет предыдущее значение, так что, например, число 11111100b (-4) перейдет в 11111110b (-2). SAR, таким образом, эквивалентна знаковому делению на 2, но, в отличие от IDIV, округление происходит не в сторону нуля, а в сторону отрицательной бесконечности. Так, если разделить -9 на 4 с помощью IDIV, результат будет -2 (и остаток -1), а если выполнить арифметический сдвиг вправо числа -9 на 2, результат будет -3. Сдвиги больше чем на 1 эквивалентны соответствующим сдвигам на 1, выполненным последовательно. Схема всех сдвиговых операций приведена на рис. 7.

Рис. 7. Сдвиговые операции

Сдвиги на 1 изменяют значение флага OF: SAL/SHL устанавливают его в 1, если после сдвига старший бит изменился (то есть старшие два бита исходного числа не были одинаковыми), и в 0, если старший бит остался тем же. SAR устанавливает OF в 0, и SHR устанавливает OF в значение старшего бита исходного числа. Для сдвигов на несколько бит значение OF не определено. Флаги SF, ZF, PF устанавливаются всеми сдвигами в соответствии с результатом, значение AF не определено (кроме случая, если счетчик сдвига равен нулю, в котором ничего не происходит и флаги не изменяются).

В процессорах 8086 непосредственно можно было задавать в качестве второго операнда только число 1 и при использовании CL учитывать все биты, а не только младшие 5, но уже начиная с 80186 эти команды приняли свой окончательный вид.

Команда: |

SHRD приемник, источник, счетчик |

Назначение: |

Сдвиг повышенной точности вправо |

Команда: |

SHLD приемник, источник, счетчик |

Назначение: |

Сдвиг повышенной точности влево |

Процессор: |

80386 |

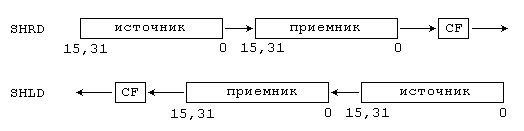

Приемник (регистр или переменная) сдвигается влево (в случае SHLD) или вправо (в случае SHRD) на число бит, указанное в счетчике (число или регистр CL, откуда используются только младшие 5 бит, которые могут принимать значения от 0 до 31). Старший (для SHLD) или младший (в случае SHRD) бит не обнуляется, а считывается из источника (регистр), значение которого не изменяется. Например, если приемник содержал 00101001b, источник 1010b, счетчик равен 3, SHRD даст в результате 01000101b, a SHLD — 01001101b (см. рис. 8).

Рис. 8. Сдвиги двойной точности

Флаг OF устанавливается при сдвигах на 1 бит, если изменился знак приемника, и сбрасывается, если знак не изменился; при сдвигах на несколько бит флаг OF не определен. Во всех случаях SF, ZF и PF устанавливаются в соответствии с результатом и AF не определен, кроме случая со сдвигом на 0 бит, в котором значения флагов не изменяются. Если счетчик больше, чем разрядность приемника, — результат и все флаги не определены.

Команда: |

ROR приемник, счетчик |

Назначение: |

Циклический сдвиг вправо |

Команда: |

ROL приемник, счетчик |

Назначение: |

Циклический сдвиг влево |

Команда: |

RCR приемник, счетчик |

Назначение: |

Циклический сдвиг вправо через флаг переноса |

Команда: |

RCL приемник, счетчик |

Назначение: |

Циклический сдвиг влево через флаг переноса |

Процессор: |

8086 |

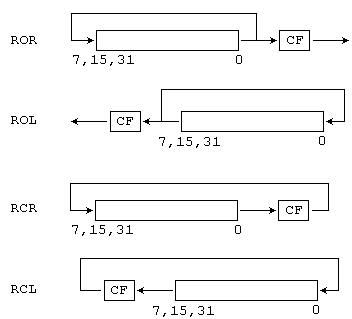

Эти команды осуществляют

циклический сдвиг приемника (регистр

или переменная) на число бит, указанное

в счетчике (число или регистр CL, из

которого учитываются только младшие

пять бит, принимающие значения от 0 до

31). При выполнении циклического сдвига

на 1 команды ROR (ROL) сдвигают каждый бит

приемника вправо (влево) на одну позицию,

за исключением самого младшего (старшего),

который записывается в позицию самого

старшего (младшего) бита. Команды RCR и

RCL выполняют аналогичное действие, но

включают флаг CF в цикл, как если бы он

был дополнительным битом в приемнике

(рис. 9).

Рис. 9. Циклические сдиги

После выполнения команд циклического сдвига флаг CF всегда равен последнему вышедшему за пределы приемника биту, флаг OF определен только для сдвигов на 1 — он устанавливается, если изменилось значение самого старшего бита, и сбрасывается, если старший бит не изменился. Флаги SF, ZF, AF и PF не изменяются.

Коротко из методички №2.

Операции сдвига, как и следует из их названия, осуществляют сдвиг операнда приемника вправо или влево на заданное число битов. Приемником может быть регистр или объект в памяти, источником – непосредственное значение, либо регистр cl.

Основное назначение операций сдвига – осуществление быстрого умножения и деления. Как в десятичной системе счисления дописывание нулей справа, т.е. сдвиг числа влево, соответствует умножению на 10, 100, 1000 и т.д., так в двоичной системе счисления дописывание нулей справа соответствует умножению на 2, 4, 8 и т.д. И наоборот, отбрасывание разрядов справа, т.е. сдвиг вправо, соответствует целочисленному делению на 10, 100, 1000 и т.д. в десятичной системе счисления и на 2, 4, 8 и т.д. - в двоичной. Поэтому практически всегда, когда в целочисленных расчетах встречается умножение или деление на константу, являющуюся целой степенью числа 2, они заменяются операциями сдвига. Кроме того, современные оптимизирующие компиляторы заменяют операции целочисленного умножения и деления на константу последовательностями сдвигов и сложений или вычитаний.

Для сдвигов беззнаковых операндов влево и вправо используются операции логического сдвига с мнемокодами shl и shr – соответственно, а для знаковых - операции арифметического сдвига с мнемокодами sal и sar – соответственно. Мнемокоды sal и shl соответствуют одной и той машинной операции, при которой на освободившиеся места справа записываются нули, и имеют различные обозначения только для симметрии. При логическом сдвиге вправо на освободившиеся места слева записываются нули, а при арифметическом – знаковый бит.

Например:

short i,j;

asm{

sal i, 4 // умножение числа i на 16

shr ax, 2 // деление содержимого рег ax на 4

mov ax, j

sal ax, 2

add j, ax // умножение числа j на 5

}