- •Вопрос 1 – Мультиплексор. Принцип построения и работы мультиплексора.

- •Вопрос 2 – Сумматор. Принцип построения и работы сумматора. Правила сложения двоичных чисел.

- •Вопрос 3 – Счетчики импульсов, принцип построения и работы.

- •Вопрос 4 – Асинхронный rs триггер. Принцип построения и работы, таблица истинности, временная диаграмма.

- •Вопрос 5 – Синхронный rs триггер. Принцип построения и работы, таблица истинности, временная диаграмма.

- •Вопрос 6 – d триггер. Принцип построения и работы, таблица истинности, временная диаграмма.

- •Вопрос 7 – t триггер. Принцип построения и работы, таблица истинности, временная диаграмма.

- •Вопрос 8 – jk триггер. Принцип работы, таблица истинности, временная диаграмма.

- •Вопрос 9 – Схемотехническая реализация логического элемента 2и-не структуры ттл. Принцип его работы.

- •Вопрос 10 – Схемотехническая реализация логического элемента 2или-не структуры ттл. Принцип его работы.

- •Вопрос 11 – Схемотехническая реализация логического элемента 2и-не структуры кмоп. Принцип его работы.

- •Вопрос 12 – Схемотехническая реализация логического элемента 2или-не структуры кмоп. Принцип его работы.

- •Вопрос 13 – Основы цифровых устройств, представление информации в цифровых устройствах.

- •Вопрос 14 – Теоретические основы проектирования цифровых устройств, операция дизъюнкции, операция инверсии.

- •Вопрос 15 – Теоретические основы проектирования цифровых устройств, операция конъюнкции, операция инверсии.

- •Вопрос 16 – Способы представления логических функций, построение логической схемы по заданной функции.

- •Вопрос 17 – Минимизация логических функций на основе метода карт Карно.

- •Вопрос 18 – Синтез комбинационных устройств (дешифратор двоично-десятичного кода в семисегментный код).

- •Вопрос 19 – Цифровые счетчики, принцип построения и работы, модуль счета.

- •Вопрос 20 – Дифференциальный каскад, схема, принцип работы.

- •Вопрос 21 – Операционный усилитель, структурная схема. Ачх.

- •Вопрос 22 – Инвертирующее включение оу.

- •Вопрос 23 – оу, назначение, не инвертирующее включение.

- •Вопрос 24 – Инвертирующий сумматор на основе оу.

- •Вопрос 25 – Усилители электрических сигналов, структурная схема, ачх.

- •Структура усилителя

- •Вопрос 26 – Усилительный каскад на транзисторе, режим по постоянному току.

- •Вопрос 27 – Биполярный транзистор, принцип работы.

- •Вопрос 28 – Биполярный транзистор, входная и семейство выходных характеристик.

- •Вопрос 29 – Полевой транзистор с управляющим p-n переходом, принцип работы, характеристики.

- •Вопрос 30 – Полевой транзистор с изолированным затвором, принцип работы, характеристики.

- •Вопрос 31 – Полупроводниковые стабилитроны, вольтамперная характеристика, основные параметры, применение.

- •Параметры

- •Вопрос 32 – Выпрямительные диоды, вольтамперная характеристика, основные параметры, применение.

- •Характеристики

- •Вопрос 33 – Параметрический стабилизатор напряжения, схема, принцип работы, основные параметры стабилизатора.

- •Параллельный параметрический стабилизатор на стабилитроне

Вопрос 4 – Асинхронный rs триггер. Принцип построения и работы, таблица истинности, временная диаграмма.

RS-триггер, или SR-триггер — триггер, который сохраняет своё предыдущее состояние при нулевых входах и меняет своё выходное состояние при подаче на один из его входов единицы.

При подаче единицы на вход S (от англ. Set — установить) выходное состояние становится равным логической единице. А при подаче единицы на вход R (от англ. Reset — сбросить) выходное состояние становится равным логическому нулю. Состояние, при котором на оба входа R и S одновременно поданы логические единицы, в простейших реализациях является запрещённым (так как вводит схему в режим генерации), в более сложных реализациях RS-триггер переходит в третье состояние QQ=00. Одновременное снятие двух «1» практически невозможно. При снятии одной из «1» RS-триггер переходит в состояние, определяемое оставшейся «1». Таким образом RS-триггер имеет три состояния, из которых два устойчивых (при снятии сигналов управления RS-триггер остаётся в установленном состоянии) и одно неустойчивое (при снятии сигналов управления RS-триггер не остаётся в установленном состоянии, а переходит в одно из двух устойчивых состояний).

S |

R |

Q(t) |

Q(t) |

Q(t+1) |

Q(t+1) |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

не определено |

не определено |

1 |

1 |

1 |

0 |

не определено |

не определено |

Условное графическое обозначение асинхронного RS-триггера

Вопрос 5 – Синхронный rs триггер. Принцип построения и работы, таблица истинности, временная диаграмма.

C |

S |

R |

Q(t) |

Q(t+1) |

0 |

x |

x |

0 |

0 |

1 |

1 |

|||

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

не определено |

1 |

1 |

1 |

1 |

не определено |

Алгоритм функционирования синхронного RS-триггера можно представить формулой

![]()

где x — неопределённое состояние.

Условное графическое обозначение синхронного RS-триггера

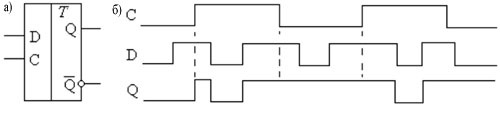

Вопрос 6 – d триггер. Принцип построения и работы, таблица истинности, временная диаграмма.

D |

Q(t) |

Q(t+1) |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

D-триггер в основном используется для реализации защёлки. Так, например, для снятия 32 бит информации с параллельной шины, берут 32 D-триггера и объединяют их входы синхронизации для управления записью информации в защёлку, а 32 D входа подсоединяют к шине.

В одноступенчатых D-триггерах во время прозрачности все изменения информации на входе D передаются на выход Q. Там, где это нежелательно, нужно применять двухступенчатые (двухтактные, Master-Slave, MS) D-триггеры.

Условное графическое обозначение D-триггера со статическим входом синхронизации С.