- •Введение.

- •1. Основы построения эвм. Основные определения.

- •2. Принципы действия эвм. Принципы программного управления.

- •Страница–словарь.

- •4. История развития вычислительной техники. Поколения эвм.

- •«Компьютер... XVII века»

- •5. Основные параметры эвм.

- •1. Запоминающие устройства эвм.

- •1.1. Типы зу и их основные характеристики.

- •1.2. Оперативные запоминающие устройства.

- •1.2.1. Общие принципы организации озу.

- •1.2.2. Структурная организация блока памяти.

- •1.2.3. Полупроводниковые интегральные зу с произвольным обращением.

- •1.2.4. Модули памяти и элементы памяти (бис).

- •1.2.5. Система электрических параметров полупроводниковых бис зу.

- •1.2.6. Контроль функционирования бис зу.

- •1.2.7. Организация многоблочной оперативной памяти.

- •1.2.8. Организация озу с многоканальным доступом.

- •1.2.9. Ассоциативные зу.

- •1.3. Сверхоперативные зу.

- •1.3.1. Назначение и типы созу.

- •1.3.2. Организация созу с прямой адресацией.

- •1.3.3. Организация стекового и магазинного созу.

- •1.3.4. Организация ассоциативных созу.

- •1.3.5. Оценка эффективности использования созу в процессоре.

- •1.4. Постоянные зу.

- •1.5. Виртуальная память.

- •Логическое распределение оперативной памяти в персональных компьютерах (Intel/pc).

- •1.6.1. Стандартная оперативная память.

- •1.6.1.1.Таблица векторов прерываний.

- •1.6.1.2. Область данных bios.

- •1.6.1.3. Область для операционной системы.

- •1.6.1.4. Основная область памяти.

- •2. Арифметико-логические устройства эвм

- •2.1. Типы арифметических устройств и их структуры.

- •2.2. Организация алу параллельного действия при работе над числами в естественной форме.

- •2.2.1. Суммирование и вычитание чисел при использовании накапливающего сумматора.

- •2.2.2. Принципы построения алу для сложения и вычитания на комбинационных суммах.

- •2.2.3. Организация алу (параллельного действия) в режиме умножения чисел с фиксированной запятой.

- •2.2.4. Аппаратные способы ускорения умножения в организации алу.

- •2.2.5. Алгоритмические (логические) способы ускорения умножения в организации алу.

- •2.2.6. Организация алу параллельного действия в режиме деления чисел с фиксированной запятой.

- •2.2.7. Организация алу при реализации логических операций и операций специальной арифметики.

- •2.3. Организация алу параллельного действия при работе над числами в нормальной форме.

- •2.3.1. Принцип построения и работы алу при суммировании и вычитании чисел в нормальной форме.

- •2.3.2. Направления и методы ускорения операций над числами с плавающей запятой.

- •2.4. Организация алу, работающих в двоично-десятичных кодах.

- •2.5.Об экзотических формах представления чисел. Логарифмическая форма:

- •Трансформирующаяся запятая.

- •Инверсная запятая.

- •2.6. Итеративные методы деления.

- •3. Процессоры.

- •3.1. Система команд эвм.

- •3.1.1. Структура и форматы команд.

- •3.1.2. Список команд.

- •3.1.3. Способы адресации.

- •3.2. Устройства управления.

- •3.2.1. Организация цуу (на примере гипотетической одноадресной эвм).

- •3.2.2. Принципы формирования уфс.

- •3.2.3. Организация микропрограммных устройств управления.

- •3.3. Организация внутрипроцессорных систем ввода-вывода информации.

- •3.3.1. Основные понятия и определения.

- •3.3.2. Способы обмена данными между ядром малой эвм и периферийными устройствами.

- •3.3.3. Программно управляемые способы передачи данных.

- •3.3.3.1. Простые типы передачи.

- •3.3.3.2. Последовательность событий при прерываниях.

- •3.3.3.3. Идентификация прерывающего устройства.

- •3.3.4. Организация прямого доступа к памяти.

- •4. Основы вычислительных конвейеров.

- •4.1. Введение в архитектурные принципы конвейерных процессоров и эвм.

- •Конвейерные сумматоры

- •Конвейерный умножитель

- •5. Архитектура сигнальных процессоров.

- •5.1. Введение. Основные задачи обработки сигналов. Методы обработки сигналов.

- •5.2. Основные характеристики и базовая архитектура семейства adsp-21xx

- •5.2.1. Общие сведения о составе функциональных устройств

- •5.2.2. Базовая архитектура.

- •5.2.3. Средства разработчиков для процессоров семейства.

- •5.3. Интерфейс процессоров adsp-21xx с памятью.

- •5.3.1. Интерфейс с загрузочной памятью.

- •5.3.2. Интерфейс с памятью программ.

- •5.3.3. Интерфейс с памятью данных.

- •5.4. Архитектура операционных устройств.

- •5.4.1. Арифметико-логическое устройство.

- •5.4.2. Умножитель/накопитель mac.

- •5.4.3. Устройство сдвига shifter.

-

3. Процессоры.

Одно определение понятия процессора было дано во введении.

Процессор – функциональный блок ЭВМ, предназначенный для логической и арифметической обработки информационных потоков на основе принципа программного управления.

Процессор выполняет функцию выполнения программ (помещаются в ОЗУ) путем выборки, проверки и последовательного выполнения действий, предписанных командами. По-другому: процессор исполняет предписанные командами действия над кодированной информацией в соответствии с программами.

<107>

В современных компьютерах процессор (ядро ЭВМ) есть не формальное объединение АЛУ и ЦУУ, а результат развития структуры ЭВМ, призванный обеспечивать высокое быстродействие и широкие функционально-логические возможности обработки информации. В частности, появление новых ЭВМ привело к необходимости появления компьютере и в процессоре

системы прерывания;

новых уровней памяти;

средств защиты памяти;

использования специальных типов индексации, адресации информации;

кэш-память команд, ветвлений, предсказаний обменов и т.д.;

специальных процедур управления вычислительным процессом

и т.д.

…

Все эти подсистемы и устройства частично или целиком входят в процессор. Главное же новое структурное явление в процессоре – СОЗУ.

Поэтому ныне процессор имеет более развитую структуру, повторяющую в известном смысле структуру машины фон Неймана.

Но мы не будем касаться новых направлений в организации процессоров. Их осветят в полной мере в курсе «Микропроцессоры».

<108>

-

3.1. Система команд эвм.

Система команд ЭВМ определяется структурой и форматами команд, а также списком (перечнем) команд и способами адресации.

Командой называется некоторым образом кодированная информация, определяющая выработку в ЭВМ последовательностей сигналов, предназначенных для выполнения определенной операции (действия) машины над заданными числовыми и нечисловыми кодами.

Поскольку, в конечном счёте, команда тем или иным образом вводится в ЭВМ и ею воспринимается, то конечный вид команды – цифровой код.

Соответственно, конечной формой программы работы ЭВМ (программу можно определить как специальным образом формализованный алгоритм обработки информации) является программа в кодированных командах.

<109>

-

3.1.1. Структура и форматы команд.

В соответствии с введенным определением команды, структура последней имеет операционную и адресную части (что и над какими данными надо сделать), а также служебную часть, определяющие особенность выполнения данной команды (модификацию) в зависимости от значений тех или иных признаков.

Адрес (адреса), содержащийся в адресной части команды, в наиболее распространенном случае указывает номер ячейки ОЗУ, в которой записано (хранится) участвующее в операции число (его код) – слагаемое, множимое, делимое и т.д., код нечисловой информации (адрес, строка символов, состояние устройства и т.д.) Обобщённо и для простоты обычно говорят: в ЗУ хранятся операнды.

Однако, если говорить о команде как о предписании, то наиболее полная его форма должна указывать не только адреса всех чисел, участвующих в операции, но и адрес ячейки, в которую следует поместить результат, а также адрес источника следующей команды. Это перечисление подводит к необходимости иметь в команде четыре адреса.

И на самом деле, такие четырехадресные команды существуют. С такого «формата» команды «стартовали». Но адресов в команде может быть и меньше, и больше!

Адрес источника следующей команды может отсутствовать, поскольку программу (последовательность команд) наиболее естественно и целесообразно размещать в некотором массиве рядом расположенных ячеек ЗУ. И если команды записаны последовательно (от номера 1 до номера n), то весьма просто аппаратно (счетчиком!) реализовать смену адреса ячейки-источника очередной команды. Заметим, что такой порядок выборки называется естественным, тогда как при задании адреса команды в команде порядок выборки именуется принудительным. Заметим также, что использование естественного порядка выборки команд приводит к необходимости введения специальных команд, изменяющих порядок вычислений (путём изменения содержимого счетчика номеров ячеек команд). Это необходимо для обеспечения алгоритмической вычислимости. При принудительном порядке выборки специальные команды не нужны, т.к. каждая команда «меняет» порядок выборки.

Число адресов выборки команд может быть и больше одного, за счет чего можно организовать ускорение вычисления, повышение надежности вычислений и др. Но все это характерно лишь для специальных ЭВМ.

<110>

Адрес результата операции может отсутствовать по следующим «причинам»:

-

таким адресом является адрес одного из операндов;

-

адресом является некоторый заранее оговоренный код-указатель, соответствующий месту хранения промежуточных результатов, либо месту вывода результатов вычислений;

-

адресом является модифицированный с помощью служебной части команды адрес одного из операндов, либо, даже, адрес выполняемой команды;

-

адрес был указан ранее в другой команде и др.

Остались два операнда.

Вспомним, что обработка информации в ЭВМ последовательная, т.е. обработка может быть сведена к ситуации, при которой результат выполнения каждой операции является операндом при выполнении последующей.

Эти рассуждения приводят нас уже к одноадресной команде. Но команда может быть и вообще безадресной. В этом последнем случае возможно несколько «вариантов отсутствия» адресов:

-

адрес формируется аппаратно, аналогично адресу выборки следующей команды;

-

память безадресная, например, стековая;

-

ведется сложная последовательная обработка некоторого введенного на начальном этапе работы числа (например,

);

); -

операнды в памяти расположены попеременно с командами и др.

Так из четырёх адресов не остаётся ни одного. Это «крайность». Число адресов в команде регламентируется только разработчиком системы команд. В редких случаях число адресов может быть и более четырёх.

<111>

Многоадресные команды имеют то назначение, что с их помощью организуются многооперандные операции (суммирование более чем двух слагаемых, групповая пересылка и др.). Но это тоже экзотика, встречающаяся только в специализированных ЭВМ.

А на что же влияет адресность? Или здесь царит произвол, и каждый разработчик ЭВМ творит, что хочет?

Адресность влияет на:

-

Быстродействие. Легко показать, что в простейшем случае суммирования

время выполнения (полное) и при использовании трехадресной, и при использовании одноадресной команды одинаково и равно

.

.

Но это справедливо только для исчисления времени доступа к операндам в двуместных (бинарных) операциях. И здесь оказывается весьма сложной задачей не эмпирически оценить влияние адресности.

-

Емкость ЗУ. Если емкость ЗУ

ячеек,

то для задания адреса любой ячейки надо

иметь

ячеек,

то для задания адреса любой ячейки надо

иметь

-

разрядный код; тогда для трехадресной

машины:

-

разрядный код; тогда для трехадресной

машины:

,

,

где

– число разрядов, отводимых под операции

(всего операций

– число разрядов, отводимых под операции

(всего операций

– p);

m

мод

–

число разрядов под признаки модификации

(можно вычислить

–

число разрядов под признаки модификации

(можно вычислить

аналогично m опер); общая тенденция развития ЭВМ такая, что растут p число

модификаций, а значит и m опер, и m мод, а длина команды ограничивается

аппаратурой, что и влечёт за собой отказ от третьего и второго адресов;

при использовании одноадресных команд вместо 3-адресных постоянно

требуются простые пересылки операндов из ОЗУ в АЛУ, из АЛУ и ОЗУ и

др.; в трехадресных они тоже требуются иногда из алгоритмических

соображений, а поскольку их длина (и информационная емкость) больше, то

это резко снижает эффективность использования ОЗУ;

-

Особенности АЛУ. Для одноадресной ЭВМ результат должен сохраняться в

операционном блоке (в сумматоре, либо в специальном регистре); вообще, чем меньше адресов, тем несколько выше аппаратурные затраты.

<112>

Эмпирическое сравнение:

KI – среднестатистическое количество команд в программах;

QI – среднестатистический объем занимаемый программой в ОЗУ, в битах, байтах и т.д.;

ТI – среднестатистическое время выполнения программы.

Индекс указывает на исключительное использование одного, двух и трёх адресов в командах.

Тогда:

и

и

и

и

.

.

К этому следует добавить: когда меньше адресность, несколько труднее программировать.

Общие тенденции: уменьшение адресности (в первую очередь для малых ЭВМ) и использование переменной адресности.

<113>

Структурно команды разбиваются на байты. Количество и сочетание байтов в различных частях команды (главным образом, в адресной части) может быть различным. Появляется гибкость и возможность расширения функциональных возможностей полей команд. Команды могут храниться в нескольких последовательных ячейках ОЗУ, причем их (команд) длина указывается в первом слове (дополнительная функция служебной части команды).

Формат команды – описание размеров и взаимного расположения структурных частей команды (полей). Поле – совокупность рядом расположенных функционально различных разрядов машинного слова.

При переменной адресности первым машинным словом прежде всего задается формат команды.

Для уяснения многих особенностей структур и форматов целесообразно немного углубиться в историю систем команд.

<114>

Система команд фирмы DEC (Digital Equipment Corporation).

В зависимости от тех или иных исходных предпосылок в описаниях выделяют от 6 до 9 основных форматов для этих ЭВМ. Взглянем на некоторые из них:

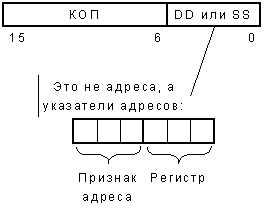

Рис. 3.1.1.01. Формат 1.

Здесь DD – поле адреса приемника результата операции; SS – поле адреса источника данных. По сути дела, это одноадресная команда.

Рис. 3.1.1.02. Формат 2.

Это двухадресная команда.

Рис. 3.1.1.03. Формат 3.

Это другая разновидность двухадресной команды, где R – трехразрядное

поле для записи номера регистра СОЗУ.

Рис. 3.1.1.04. Формат 5.

Одноадресная команда.

![]()

Рис. 3.1.1.05. Формат 9.

Это безадресная команда, с помощью которой выполняются операции управления прерыванием и специальные команды.

<115>

Рассмотрим теперь некоторые форматы команд IBM (всего их первоначально было 9).

Рис. 3.1.1.06. Формат RR.

Это короткая (двухбайтовая) команда, выполняющая операции над содержимым регистров СОЗУ.

Рис. 3.1.1.07. Формат RS (регистр-память).

Четыре байта, результат в регистре R3. Это трехадресная команда (несколько

необычен порядок расположения адресов); В2 – адрес базового регистра; D2 – величина смещения.

Рис. 3.1.1.08. Формат SS (память-память).

Шесть байт; L1 и L2 – указатели длин операндов; адресов всего два.

<116>

Исходная система команд Intel по утверждению разработчиков использовала всего три формата команд:

Рис. 3.1.1.1.09.

Но это лишь лукавый поверхностный взгляд. В поле КОП «спрятались» адреса регистров СОЗУ и быстро выяснялось, что существовало семь «процессорных» форматов поля КОП:

Рис. 3.1.1.10.

В заштрихованных полях содержатся собственно коды операций АЛУ. Другие обозначения:

DDD – поле приемника результата;

SSS – поле источника операнда;

RP – код регистровой пары;

CCC – указатель условия перехода;

NNN – адрес вектора прерывания.

Далее системы команд Intel развивались очень уродливо: в дело вмешались деньги. Весьма большие: стоимость используемого ПО Intel 8080 уже исчислялась миллиардами долларов.

Форматы команд процессоров для PC XT/AT достаточно разнообразны и многочисленны. Главные причины этого заключены в системе сегментации памяти, в разнообразии способов адресации, в возможности обрабатывать 8- и 16-разрядные данные, а также связаны с обширным списком операций, включая операции обработки строк данных. Длина команды может составлять от 1 до 6 байт, не считая возможного предшествующего команде байта префикса.

Большая часть форматов команд процессора приведена на рисунке:

Рис. 3.1.1.11.

<117>

Остановимся на описании полей в форматах команд, содержащих указатели длины операндов, указатели модификации, коды адресных регистров и т.п.

В первом байте команды всегда содержится код операции процессора (КОП), занимающий большее количество разрядов и указатели длины форматов. В отдельных случаях КОП может размещаться в постбайте в поле reg (характерно только для команд с одним операндом).

Функциональное назначение отдельных битов-указателей и битов-признаков таково:

w – признак длины формата данных; при w=0 длина операнда один байт, а при w=1 – машинное слово (два байта);

d - указатель одного из возможных мест запоминания результата операции (характерно только для команд с двумя адресами операндов);

s – признак длины непосредственного операнда в выполняемой команде; s=0 – «длинный» операнд, s=1 – «короткий».

v – указатель количества разрядов, на которое производится сдвиг в соответствующих командах; при v=0 сдвиг производится только на один разряд, а при v=1 – на количество разрядов, указанное в регистре CL (см. рис. 3.1.1.11).

Среди изображенных на рисунке форматов специально обращаем внимание на «длинный» шестибайтовый формат (рис. с литерой (в)), на формат, содержащий шестнадцатиразрядный адрес для команд с прямой адресацией (рис. с литерой (г)), и на формат, используемый в командах условных переходов (рис. с литерой (е)). На том же рисунке показан также формат постбайта, используемого главным образом для задания способа адресации одного или двух операндов. Постбайт содержит поле режима адресации – mod, поле кода регистров – reg и поле регистр/память – r/m, указывающее место размещения второго операнда.

Правило формирования исполнительного адреса по коду в поле r/m показано в таблице 1, причем при (mod)=00 смещение принимается равным нулю (внимание! Имеется одно исключение: при (r/m)=110 исполнительный адрес равен шестнадцатиразрядному смещению, указанному в команде); при (mod)=01 восьмиразрядное смещение, указанное в команде путем расширения знака превращается в шестнадцатиразрядное; при (mod)=10 в команде указывается шестнадцатиразрядное смещение; наконец, при (mod)=11 вторым исполнительным адресом является адрес регистра, кодируемый также, как и первый исполнительный адрес регистра (поле reg), но в поле r/m . Коды регистров в постбайте, а также в поле reg в формате на рис. а, приведены в таблице:

Таблица 1.

|

Коды полей reg и r/m при (mod)=11 |

Регистр |

|

|

При w=0 |

При w=1 |

|

|

000 |

AL |

AX |

|

001 |

CL |

CX |

|

010 |

DL |

DX |

|

011 |

BL |

BX |

|

100 |

AH |

SP |

|

101 |

CH |

BP |

|

110 |

DH |

SI |

|

111 |

BH |

DI |

С созданием фирмой Intel поколений 80386, 80486 и Pentium-процессоров форматы еще более головоломно усложнились:

Рис. 3.1.1.12. Общий формат команды.

Детальный комментарий здесь затруднителен, т.к. требует подробного рассмотрения организации памяти конкретного процессора и структуры самого процессора. Ограничимся отдельными замечаниями.

При выполнении отдельных команд разрядность операндов может меняться соответствующим префиксом размера операнда. В 32-битном режиме размеры операнда по умолчанию равны 8 и 32 бита. Если предполагается использование в команде 16-разрядных операндов, то в этом случае необходимо использовать префикс размера операнда.

Префикс размера операнда определяет размер внутрисегментного смещения. В 32-битном режиме смещения вычисляются как 32-разрядные адреса. Если в команде должен быть использован 16-разрядный адрес, то необходимо использовать префикс размера адреса.

Постбайт адресации md-reg-r/m используется для задания адресов операндов, один из которых обязательно должен находиться в регистре блока РОН, а второй может размещаться либо в регистре, либо в памяти. Кодировка полей md и r/m определяет способ вычисления адреса операнда в памяти. Для реализации некоторых способов адресации кроме постбайта в адресации используется дополнительный байт адресации SIB.

<118>