- •Введение.

- •1. Основы построения эвм. Основные определения.

- •2. Принципы действия эвм. Принципы программного управления.

- •Страница–словарь.

- •4. История развития вычислительной техники. Поколения эвм.

- •«Компьютер... XVII века»

- •5. Основные параметры эвм.

- •1. Запоминающие устройства эвм.

- •1.1. Типы зу и их основные характеристики.

- •1.2. Оперативные запоминающие устройства.

- •1.2.1. Общие принципы организации озу.

- •1.2.2. Структурная организация блока памяти.

- •1.2.3. Полупроводниковые интегральные зу с произвольным обращением.

- •1.2.4. Модули памяти и элементы памяти (бис).

- •1.2.5. Система электрических параметров полупроводниковых бис зу.

- •1.2.6. Контроль функционирования бис зу.

- •1.2.7. Организация многоблочной оперативной памяти.

- •1.2.8. Организация озу с многоканальным доступом.

- •1.2.9. Ассоциативные зу.

- •1.3. Сверхоперативные зу.

- •1.3.1. Назначение и типы созу.

- •1.3.2. Организация созу с прямой адресацией.

- •1.3.3. Организация стекового и магазинного созу.

- •1.3.4. Организация ассоциативных созу.

- •1.3.5. Оценка эффективности использования созу в процессоре.

- •1.4. Постоянные зу.

- •1.5. Виртуальная память.

- •Логическое распределение оперативной памяти в персональных компьютерах (Intel/pc).

- •1.6.1. Стандартная оперативная память.

- •1.6.1.1.Таблица векторов прерываний.

- •1.6.1.2. Область данных bios.

- •1.6.1.3. Область для операционной системы.

- •1.6.1.4. Основная область памяти.

- •2. Арифметико-логические устройства эвм

- •2.1. Типы арифметических устройств и их структуры.

- •2.2. Организация алу параллельного действия при работе над числами в естественной форме.

- •2.2.1. Суммирование и вычитание чисел при использовании накапливающего сумматора.

- •2.2.2. Принципы построения алу для сложения и вычитания на комбинационных суммах.

- •2.2.3. Организация алу (параллельного действия) в режиме умножения чисел с фиксированной запятой.

- •2.2.4. Аппаратные способы ускорения умножения в организации алу.

- •2.2.5. Алгоритмические (логические) способы ускорения умножения в организации алу.

- •2.2.6. Организация алу параллельного действия в режиме деления чисел с фиксированной запятой.

- •2.2.7. Организация алу при реализации логических операций и операций специальной арифметики.

- •2.3. Организация алу параллельного действия при работе над числами в нормальной форме.

- •2.3.1. Принцип построения и работы алу при суммировании и вычитании чисел в нормальной форме.

- •2.3.2. Направления и методы ускорения операций над числами с плавающей запятой.

- •2.4. Организация алу, работающих в двоично-десятичных кодах.

- •2.5.Об экзотических формах представления чисел. Логарифмическая форма:

- •Трансформирующаяся запятая.

- •Инверсная запятая.

- •2.6. Итеративные методы деления.

- •3. Процессоры.

- •3.1. Система команд эвм.

- •3.1.1. Структура и форматы команд.

- •3.1.2. Список команд.

- •3.1.3. Способы адресации.

- •3.2. Устройства управления.

- •3.2.1. Организация цуу (на примере гипотетической одноадресной эвм).

- •3.2.2. Принципы формирования уфс.

- •3.2.3. Организация микропрограммных устройств управления.

- •3.3. Организация внутрипроцессорных систем ввода-вывода информации.

- •3.3.1. Основные понятия и определения.

- •3.3.2. Способы обмена данными между ядром малой эвм и периферийными устройствами.

- •3.3.3. Программно управляемые способы передачи данных.

- •3.3.3.1. Простые типы передачи.

- •3.3.3.2. Последовательность событий при прерываниях.

- •3.3.3.3. Идентификация прерывающего устройства.

- •3.3.4. Организация прямого доступа к памяти.

- •4. Основы вычислительных конвейеров.

- •4.1. Введение в архитектурные принципы конвейерных процессоров и эвм.

- •Конвейерные сумматоры

- •Конвейерный умножитель

- •5. Архитектура сигнальных процессоров.

- •5.1. Введение. Основные задачи обработки сигналов. Методы обработки сигналов.

- •5.2. Основные характеристики и базовая архитектура семейства adsp-21xx

- •5.2.1. Общие сведения о составе функциональных устройств

- •5.2.2. Базовая архитектура.

- •5.2.3. Средства разработчиков для процессоров семейства.

- •5.3. Интерфейс процессоров adsp-21xx с памятью.

- •5.3.1. Интерфейс с загрузочной памятью.

- •5.3.2. Интерфейс с памятью программ.

- •5.3.3. Интерфейс с памятью данных.

- •5.4. Архитектура операционных устройств.

- •5.4.1. Арифметико-логическое устройство.

- •5.4.2. Умножитель/накопитель mac.

- •5.4.3. Устройство сдвига shifter.

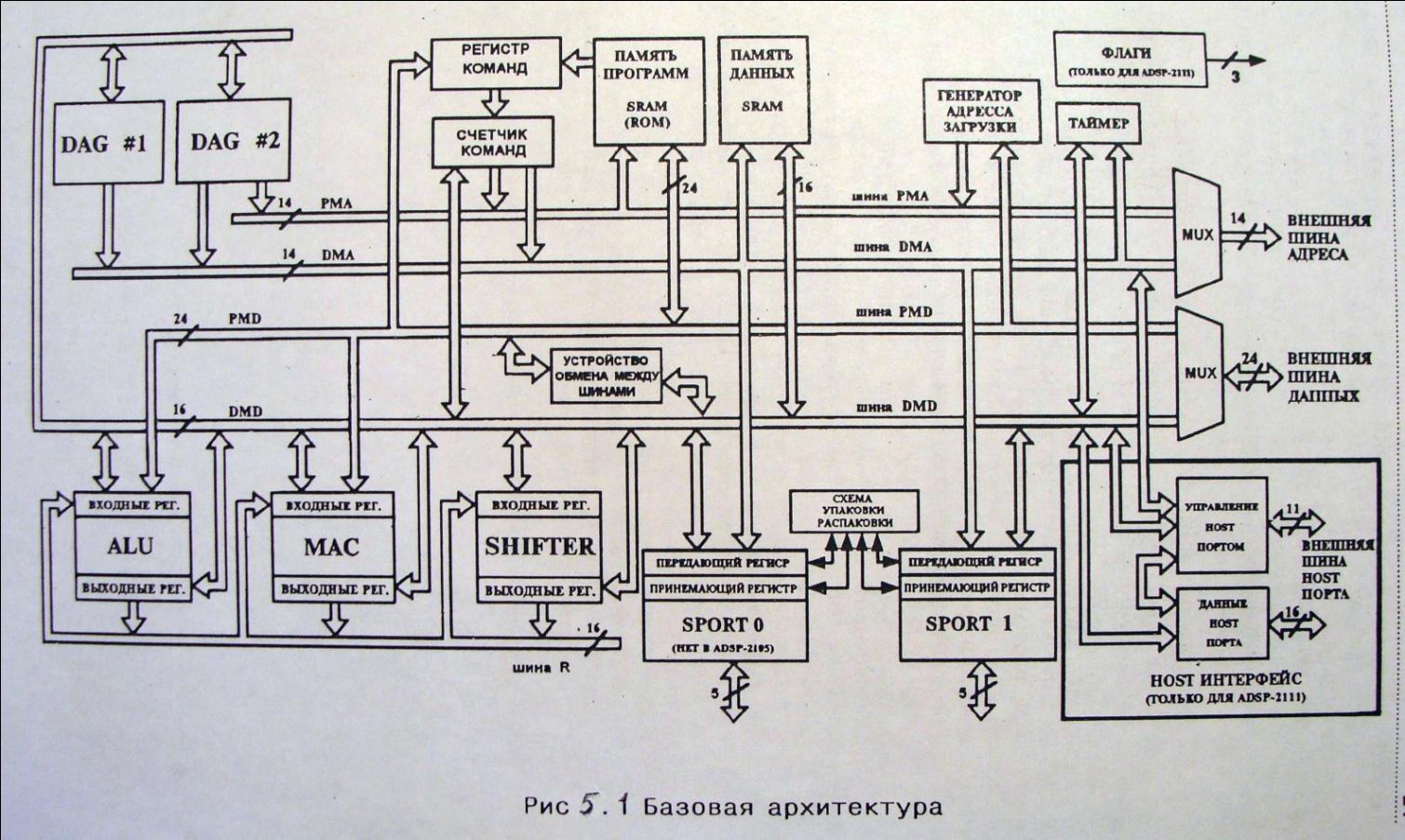

5.2.2. Базовая архитектура.

Обобщенно базовая архитектура процессоров семейства показана на рисунке 5.1.

Три независимых полнофункциональных операционных устройства были названы ранее. Операции реализуются над числами в разных форматах, в том числе над числами с плавающей запятой, занимающими более одного 16-разрядного слова. Операционные устройства реализован «бок о бок», что позволяет результату работы любого из них становится операндом другого в следующем цикле. С этой целью введена особая шина внутренних результатов – шина R.

Все три операционных устройства содержат входные и выходные регистры, которые доступны через внутреннюю шину данных памяти данных (DMD). Регистры обеспечивают буферизацию между операционными устройствами и памятью.

Два выделенных генератора адресов данных DAG1 и DAG2 обеспечивают формирование адресов памяти данных, когда данные пересылаются из выходных или во входные регистры операционных устройств. Каждый генератор запоминает до 4-х адресных указателей. Когда указатель используется для косвенной адресации, он может автоматически модифицироваться значением в заданном регистре после исполнения инструкции. Два генератора обеспечивают генерацию двух адресов данных в одном цикле, т.е. поддерживать двухадресные инструкции. С каждым указателем может быть ассоциирована длина для автоматической реализации кольцевых буферов. (Эта возможность также используется последовательными портами и аналоговым интерфейсом для автоматической передачи данных.)

Различия:

DAG1 может генерировать адреса только для памяти данных, но в его выходном адресе может меняться порядок следования битов перед выдачей на шину, что облегчает адресацию в алгоритмах radix-2 БПФ;

DAG2 может генерировать адреса, как для памяти данных, так и для памяти программ.

Функции счетчика команд выполняет генератор адресов команд, который не только инкрементацией, а многообразно формирует адреса инструкций для памяти программ. Он управляет регистром инструкций, который содержит исполняемую в данный момент команду. Регистр инструкций буферирует исполнение программы. Команды загружаются в регистр в течение одного цикла, а исполняются в течение следующего, одновременно с загрузкой следующей команды. Чтобы минимизировать циклы ожидания устройство выполняет условные переходы, вызовы и возвраты из подпрограмм за один цикл. Счетчик/генератор имеет внутренний счетчик вложенности циклов и стек циклов для работы без потерь времени.

Внутренние устройства процессоров связаны пятью шинами:

- шина адреса памяти данных DMA (Data Memory Address); шина имеет ширину 14 бит, что обеспечивает доступ к 16 Кб данных;

- шина адреса памяти инструкций PMA (Program Memory Address); шина имеет ширину 14 бит, что обеспечивает доступ к 16 Кб инструкций и данных;

- шина данных памяти данных DMD (Data Memory Data); шина имеет ширину 16 бит, что обеспечивает пересылку содержимого любого регистра процессора в любой другой регистр или в/из памяти в течение одного цикла; адрес памяти данных формируется из абсолютного значения, записанного в инструкции (абсолютная адресация), или из генератора адресов данных (косвенная адресация); только косвенная адресация возможна для адресации данных в памяти программ;

- шина данных памяти инструкций PMD (Program Memory Data); ширина этой шины – 24 бита, что обеспечивает загрузку 24-разрядной команды;

- шина внутренних результатов – шина R.

Первые четыре шины мультиплексированы наружу микросхемы в две шины – шину адреса и шину данных; адресное пространство выбирается сигналами BMS, DMS и PMS (все – активный низкий).

Шина PMD также может быть использована для пересылок данных в/из операционных устройств напрямую или через устройство обмена между шинами PMD и DMD. Устройство обмена позволяет пересылать данные с одной шины на другую и содержит логику сопряжения для преодоления разницы ширины в 8 бит.

Почти все процессоры семейства имеют по 2 двунаправленных последовательных порта (S-PORT) с двойной буферизацией. Эти порты используются для синхронной передачи данных и используют кадровые сигналы для контроля потоков данных. Каждый порт может тактироваться от внутреннего таймера или от внешней частоты. Сигналы кадровой синхронизации могут быть сгенерированы как самим портом, так и получены извне. Длина слова передачи может меняться от 3 до 16 бит. Один порт (S-PORT0) имеет многоканальные возможности, что позволяет получать и передавать слова данных из 24- или 32-словного потока битов. Другой порт (S-PORT1) может быть сконфигурирован для использования внешних сигналов прерывания IRQ1 и IRQ0 и внешних сигналов FO и FI (Flag out и Flag in).

Встроенный программируемый интервальный таймер обеспечивает периодическую генерацию прерываний «изнутри». 8-битный масштаб позволяет ему декрементировать содержимое 16-битного регистра-счётчика в диапазоне от одного до каждого 256-го командного цикла. Прерывание генерируется по обнулению регистра-счётчика. После этого регистр-счётчик автоматически загружается из 16-битного регистра интервала и отсчёт времени в таймере немедленно возобновляется.

Порт HIP – это параллельный порт ввода-вывода, позволяющий просто подсоединить хост-процессор. Через этот порт процессор ADSP-21xx может быть использован хост-процессором как периферийное устройство с отображением его на адресное пространство хост-процессора. Порт HIP работает параллельно и асинхронно с операционными устройствами и памятью процессора семейства и состоит из регистров через которые происходит обмен данными и статусной информацией (слова состояния и управления). Порт может быть настроен на 8- или 16-битные шины данных, на мультиплексированную шину адреса/данных или на раздельные шины, на раздельные строб-импульсы для чтения/записи или на строб-импульс чтения/записи и строб-импульс данных.

Аналоговый интерфейс процессоров (ADSP-21msp5x) состоит из входных усилителей, 16-битных сигма-дельта АЦП и ЦАП и дифференциального выходного усилителя. Набор регистров, отображённых на память процессора, служит для управления операциями аналоговой части и для передачи данных между аналоговой частью и остальными устройствами процессора.