- •Введение.

- •1. Основы построения эвм. Основные определения.

- •2. Принципы действия эвм. Принципы программного управления.

- •Страница–словарь.

- •4. История развития вычислительной техники. Поколения эвм.

- •«Компьютер... XVII века»

- •5. Основные параметры эвм.

- •1. Запоминающие устройства эвм.

- •1.1. Типы зу и их основные характеристики.

- •1.2. Оперативные запоминающие устройства.

- •1.2.1. Общие принципы организации озу.

- •1.2.2. Структурная организация блока памяти.

- •1.2.3. Полупроводниковые интегральные зу с произвольным обращением.

- •1.2.4. Модули памяти и элементы памяти (бис).

- •1.2.5. Система электрических параметров полупроводниковых бис зу.

- •1.2.6. Контроль функционирования бис зу.

- •1.2.7. Организация многоблочной оперативной памяти.

- •1.2.8. Организация озу с многоканальным доступом.

- •1.2.9. Ассоциативные зу.

- •1.3. Сверхоперативные зу.

- •1.3.1. Назначение и типы созу.

- •1.3.2. Организация созу с прямой адресацией.

- •1.3.3. Организация стекового и магазинного созу.

- •1.3.4. Организация ассоциативных созу.

- •1.3.5. Оценка эффективности использования созу в процессоре.

- •1.4. Постоянные зу.

- •1.5. Виртуальная память.

- •Логическое распределение оперативной памяти в персональных компьютерах (Intel/pc).

- •1.6.1. Стандартная оперативная память.

- •1.6.1.1.Таблица векторов прерываний.

- •1.6.1.2. Область данных bios.

- •1.6.1.3. Область для операционной системы.

- •1.6.1.4. Основная область памяти.

- •2. Арифметико-логические устройства эвм

- •2.1. Типы арифметических устройств и их структуры.

- •2.2. Организация алу параллельного действия при работе над числами в естественной форме.

- •2.2.1. Суммирование и вычитание чисел при использовании накапливающего сумматора.

- •2.2.2. Принципы построения алу для сложения и вычитания на комбинационных суммах.

- •2.2.3. Организация алу (параллельного действия) в режиме умножения чисел с фиксированной запятой.

- •2.2.4. Аппаратные способы ускорения умножения в организации алу.

- •2.2.5. Алгоритмические (логические) способы ускорения умножения в организации алу.

- •2.2.6. Организация алу параллельного действия в режиме деления чисел с фиксированной запятой.

- •2.2.7. Организация алу при реализации логических операций и операций специальной арифметики.

- •2.3. Организация алу параллельного действия при работе над числами в нормальной форме.

- •2.3.1. Принцип построения и работы алу при суммировании и вычитании чисел в нормальной форме.

- •2.3.2. Направления и методы ускорения операций над числами с плавающей запятой.

- •2.4. Организация алу, работающих в двоично-десятичных кодах.

- •2.5.Об экзотических формах представления чисел. Логарифмическая форма:

- •Трансформирующаяся запятая.

- •Инверсная запятая.

- •2.6. Итеративные методы деления.

- •3. Процессоры.

- •3.1. Система команд эвм.

- •3.1.1. Структура и форматы команд.

- •3.1.2. Список команд.

- •3.1.3. Способы адресации.

- •3.2. Устройства управления.

- •3.2.1. Организация цуу (на примере гипотетической одноадресной эвм).

- •3.2.2. Принципы формирования уфс.

- •3.2.3. Организация микропрограммных устройств управления.

- •3.3. Организация внутрипроцессорных систем ввода-вывода информации.

- •3.3.1. Основные понятия и определения.

- •3.3.2. Способы обмена данными между ядром малой эвм и периферийными устройствами.

- •3.3.3. Программно управляемые способы передачи данных.

- •3.3.3.1. Простые типы передачи.

- •3.3.3.2. Последовательность событий при прерываниях.

- •3.3.3.3. Идентификация прерывающего устройства.

- •3.3.4. Организация прямого доступа к памяти.

- •4. Основы вычислительных конвейеров.

- •4.1. Введение в архитектурные принципы конвейерных процессоров и эвм.

- •Конвейерные сумматоры

- •Конвейерный умножитель

- •5. Архитектура сигнальных процессоров.

- •5.1. Введение. Основные задачи обработки сигналов. Методы обработки сигналов.

- •5.2. Основные характеристики и базовая архитектура семейства adsp-21xx

- •5.2.1. Общие сведения о составе функциональных устройств

- •5.2.2. Базовая архитектура.

- •5.2.3. Средства разработчиков для процессоров семейства.

- •5.3. Интерфейс процессоров adsp-21xx с памятью.

- •5.3.1. Интерфейс с загрузочной памятью.

- •5.3.2. Интерфейс с памятью программ.

- •5.3.3. Интерфейс с памятью данных.

- •5.4. Архитектура операционных устройств.

- •5.4.1. Арифметико-логическое устройство.

- •5.4.2. Умножитель/накопитель mac.

- •5.4.3. Устройство сдвига shifter.

-

2. Арифметико-логические устройства эвм

-

2.1. Типы арифметических устройств и их структуры.

Как известно, АЛУ совместно с УУ образуют центральное обрабатывающее устройство – основную часть процессора.

АЛУ служит непосредственно для преобразования кодов числовых величин в процессе решения задачи.

В состав операций, реализуемых АЛУ, обычно входят:

арифметические операции (сложение, вычитание, умножение, деление, вычитание модулей и т.п.);

логические (сравнение кодов на равенство, «И», «ИЛИ», «Сложение по модулю 2», именуемое также «Исключающее ИЛИ», и, реже, другие сходные операции над многоразрядными числовыми кодами (поразрядно)); исключительная редкость - использование полей;

операции специальной (машинной) арифметики (сдвиги: циклический, арифметический и логический; нормализация; счет с удвоенной точностью);

операции над кодами как над текстами, строками, символьной информацией;

дополнительные, специальные преобразования числовых кодов.

Последняя группа операций не имеет строго описываемых схожих черт и чётких общих теоретических основ. Кроме того, состав операций АЛУ не определяет полностью перечень операций процессора.

<86>

Условно-схематично введём классификацию АЛУ:

Рис. 2.1.1.

Чуть-чуть комментариев к рисунку:

при параллельном выполнении операций все разряды числа одновременно участвуют в формировании результата (операция может быть выполнена за 1 машинный такт);

существует последовательно-параллельный способ выполнения операций (параллельно над m разрядами из n);

в АЛУ последовательного действия малы затраты оборудования;

использование плавающей запятой требует затрат времени на выравнивание порядков и нормализацию;

эмпирически установлено, что исключительное использование фиксированной запятой требует в 1,5 раза увеличить длину мантиссы.

Эта классификация может быть расширена и дополнена.

<87>

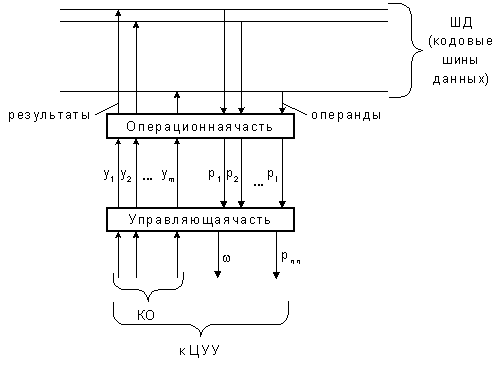

Обобщенную структуру АЛУ, как операционного устройства, и систему его связей с другими устройствами можно представить себе так:

Рис. 2.1.2

В операционную часть (совокупность блоков, предназначенных для хранения слов и выполнения микроопераций над ними) входят: сумматоры, счетчики, регистры, комбинационно- логические схемы и др.

Управляющая часть определяет порядок работы отдельных узлов АЛУ в зависимости от кода операции (КО), поступающего из ЦУУ. Здесь мы его рассматривать не будем (см. раздел УУ). На рисунке:

{yi} – сигналы управления; далее будем их именовать управляющими функциональными сигналами (УФС);

{pj} – осведомительные сигналы;

w – сигнал окончания операции;

рпп – сигнал (признак) переполнения разрядной сетки.

Коды, применяемые в АЛУ, существенно влияют на его структуру, и, следовательно, требуется специальное прямое указание типов применяемых кодов. Если нет специального указания, то далее будем считать, что в ОЗУ при хранении чисел используется дополнительный код.

<88>

-

2.2. Организация алу параллельного действия при работе над числами в естественной форме.

2.2.1. Суммирование и вычитание чисел при использовании накапливающего сумматора.

Будем полагать в этом разделе:

-

хранение чисел в ОЗУ осуществляется в прямом коде;

-

коды модифицированные;

-

в АЛУ при суммировании используется модифицированный обратный код.

Выполняется операция S(A)=S(A)+B:

Рис. 2.2.1.1

Первоначально

подается импульс, УФС сброс

y0.

Затем из регистра слагаемого подается

первое число (по y2),

т.е. считается, что первое число там

всегда хранится заблаговременно. Не

ранее чем через интервал времени

вводится второе число.

вводится второе число.

«Единица» переноса возникает в триггере на выходе «0»: если он перешел из состояния «1» в состояние «0». Линии задержки обеспечивают задержку импульса переноса на время завершения переходных процессов в триггерах (разрядах) при суммировании, что существенно именно при применения накапливающих сумматоров.

Поскольку слагаемые представляются в модифицированных кодах, то знак записывается в два разряда знака (00 или 11). Операции над разрядами знака производятся так же, как и над разрядами значащими. Переполнение (появление комбинаций 01 или 10) проверяется по УФС y3. Цепь циклического переноса служит для организации вычитания за счет суммирования в обратном коде:

.

.

Результат суммирования выдается в прямом коде по сигналу y4.

Если число положительное, то оно выдается непосредственно, а если отрицательное, то оно автоматически (по сигналу y4) инвертируется в прямой код.

Работу схемы легко уяснить по рисунку.

<89>

Несколько слов о времени выполнения операции:

,

,

где

t

– интервал подачи слагаемых,

–

задержка импульсного переноса,

–

задержка импульсного переноса,

–

переходные процессы в триггере сумматора.

Если предположить, что

–

переходные процессы в триггере сумматора.

Если предположить, что

,

то при

,

то при

получаем:

получаем:

.

Столь огромное время выполнения

суммирования связано только с применением

простейшей схемы последовательного

переноса. Современные процессоры в

своём составе используют совсем другие

сумматоры.

.

Столь огромное время выполнения

суммирования связано только с применением

простейшей схемы последовательного

переноса. Современные процессоры в

своём составе используют совсем другие

сумматоры.

Для повышения быстродействия АЛУ применяют различные способы ускорения распространения волны переносов. Отсюда наименования разных типов переносов (схем распространения волны переносов): параллельный, групповой, сквозной. Также применяют асинхронные сумматоры. В последних момент окончания переносов определяется специальной схемой и устанавливается время завершения суммирования для конкретных слагаемых.

В пояснение укажем логические формулы признаков переноса и гарантированного отсутствия переноса в i-ом разряде:

–

сигнал

«перенос из i-го

разряда закончен»

–

сигнал

«перенос из i-го

разряда закончен»

–

признак

окончания переноса.

–

признак

окончания переноса.

Полностью параллельный перенос требует формирования сигналов между разрядами по чрезвычайно громоздким логическим формулам. Их структуру несложно понять по формулам для первых (младших) разрядов:

Легко заметить, что сам принцип формирования формул предполагает наличие эквивалентных сокращённых скобочных форм записи, к которым и сводятся последовательный и групповой виды переносов.

Средний

«пробег» переноса можно оценить как

разрядов. Так получается эмпирически

и теоретически. Тогда, при n=32

имеем:

разрядов. Так получается эмпирически

и теоретически. Тогда, при n=32

имеем:

– для синхронных сумматоров,

– для синхронных сумматоров,

– для асинхронных. Но асинхронные

сложнее по оборудованию.

– для асинхронных. Но асинхронные

сложнее по оборудованию.

<90>