- •Иркутск, 2009 г.

- •Тема 4.5. Основы цифровой электроники

- •По функциональному назначению:

- •По количеству элементов в корпусе имс, т.Е. По степени интеграции:

- •3) По конструктивно-технологическому исполнению:

- •4) По типу базовых электронных ключей, на которых строится имс(по типу логики):

- •5)По способу представления информации:

- •1 Вариант.

- •2 Вариант.

- •Это триггер со счетным входом

- •После выполнения практических заданий каждый студент оформляет отчёт по лабораторной работе с выводами по анализу работы элементов цу.

- •Контрольные вопросы

- •Практическое занятие разработал

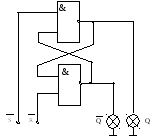

1 Вариант.

Построен на 2-х логических элементах 2ИЛИ-НЕ (элемент Пирса), связанных таким образом, что выход каждого элемента подключен к одному из входов другого

Т аблица

истинности R-S-

триггера

аблица

истинности R-S-

триггера

|

R(t) |

S(t) |

Q(t) |

Q(t=1) |

Режимы |

|

0 0 |

0 0 |

0 1 |

0 1 |

Хранение |

|

0 0 |

1 1 |

0 1 |

1 1 |

Уст.1 |

|

1 1 |

0 0 |

0 1 |

0 0 |

У |

|

1 1 |

1 1 |

0 1 |

-(1/0) -(1/0) |

Запрещен |

У ГО:

ГО:

Логическая формула R-S-триггера:

![]()

![]()

![]()

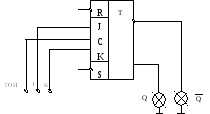

2 Вариант.

Построен на 2-х логических элементах 2И-НЕ (элемент Шефера)

Логическая формула R-S-триггера:

![]()

![]()

![]()

УГО:

S(SET)-установка; R(RESET)-сброс; Q-прямой

выход; Q-инверсный

выход.

![]()

Недостатки:

-слабая помехозащищенность;

наличие запрещенной комбинации.

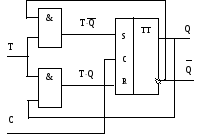

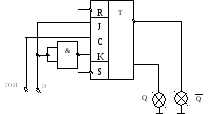

Синхронный однотактный RS-триггер.

УГО:

УГО:

Синхронный RS-триггер состоит из асинхронного RS-триггера и схем И-НЕ, через которые сигнал R и S передается только при наличии 1 на синхронизирующем входе С (С=1). При С=0 состояния выходов триггера не изменяется (режим хранения)

При

с=1

![]()

![]()

При

с=0

![]()

![]()

В

общем виде:

![]()

![]()

Данный триггер изменяет значение выходного сигнала по переднему фронту синхроимпульсов. При этом задержка выходного сигнала относительно входного зависит от времени подачи входного сигнала и находится в диапазоне: 0≤ tз<0,5Т.

Синхронный двухтактный RS-триггер.

0,5Т<tз≤T-время задержки между входным и выходным сигналами.

В 2-хтактном R-S триггере входные сигналы записываются в первый триггер (первая ступень) по переднему фронту синхроимпульса, а изменение выходного (вторая ступень) сигнала –по заднему фронту синхроимпульса.

б) Т-триггер.

Это триггер со счетным входом

Таблица истинности:

-

T(t)

Q(t)

Q(t+1)

Режимы

0

0

0

1

0

1

Хранение

1

1

0

1

1

0

Счета

(инверсии)

Л огическая

функция Q(t+1)

= (T(t)

Q(t) + T(t)

Q(t))

с(t)+

Q(t)c(t)

огическая

функция Q(t+1)

= (T(t)

Q(t) + T(t)

Q(t))

с(t)+

Q(t)c(t)

Синхронный однотактный Т-триггер может быть построен на RS-триггере и элементах “2И”

-

T(t)

Q(t)

S(t)

R(t)

Q(t+1)

Режимы

0

0

0

1

0

0

0

0

0

1

Хранение

1

1

0

1

1

0

0

1

1

0

Счета

(инверсии)

Логическая функция приведенной схемы:

Q(t+1)

= S(t)

+ R(t)

Q(t);

Q(t+1)

= S(t)

+ R(t)

Q(t);

S (t)

= T(t)

Q(t); R(t) = T(t)

Q(t)

(t)

= T(t)

Q(t); R(t) = T(t)

Q(t)

Объединим все эти логические функции:

Q(t+1)

= T(t)

Q(t) + T(t)

Q(t)

Q(t) =

Q(t+1)

= T(t)

Q(t) + T(t)

Q(t)

Q(t) =

= T(t)

Q(t) + (T(t) + Q(t))

Q(t) =

= T(t)

Q(t) + (T(t) + Q(t))

Q(t) =

=

T(t)

Q(t) + T(t)

Q(t) + Q(t)

Q(t) =

=

T(t)

Q(t) + T(t)

Q(t) + Q(t)

Q(t) =

=

T(t)

Q(t) + T(t)

Q(t).

=

T(t)

Q(t) + T(t)

Q(t).

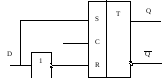

в) Д – триггер.

Выполняет функцию временной задержки входного сигнала. Имеет только один информационный вход. Вход С управляющий, и служит для подачи синхроимпульсов:

Q (t+1)

= D(t)

(t+1)

= D(t)

Q (t+1)

= C(t)

Q(t) +

(t+1)

= C(t)

Q(t) +

+ C(t)

(S(t) +R(t)

Q(t)

C(t)

(S(t) +R(t)

Q(t)

т .к.

S(t) = D(t); R(t) = D(t)

.к.

S(t) = D(t); R(t) = D(t)

получим:

Q

(t+1)

= C(t)

Q(t) + C(t)

(D(t) + D(t) + D(t)

Q(t) = C(t)Q(t) + C(t)

D(t)

(t+1)

= C(t)

Q(t) + C(t)

(D(t) + D(t) + D(t)

Q(t) = C(t)Q(t) + C(t)

D(t)

C(t) = 0 Q(t+1) = Q(t)

C(t) = 1 Q(t+1) = D(t)

D

И3 – триггера бывают только синхронные

– триггера бывают только синхронные

Двухступенчатый D – триггер.

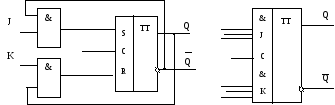

г) JK – триггер.

Универсальный триггер отличается от RS триггера отсутствием запрещенной комбинации на входах J и K.

Таблица истинности: (J – JUМP; K – KEEP)

-

J(t)

K(t)

Q(t)

Q(t+1)

Режимное

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

0

1

1

1

0

Х

ранение

ранениеУ

ст.”0”

ст.”0”У

ст.”1”

ст.”1”И

нверсный

нверсный(счет)

J -входное

устройство “1”; К- входное устройство

“0”; известно, что логическая формула

для RS-триггера имеет

вид:Q(t+1)=S(t)+R(t)Q(t)

(*),

-входное

устройство “1”; К- входное устройство

“0”; известно, что логическая формула

для RS-триггера имеет

вид:Q(t+1)=S(t)+R(t)Q(t)

(*),

Используя схему JК триггера (рис.1) (R-S триггер 2 схема “2И” на входе)

М

ожно

записать S(t)=

J(t)

Q(t); R(t)=

K(t)

Q(t), подставив

S(t) и R(t)

в выражение (*) получим:

ожно

записать S(t)=

J(t)

Q(t); R(t)=

K(t)

Q(t), подставив

S(t) и R(t)

в выражение (*) получим:

Q

(t+1)

= K(t)

Q(t)

Q(t)

+ J(t)

Q(t)=

(t+1)

= K(t)

Q(t)

Q(t)

+ J(t)

Q(t)=

=

J(t)

Q(t)+(K(t)

+ Q(t))

Q(t)

=

J(t)

Q(t)+(K(t)

+ Q(t))

Q(t)

=

J(t)

Q(t)+K(t)

Q(t)+

Q(t)

Q(t)

=

J(t)

Q(t)+K(t)

Q(t)+

Q(t)

Q(t)

=

=

J(t)

Q(t)+

K(t)

Q(t). (закон

противоречия)

J(t)

Q(t)+

K(t)

Q(t). (закон

противоречия)

Логическая функция JK триггера имеет вид:

Q(t+1)

= K(t)

Q(t) + J(t)

Q(t)

Q(t+1)

= K(t)

Q(t) + J(t)

Q(t)

На JK – триггере легко реализовать другие типы триггеров ( RS, D, T…):

J TT Q D J TT Q R R K C J TT Q Q S T

R C Q R C Q R

R K 1 R K

RS – тр. D – тр. T – тр.

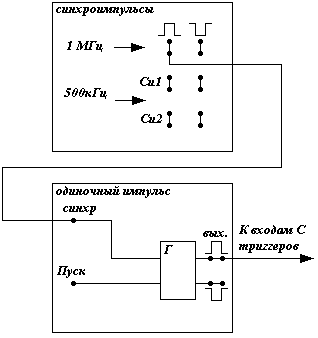

ПЗ.4.5.1.5. Анализ комбинационных схем и цифровых автоматов.

А) Порядок работы

1. После изучения указанного выше материала и подготовки отчета по ПЗ на самостоятельной подготовке, учебная группа разбивается на бригады и выполняет по бригадам практические задания, используя при этом лабораторную установку.

Задания:

1.Изучить лабораторную установку (размещение логических элементов, триггеров, элементов управления; меры безопасности при работе).

2.Собрать схемы и проанализировать работу логических элементов: 2И-НЕ, НЕ, 2И, 2ИЛИ-НЕ, 2ИЛИ.

3. Собрать схемы и проанализировать работу триггеров: асинхронного RS-триггера (на элементах 2И-НЕ), синхронного однотактного RS-триггера., JK-триггера, D-триггера, Т-триггера,

4. Ознакомиться с условными графическими обозначениями (УГО) логических элементов и триггеров.

2. По методическим разработкам (имеются у каждой бригады) проводится анализ работы логических элементов, триггеров. Результаты анализа заносятся в соответствующие таблицы отчёта. Анализ работы проводить в следующей последовательности:

- подобрать необходимые элементы и проводники;

- собрать схему исследуемого элемента;

- провести исследование путём задания входных сигналов логического элемента или триггера с тумблерных переключателей (с верхней клеммы переключателя при установке рычага переключателя в верхнее положение будет сниматься сигнал логической "1", иначе логического "О"). Выходной сигнал снимается с сигнальных ламп (если горит лампа- логическая "1", иначе логический "0").

При сборке элементов ЦУ необходимо знать следующие две особенности работы логических элементов установки:

- Наличие незадействованного входа в логических элементах типа И-НЕ равносильно подаче на этот вход "1". Число незадействованных входов в таких элементах не должно превышать двух. В противном случае на незадействованные входы логических элементов необходимо подавать "1".

Внимание! СБОРКА узлов ЦУ на наборном поле лабораторной установки производится при отключенной установке. Включение установки и исследование узлов производится после проверки схемы инженером лаборатории или преподавателем

СХЕМЫ АНАЛИЗИРУЕМЫХ ЦИФРОВЫХ ЭЛЕМЕНТОВ

Рис.1 Логический элемент 2И-НЕ Рис.2 Логический элемент НЕ

(на элементе 2И-НЕ)

Рис.3 Логический элемент 2И (на элементе 2И-НЕ)

Рис.4 Логический элемент 2ИЛИ (на элементах 2И-НЕ)

Рис.5 Логический элемент 2ИЛИ-НЕ (на элементах 2И-НЕ)

Рис. 6 Схема сборки генератора одиночных импульсов (ГОИ)

Рис.7 Асинхронный RS-триггер (на элементах 2И-НЕ)

Рис.8 Синхронный однотактный RS-триггер(на элементе 2И-НЕ)

Рис.9 JK- триггер

Рис.10 RS- триггер (на JK- триггере)

Рис.11 T- триггер (на JK- триггере)

Рис.12 D-триггер (на JK- триггере)

ТАБЛИЦЫ РЕЗУЛЬТАТОВ АНАЛИЗА ЦИФРОВЫХ ЭЛЕМЕНТОВ

Логические элементы 2И-НЕ, 2И, 2ИЛИ-НЕ, 2ИЛИ

Таблица1

|

Х1 |

X2 |

Y2и-не(рис1) |

Y2и(рис3) |

Y2или-не(рис5) |

Y2или(рис4) |

|

0 |

0 |

|

|

|

|

|

0 |

1 |

|

|

|

|

|

1 |

0 |

|

|

|

|

|

1 |

1 |

|

|

|

|

Логический элемент НЕ

Таблица 2

|

X |

Yне(рис2) |

|

0 |

|

|

1 |

|

RS-триггер (на элементах 2И-НЕ)

Таблица 3

|

R |

S |

Q(t) |

Q(t+1)(рис7) |

|

0 |

0 |

0 |

|

|

0 |

0 |

1 |

|

|

0 |

1 |

0 |

|

|

0 |

1 |

1 |

|

|

1 |

0 |

0 |

|

|

1 |

0 |

1 |

|

|

1 |

1 |

0 |

|

|

1 |

1 |

1 |

|

RS-триггер

Таблица 6

|

R(t) |

S(t) |

Q(t) |

Q(t+1)(рис7) |

Q(t+1)(рис8) при С=1 |

Q(t+1)(рис10) при С=1 |

|

0 |

0 |

0 |

|

|

|

|

0 |

0 |

1 |

|

|

|

|

0 |

1 |

0 |

|

|

|

|

0 |

1 |

1 |

|

|

|

|

1 |

0 |

0 |

|

|

|

|

1 |

0 |

1 |

|

|

|

|

1 |

1 |

0 |

|

|

|

|

1 |

1 |

1 |

|

|

|

JK-триггер

Таблица 7

|

J(t) |

K(t) |

Q(t) |

Q(t+1)(рис9) при С=0 |

Q(t+1)(рис9) при С=1 |

|

0 |

0 |

0 |

|

|

|

0 |

0 |

1 |

|

|

|

0 |

1 |

0 |

|

|

|

0 |

1 |

1 |

|

|

|

1 |

0 |

0 |

|

|

|

1 |

0 |

1 |

|

|

|

1 |

1 |

0 |

|

|

|

1 |

1 |

1 |

|

|

Т-триггер

Таблица 8

|

Т(t) |

Q(t) |

Q(t+1)(рис11) при С=0 |

Q(t+1)(рис11) при С=1 |

|

0 |

0 |

|

|

|

0 |

1 |

|

|

|

1 |

0 |

|

|

|

1 |

1 |

|

|

D-триггер

Таблица 9

|

D(t) |

Q(t) |

Q(t+1)(рис12) при С=0 |

Q(t+1)(рис12) при С=1 |

|

0 |

0 |

|

|

|

0 |

1 |

|

|

|

1 |

0 |

|

|

|

1 |

1 |

|

|

ст.0

ст.0 (t)

(t) (t)

(t)