- •Разработка программной и аппаратной поддержки к методическим указаниям «программирование микроконтроллеров»

- •Реферат

- •Введение

- •1. Основы архитектуры микроконтроллеров

- •1.1. Основные типы микроконтроллеров и их архитектура

- •Система команд.

- •Типы памяти мк.

- •1.2. Аппаратные средства

- •1.2.1. Запуск микроконтроллера

- •Сброс в начальное состояние.

- •1.2.2. Тактирование и командные циклы

- •1.2.3. Программный счетчик и алу

- •1.2.4. Подпрограммы и функции

- •Прерывания.

- •Таймеры.

- •1.2.5. Ввод/вывод данных

- •Аналоговый компаратор.

- •Программирование устройств.

- •Безопасность памяти программ.

- •1.3. Инструментальные и программные средства разработки и отладки

- •Симуляторы

- •000000000:00

- •Интегрированные среды разработки

- •Язык Ассемблера.

- •Языки программирования высокого уровня.

- •1.4. Основные типы интерфейсов мк.

- •1.4.1. Подключение переключателей и подавление «звона» контактов.

- •1.4.2. Световая индикация.

- •Семи сегментный индикатор.

- •1.4.3. Ввод с матричной клавиатуры.

- •2. Особенности построения и функционирования микроконтроллеров фирмы atmel семейства avr

- •2.1. Архитектура микропроцессорного ядра avr-микроконтроллеров

- •Программная модель avr и система команд.

- •Адресация регистров ввода/вывода и памяти sram.

- •Программный счетчик и стек

- •Регистр состояния.

- •Прерывания.

- •2.2. Аппаратные средства avr. Системный тактовый генератор.

- •Таймеры.

- •Сторожевой таймер.

- •Устройство внешнего вывода.

- •Аналоговый ввод/вывод.

- •Конфигурирование мк

- •Память данных eeprom.

- •Подключение питания и запуск.

- •Программирование в системе.

- •2.3. Система команд микроконтроллера avr

- •Способы адресации данных

- •Команды пересылки данных.

- •Команды арифметических и логических операций.

- •Команды ветвления

- •Битовые команды и команды тестирования битов.

- •3. Программное и инструментальное обеспечение процесса программирования микроконтроллеров

- •3.1. Написание и отладка программного кода с помощью avr Studio

- •3.1.1. Обзор avr Studio

- •3.1.2. Создание нового проекта

- •3.1.3. Исполнение программного кода

- •3.2. Анализ методики реализации разработки программного обеспечения

- •3.2.1. Классификация вариантов заданий

- •Варианты заданий

- •Основные принципы выполнения заданий.

- •3.2.2. Рассмотрение типовых примеров

- •3.3. Описание макета программатора.

- •Заключение

- •Библиографический список использованных источников

- •Приложение 1Инструкции процессоров avr.

- •Приложение 2. Таблица регистров микроконтроллера at90s1200

- •Приложение 3. Программа для измерителя звуковой частоты

- •Приложение 4. Программа для устройства «кодовый замок»

- •Приложение 5. Основные характеристики микроконтроллеров avr

1.4.3. Ввод с матричной клавиатуры.

Во многих приложениях требуется производить ввод данных с клавиатуры. Это может быть реализовано при помощи отдельных кнопок, но такой подход слишком расточителен с точки зрения использования линий ввода/вывода МК. Лучшим решением является использование матричной клавиатуры, которая представляет собой набор ключей, объединенных в ряды и столбцы (см. рис. 1.11).

Рис. 1.11. Подключение к МК матричной клавиатуры.

Для чтения состояния определенного ключа на столбец подается сигнал, а затем считывается состояние рядов. Обычно ряды подключаются к высокому потенциалу, а опрашиваемый столбец соединяется с землей. Если при сканировании считывается низкий уровень сигнала, то это означает, что ключ в данной позиции ряд-столбец замкнут. На рис. 1.11 показаны два МОП-транзистора, которые используются для подключения столбцов к земле. Но в некоторых МК выводы могут работать в режиме с открытым коллектором, и следовательно имитировать работу этих транзисторов, делая их включение ненужным.

Матричная клавиатура может быть расширена практически до любого размера, используя при этом небольшое число выводов МК. Например, 104-клавишная клавиатура ПК – это матрица, содержащая 13х8 ключей.

2. Особенности построения и функционирования микроконтроллеров фирмы atmel семейства avr

2.1. Архитектура микропроцессорного ядра avr-микроконтроллеров

Архитектура AVR была оптимизирована так, чтобы соединить достоинства Гарвардской и Принстонской (Фон Неймана) архитектуры для достижения очень быстрого и эффективного выполнения программ. Такая организация обеспечивает высокую эффективность процессора при обработке данных.

Основной идеей всех RISC (Reduced Instruction Set Computer), как известно, является увеличение быстродействия за счет сокращения количества операций обмена с памятью программ. Для этого каждую команду стремятся уместить в одну ячейку памяти программ. При ограниченной разрядности ячейки памяти это неизбежно приводит к сокращению набора команд микропроцессора.

У AVR-микроконтроллеров в соответствии с этим принципом практически все команды (исключая те, у которых одним из операндов является 16-разрядный адрес) также упакованы в одну ячейку памяти программ. Но сделать это удалось не за счет сокращения количества команд процессора, а путем расширения ячейки памяти программ до 16 разрядов. Такое решение является причиной богатства системы команд AVR по сравнению с другими RISC-микроконтроллерами.

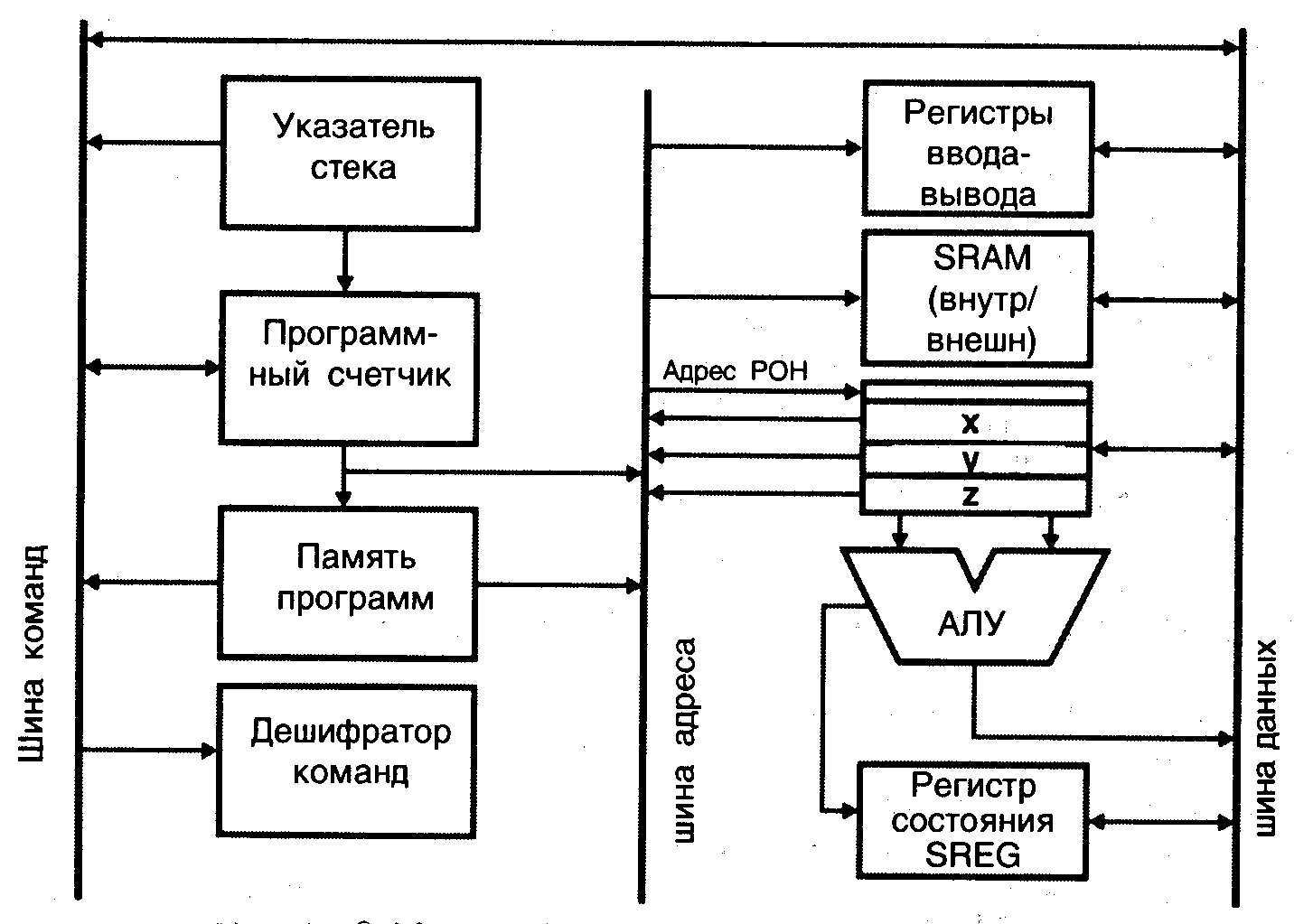

Организация памяти AVR выполнена по схеме Гарвардского типа, в которой разделены не только адресные пространства памяти программ и памяти данных, но также и шины доступа к ним. Для более углубленного понимания архитектуры приведем две схемы (см. рис. 2.1 и 2.2).

Вся программная память AVR-микроконтроллеров выполнена по технологии FLASH и размещена на кристалле. Она представляет собой последовательность 16-разрядных ячеек и имеет емкость от 512 слов до 64K слов в зависимости от типа кристалла.

Разделение шин доступа (рис. 2.2.) к FLASH памяти и SRAM памяти дает возможность иметь шины данных для памяти данных и памяти программ различной разрядности, а также использовать технологию конвейеризации. Конвейеризация заключается в том, что во время исполнения текущей команды программный код следующей уже выбирается из памяти и дешифрируется.

Рис. 2.1. Архитектура AVR-микроконтроллеров.

Рис. 2.2. Структурная схема архитектуры процессора семейства AVR.

Для сравнения вспомним, что у микроконтроллеров семейства MCS-51 выборка кода команды и ее исполнение осуществляются последовательно, что занимает один машинный цикл, который длится 12 периодов кварцевого резонатора.

В случае использования конвейера приведенную длительность машинного цикла можно сократить. Например, у PIC-микроконтроллеров фирмы Microchip за счет использования конвейера удалось уменьшить длительность машинного цикла до 4 периодов кварцевого резонатора. Длительность же машинного цикла AVR составляет один период кварцевого резонатора. Таким образом, AVR способны обеспечить заданную производительность при более низкой тактовой частоте. Именно эта особенность архитектуры и позволяет AVR-микроконтроллерам иметь наилучшее соотношение энергопотребление/производительность, так как потребление КМОП микросхем, как известно, определяется их рабочей частотой [9,11].