- •Введение

- •Расшифровка и анализ задания

- •2.2 Генератор тактовых импульсов

- •2.3 Буферный регистр кр580ир82

- •2.4 Шинный формирователь кр580ва86

- •2.5 Контроллер шин к1810вг88

- •2.6 Арбитр шин к1810вб89

- •2.8 Программируемый таймер кр580ви53

- •3.3 Подключение устройств памяти и ввода-вывода к магистралям

- •4.3 Разработка контроллера прямого доступа к памяти

- •4.4 Расширенная структурная схема микропроцессорной системы

- •5 Разработка алгоритма работы микропроцессорной

- •6 Реализация ес1834 – ппэвм комбината "Роботрон" на

- •Заключение

- •Список используемых источников

- •68 Изм. Лист № Докум. Подпись Дата Уитс.161ххх.122 пз Лист.

4.3 Разработка контроллера прямого доступа к памяти

Режим прямого доступа к памяти (ПДП) инициируется подачей на вход HLD МП БИС К1810ВМ86 единичного сигнала запроса. По завершении текущего машинного цикла МП БИС выдает сигнал подтверждения захвата и переводит свои магистрали в третье состояние. Так как память МП БИС организована в виде однобайтных ячеек, то для осуществления режима прямого доступа к памяти может использоваться микросхема КР580ВТ57, относящаяся к МПК серии К580.

БИС программируемого контроллера прямого доступа к памяти КР580ВТ57 предназначена для организации высокоскоростного обмена данными между памятью и внешними устройствами, выполняемого по инициативе внешнего устройства. Контроллер прямого доступа к памяти (КПДП)

генерирует управляющие сигналы, необходимые для организации обмена. КПДП содержит 4 канала прямого доступа, каждый из которых обеспечивает передачу блока данных размером до 16К байт с произвольным начальным адресом в диапазоне от 0 до 64 байт.

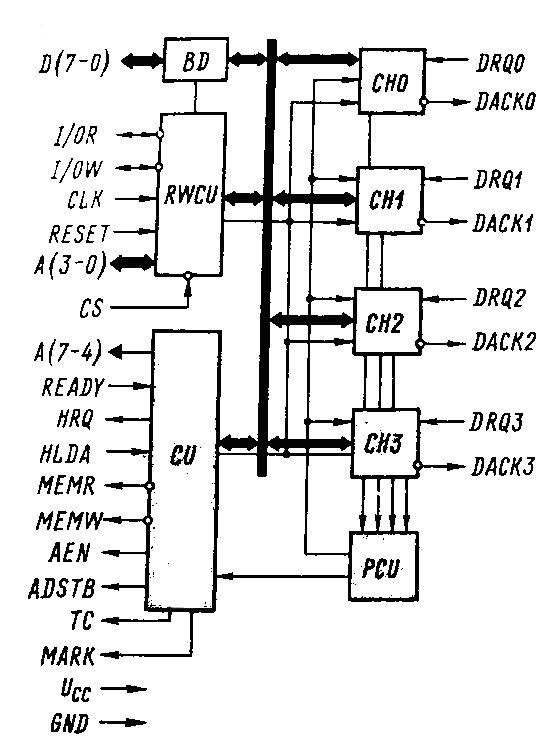

В состав БИС входят: двунаправленный двустабнльный буфер данных (ВD), предназначенный для обмена информацией между МП и КПДП: схема управления чтением/записью (RWCU), адресующая внутренние регистры КПДП и управляющая обменом по шине D(7-0); блок управления (CU), содержащий регистры режима и состояния КПДП и обеспечивающий последовательность операций, необходимую для организации режима прямого доступа к памяти; блок управления приоритетами (PCU), обеспечивающий определенный порядок обслуживания запросов внешних устройств; четыре канала прямого доступа (CH0-CH3), каждый из которых содержит регистр адреса ячейки памяти, с которой производится обмен, и счетчик циклов обмена, два старших разряда которого отведены для задания операций обмена.

Структура КПДП КР580ВТ57 приведена на рисунке 29, а назначение входных, выходных и управляющих сигналов – в таблице 12.

Рисунок 29 – Структура КПДП КР580ВТ57

Таблица 11 – Назначение входных, выходных и управляющих сигналов

КПДП

|

Обозначение вывода |

Номер вывода |

Назначение выводов |

|

1 |

2 |

3 |

|

D(7-0)

|

21; 22; 23; 26; 27; 28; 29; 30; |

Входы/выходы данных для обмена с МП;

|

|

I/OR

|

1

|

Чтение ввода/вывода – двунаправленный тристабильный вход/выход: входной сигнал L-уровня разрешает чтение информации из КПДП в МП; выходной сигнал L-уровня разрешает чтение из ВУ;

|

|

1 |

2 |

3 |

|

I/OW

|

2

|

Запись ввода/вывода – двунаправленный тристабильный вход/выход; входной сигнал L-уровня разрешает программирование КПДП: выходной сигнал L-уровня разрешает запись в ВУ; |

|

CLK |

12 |

Вход тактовых импульсов; |

|

RESET |

13 |

Вход установки 0; |

|

A(3-0) |

35; 34; 33; 32 |

Двунаправленные тристабильные адресные выводы; |

|

CS |

11 |

Выбор микросхемы; |

|

A(7-4) |

40; 39; 38; 37; |

Тристабильные адресные выходы; |

|

READY

|

6

|

Готовность – входной сигнал H-уровня указывает на готовность к обмену; |

|

HRQ

|

10

|

Запрос захвата – выходной сигнал H-уровня указывает на запрос о доступе КПДП к системным шинам; |

|

HLDA |

7 |

Подтверждение захвата – входной сигнал H-уровня указывает на возможность доступа к системным шинам; |

|

MEMR

|

3

|

Чтение из памяти – тристабильный выход; выходной сигнал L-уровня разрешает чтение из ячейки памяти, адресуемой КПДП; |

|

MEMW

|

4

|

Запись в память – тристабильный выход; выходной сигнал L-уровня разрешает запись в ячейку, адресуемую КПДП; |

|

AEN |

9 |

Разрешение адреса – сигнал H-уровня используется для блокировки некоторых шин адреса и данных; |

|

ADSB

|

8

|

Строб адреса – сигнал H-уровня указывает на нахождение на шине D(7–0) старшего байта адреса ЗУ; |

|

TC

|

36

|

Конец счета – сигнал H-уровня определяет выполнение последнего цикла передачи блока данных; |

|

MARK

|

5

|

Маркер – сигнал H-уровня указывает, что до конца передаваемого блока необходимо выполнить число циклов обмен-кратное 128; |

|

DRQ3-DRQ0

|

16; 17; 18; 19

|

Запросы прямого доступа к памяти каналов СНЗ-СН0 сигнал H-уровня указывает на запрос от ВУ; |

продолжение таблицы 11

|

1 |

2 |

3 |

|

DACK3-DACK0

|

15; 14; 24; 25

|

Подтверждение запросов прямого доступа к памяти каналов СН3-СН0; сигнал L-уровня указывает на разрешение обмена; |

|

Ucc |

31 |

Напряжение питания (+5 В); |

|

GND |

20 |

» » (0 В). |

При подключении КПДП к шинам микроЭВМ младший байт адреса памяти выдается по линиям А(3–0) и А(7–4), а старший байт – через шину D(7–0), поэтому КПДП обычно подключается вместе с буферным регистром.

Для начальной установки КПДП необходимо записать соответствующую информацию в 16-разрядный регистр адреса канала (RGA), в 16-разрядный счетчик циклов канала (СТ) и в 8-разрядный регистр режима, общий для всех каналов. Два старших разряда счетчика циклов определяют операцию обмена следующим образом: запись в память – 01, чтение из памяти – 10, контроль – 00 (комбинация 11 запрещена).

Рисунок 30 – Схема подключения КПДП к системной шине

Состояние КПДП можно контролировать чтением содержимого КПФ, СТ и 8-разрядного регистра состояния, общего для всех каналов, с помощью команды IN.