К541ре1 к555ли1 к555лн1

Рисунок 20 - Схема подключения ОЗУ и ПЗУ к магистралям

4. РАЗРАБОТКА ПОДСИСТЕМ ВВОДА/ВЫВОДА, ПРЕРЫВАНИЯ И

ПРЯМОГО ДОСТУПА К ПАМЯТИ

4.1 Контроллер прямого доступа к памяти КР580ВТ57

БИС программируемого контроллера прямого доступа к памяти КР580ВТ57 предназначена для организации высокоскоростного обмена данными между памятью и внешними устройствами, выполняемого по инициативе внешнего устройства. Контроллер прямого доступа к памяти (КПДП) генерирует управляющие сигналы, необходимые для организации обмена. КПДП содержит четыре канала прямого доступа, каждый из которых обеспечивает передачу блока данных размером до 16 Кбайт с произвольным начальным адресом в диапазоне от 0 до 64 Кбайт.

Упрощенная структурная схема контроллера прямого доступа к памяти приведена ниже.

В состав БИС входят: двунаправленный двустабильный буфер данных ВD, предназначенный для обмена информацией между микропроцессором и контроллером прямого доступа к памяти; схема управления чтением/записью RWCU, адресующая внутренние регистры КПДП и управляющая обменом по шине D (7-0); блок управления СU, содержащий регистры режима и состояния КПДП и обеспечивающий последовательность операций, необходимую для организации режима прямого доступа к памяти; блок управления приоритетами РСU, обеспечивающий определенный порядок обслуживания запросов внешних устройств; четыре канала прямого доступа СН0 - СН3, каждый из которых содержит регистр адреса ячейки памяти, с которой производится обмен, и счетчик циклов обмена, два старших разряда которого отведены для задания операций обмена.

При подключении КПДП к шинам микро ЭВМ младший байт адреса выдается по линиям А (3-0) и А (7-4), а старший байт через шину D (7-0), поэтому КПДП обычно подключается вместе с буферным регистром.

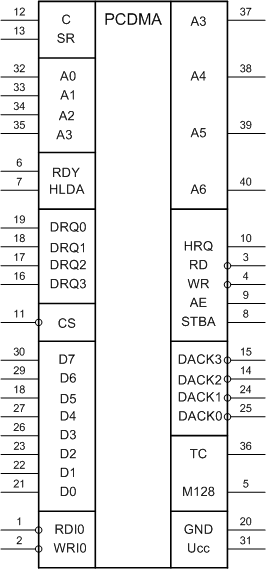

Рисунок 21 - Условное графическое обозначение КР580ВТ57

Режим расширенной записи EW=1 увеличивает за счет смещения переднего фронта длительность сигналов I/OW и MEMW, генерируемых КПДП. Это позволяет ВУ, формирующему сигнал READY по фронту сигнала записи, уменьшить время охлаждения и увеличить скорость обмена.

В режиме автозагрузки AL=1 может работать только второй канал, использую содержимое своих внутренних регистров и внутренних регистров третьего канала.

BD

CH0

CH1

CH2

CH3

PCU

DRQ0

DACK0

DRQ1

DACK1

DRQ2

DACK2

DRQ3

DACK3

RWCU

CU

D (7-0)

I/0R

I/OW

CLK

RESET

A (3-0)

CS

A (7-4)

READY

HRQ

HLDA

MEMR

MEMW

AEN

ADSTB

TC

MARK

UCC

GND

Рисунок 22 – Структурная схема контроллера прямого доступа к памяти

КР580ВТ57

Таблица 12 – Назначение выводов КПДП

|

№ вывода |

Обозначение

|

Наименование |

Назначение |

Тип сигнала |

Состояние | |

|

Англ. |

Рус. | |||||

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

21;22; 23;26; 27;28; 29;30 |

D(7-0) |

Д0 - Д7 |

Шина данных |

Входы/выходы данных для обмена с МП |

вх/вых |

1,0,в.с. |

|

1 |

I/OR |

ЧТ.В. |

Чтение вво |

Разрешает чтение информации из |

вход |

0 |

Продолжение таблицы 12

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

|

|

|

да/вывода |

КПДП в МП; выходной сигнал L-уровня разрешает чтение из ВУ |

|

|

|

2 |

I/OW |

ЗП.В. |

Запись ввода/вывода |

Разрешает программирование КПДП; выходной сигнал L-уровня разрешает запись в ВУ |

вход |

0 |

|

35;34;33;32 |

A(3-0) |

A(3-0) |

Шина адреса |

Двунаправленные тристабильные адресные выводы |

вх/вых |

1,0,в.с |

|

11 |

CS |

ВК |

Выбор кристалла |

Выбор микросхемы |

вход |

0 |

|

40;39;38;37 |

A(7-4) |

A(7-4) |

Шина адреса |

Тристабильные адресные выходы |

выход |

1,0,в.с |

|

6 |

READY |

ГОТ |

Готовность |

Готовность — входной сигнал Н-уровня указывает на готовность к обмену |

вход |

1 |

|

10 |

HRQ |

З.ЗХ. |

Запрос захвата |

Запрос захвата — выходной сигнал Н-уровня указывает на запрос о доступе КПДП к системным шинам |

выход |

1 |

|

7 |

HLDA |

П.ЗХ. |

Подтверждение захвата |

Подтверждение захвата — входной сигнал Н-уровня указывает на возможность доступа к системным шинам |

вход |

1 |

|

3 |

MEMR |

ЧТ.П. |

Чтение из памяти |

Разрешает чтение из ячейки памяти, адресуемой КПДП |

выход |

0 |

|

4 |

MEMW |

ЗП.П |

Запись в память |

Разрешает запись в ячейку, адресуемую КПДП |

выход |

0 |

|

9 |

AEN |

РА |

Разрешение адреса |

Используется для блокировки некоторых шин адреса и данных |

выход |

1 |

|

8 |

ADSTB |

СТБА |

Строб адреса |

Сигнал Н-уровня указывает на нахождение на шине |

выход |

1 |

Продолжение таблицы 12

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

|

|

|

|

D(7—0) старшего байта адреса ЗУ |

|

|

|

36 |

TC |

КБ |

Конец счета |

Определяет выполнение последнего цикла передачи блока данных |

выход |

1 |

|

5 |

MARK |

МАРК |

Маркер |

Указывает, что до конца передаваемого блока необходимо выполнить число циклов обмена, кратное 128 |

выход |

1 |

|

16;17;18;19 |

DRQ3-DRQ0 |

ЗПДП3-ЗПДП0 |

Запросы прямого доступа к памяти |

Запросы прямого доступа к памяти каналов СН3-СН0; сигнал Н-уровня указывает на запрос от ВУ |

вход |

1 |

|

12 |

CLK |

ВХ |

Импульс синхронизации |

Вход тактовых импульсов |

вход |

1 |

|

13 |

RESET |

СБР |

Сброс |

Вход установки 0 |

вход |

1 |

|

15;14;24;25 |

DACK3-DACK0 |

ППДП3-ППДП0 |

Подтверждение запросов ПДП |

Сигнал L-уровня указывает на разрешение обмена |

выход |

1 |

|

31 |

UСС |

UИП |

Сигнал питания |

Напряжение питания ( + 5 В) |

- |

- |

|

20 |

GND |

ОБЩ |

Сигнал питания |

Напряжение питания (0 В) |

- |

- |

Электрические параметры микросхемы КР580ВТ57 при температуре окружающей среды 25±10°С:

- выходное напряжение логического нуля UOL, В менее 0,45;

- выходное напряжение логической единицы UOH, В более 2,4;

- ток потребления IСС, мА менее 100;

- ток утечки на входах IIL, мкА менее 1,5;

- ток утечки на управляемых выводах IОL, мкА 1,5.

Схема подключения контроллера прямого доступа к памяти к системной шине с использованием буферного регистра К589ИР12 показана на рисунке 22.

КР580ВТ57

AB

CB

DB

A (3-0)

A (7-4)

A (8-15)

CS

A (3-0)

A (7-0)

К589ИР12

I/0R

I/0W

MEMR

MEMRW

HOLD

HLDA

CLK2

READY

RESET

ADSTB

AEN

D (7-0)

I/0R

I/0W

MEMR

MEMRW

HLDA

HRQ

READY

RESET

CLK

ТC

MARK

DACK3

DRQ3

DACK2

DRQ2

DACK1

DRQ1

DACK0

DRQ0

Рисунок 23 – Схема подключения контроллера прямого доступа к памяти к системной шине с использованием буферного регистра К589ИР12

4.2 Программируемый контроллер прерываний К1810ВН59А

Микропроцессорная БИС имеет простую и изменяющуюся систему прерываний. Прерывания могут быть вызваны внешними устройствами, выполнением соответствующих команд, а также инициированы самой МП БИС (внутренние прерывания). Существует 256 различных типов прерываний.

Рисунок 24 - Условное графическое обозначение К1810ВН59А

Для подачи прерываний в МП БИС имеются два входа:

INTR – Interrupt Reguest и NMI – Non Masking Interrupt (рисунок 23).

Рисунок 25 – Возможные способы формирования прерываний в

МП К1810ВМ6

Таблица 13 – Назначение выводов ПКП КР580ВН59А

|

№ вывода |

Обозначение |

Наименование |

Назначение |

Тип сигнала |

Состояние | |

|

Англ. |

Рус. | |||||

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

1 |

CS |

ВК |

Выбор кристалла |

Вход выбора микросхемы |

вход |

0 |

|

2 |

WR |

ЗП |

Запись |

Вход строба записи |

вход |

0 |

|

3 |

RD |

ЧТ |

Чтение |

Вход строба чтения |

вход |

0 |

|

4;5;6;7;8;9; 10; 11 |

D(7-0) |

Д0 - Д7 |

Шина данных |

Вход/выход данных |

вх/вых |

1,0,в.с. |

|

18;19; 20;21 22;23; 24;25 |

IR0-IR7 |

ЗПР0-ЗПР7 |

Запросы прерываний |

Входы запросов прерываний |

вход |

1 |

|

12; 13; 15 |

CAS0-CAS2 |

КАС0–КАС2 |

Каскадирование |

Входы/выходы каскадирования |

вх/вых |

1 |

|

14 |

GND |

ОБЩ |

Сигнал питания |

напряжение питания 0 В |

- |

- |

|

16 |

SP |

ВДМ |

Ведомый контроллер |

Признак подчинения: напряжение H-уровня указывает, что ПКП является старшим (ведущим) контроллером; напряжение L-уровня определяет ПКП подчиненным (ведомым) контроллером |

вход |

0 |

|

17 |

INT |

ПР. |

Прерывание |

Прерывание — напряжение H-уровня указывает о запросе на обслуживание прерывания |

вход |

1 |

|

26 |

INTA |

П.ПР. |

Подтверждение прерывания |

Подтверждение прерывания — входное напряжение H-уровня указывает о выдаче ПКП команды CALL на шину данных |

выход |

0 |

Продолжение таблицы 13

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

27 |

А0 |

А0 |

Разряд адреса |

Вход нулевого разряда адреса, используемый при загрузке команд и считывании состояния ПКП |

вход |

1 |

|

28 |

UCC |

UИП |

Сигнал питания |

напряжение питания +5 В |

- |

- |

Вход INT обычно используется для подключения программируемого блока приоритетных прерываний (БПП). По функциональному назначению микросхема БПП аналогична схеме КР580ИК59 и является дальнейшей ее модификацией. Режимы работы БПП могут быть заданы программно. Основные задачи БПП – получение запросов прерывания от различных внешних устройств, определение сигнала с высшим приоритетом, формирование запроса прерывания на входе МП БИС и сообщение номера текущего обслуживаемого внешнего устройства. Прерывания по входу INT могут быть маскированы путем записи «0» или «1» в разряд 1 флагового регистра МП БИС.

Микропроцессорная БИС реагирует на поступление запроса прерывания по входу INTR последовательным выполнением двух машинных циклов обслуживания прерывания: первый указывает БПП, что запрос прерывания был воспринят, и начинает обслуживаться; на втором БПП выдает на МД байт данных, указывающий тип прерывания (0–255). При работе МП БИС с максимальной конфигурацией системы на интервале двух циклов INTA на выходе LOCK формируется сигнал, запрещающий другим процессорам системы пользоваться магистралями.

Внешние устройства могут подавать запросы прерывания на второй вход NMI МП БИС. На этом входе запрос воспринимается и записывается в МП БИС по фронту поступающего импульса, не может быть маскирован и имеет высший приоритет по отношению к запросам, поступающим на вход INTR. Обычно вход NMI используют для указания МП БИС о каких-либо сбоях в системе (сбоях в источнике питания, ошибках в памяти). При определении наличия сигнала на входе NMl МП БИС нет необходимости получать код для инициализации процесса обслуживания прерывания и соответственно она не формирует два машинных цикла INTA в ответ на запрос по входу NMI.

Внутренние прерывания формируются за счет выполнения МП БИС команды прерывания (тип команды зависит от источника прерывания).

При установке флага переполнения О=1 в результате выполнения какой-либо команды программы формируется команда прерывания – INTO (прерывание по переполнению).

Микропроцессорная БИС формирует прерывание сразу же после выполнения команд DIV или IDIV, если частное от деления больше, чем разрядность используемых регистров.

При установке флага Т=1 МП БИС автоматически формирует прерывание, которое воздействует сразу после выполнения любой текущей команды. Этот тип прерывания называют одношаговым или первым типом, и он является мощным средством при отладке программ. При выполнении одношагового типа прерывания МП БИС производит обычную последовательность операций, а именно записывает в стек флаги МП БИС, содержимое регистров CS и IP. В дополнение к этому очищаются флаги I и Т. В регистры CS и IP записываются соответственно из адресов 00006, 00007 и 00004, 00005 новые значения базового адреса сегмента и смещения для передачи управления на соответствующую подпрограмму обслуживания прерывания. В качестве такой подпрограммы может быть использована подпрограмма выдачи результата выполнения программы на печать, дисплей и т. д. По окончании выполнения подпрограммы после получения команды IRET (возврат из подпрограммы) из стека извлекаются и записываются в МП БИС флаги и содержимое регистров IP и СР. Из приведенных пояснений ясно, что при выполнении одношагового типа прерывания МП БИС обслуживает прерывания обычным способом. Однако обеспечение вывода результатов выполнения отдельных блоков в программе или даже отдельных команд с целью их последующего анализа путем задания в нужном месте программ режима одношаговых прерываний является удобным средством при исследовании работы программ.

Типы внутренних прерываний имеют ряд общих свойств:

1) код прерывания сообщается МП БИС перед командой или включен в команду прерывания;

2) на выходе МП БИС не формируются сигналы INTA;

3) за исключением одношагового типа, внутренние прерывания не могут быть программно отключены;

4) за исключением одношагового типа, любой из внутренних прерываний имеет более высокий приоритет по отношению к внешним прерываниям.

Любой из 256 возможных типов прерывания характеризуется вектором прерывания. Векторы прерывания занимают 1К байт адресного пространства. На рисунке 19 показано распределение начал векторов прерывания по адресам памяти. Как видно из рисунка, каждый вектор занимает четыре ячейки памяти, при этом два младших адреса в векторе используются для записи смещения в сегменте, а два старших — для записи базового адреса сегмента.

Рисунок 26 – Распределение векторов прерываний в памяти микроЭВМ

Формирование адреса передачи управления на соответствующую подпрограмму обслуживания прерывания в BIU происходит так же, как и при обращении к любой ячейке памяти, а именно: содержимое двух младших адресов вектора прерывания записывается в регистр IP, coдержимое старших двух адресов записывается в регистр CS. После этого содержимое CS смещается на четыре разряда влево и откладывается с содержимым IP. Полученное 20-разрядное число определяет адрес начала подпрограммы прерывания.

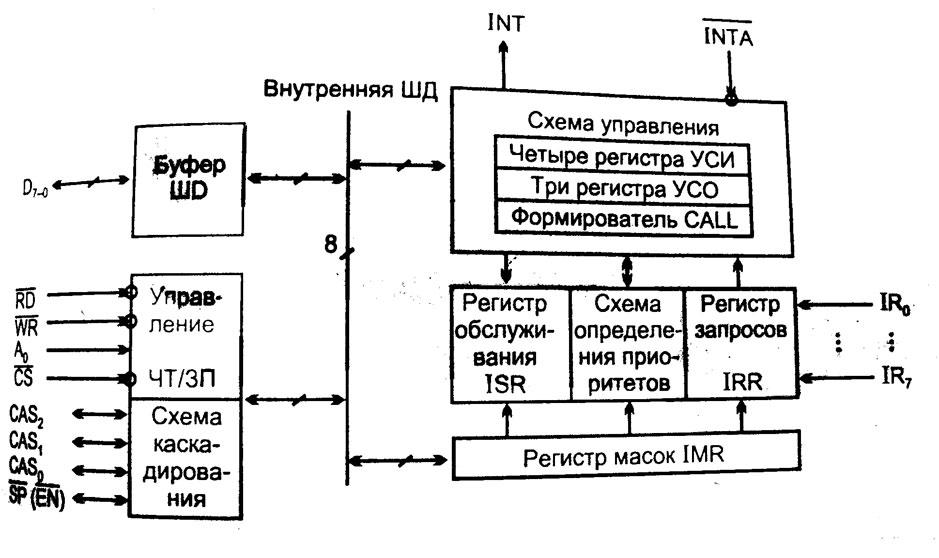

В данной микропроцессорной системе используется контроллер прерываний К1810ВН59А. Структурная схема изображена на рисунке 25.

Рисунок 27 – Структурная схема контроллера прерываний К1810ВН59А

включение контроллера прерываний в систему показано на рисунке 22.

Рисунок 28 – Включение контроллера прерываний в МПС

Контроллер принимает запросы от внешних устройств, определяет, какой из незамаскированных запросов имеет наивысший приоритет, сравнивает его с приоритетом текущей программы и при соответствующих условиях выдает запрос прерывания INT для МП. После подтверждения запроса МП должен получить от котроллера информацию, которая укажет на подпрограмму, соответствующую данному ВУ.

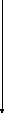

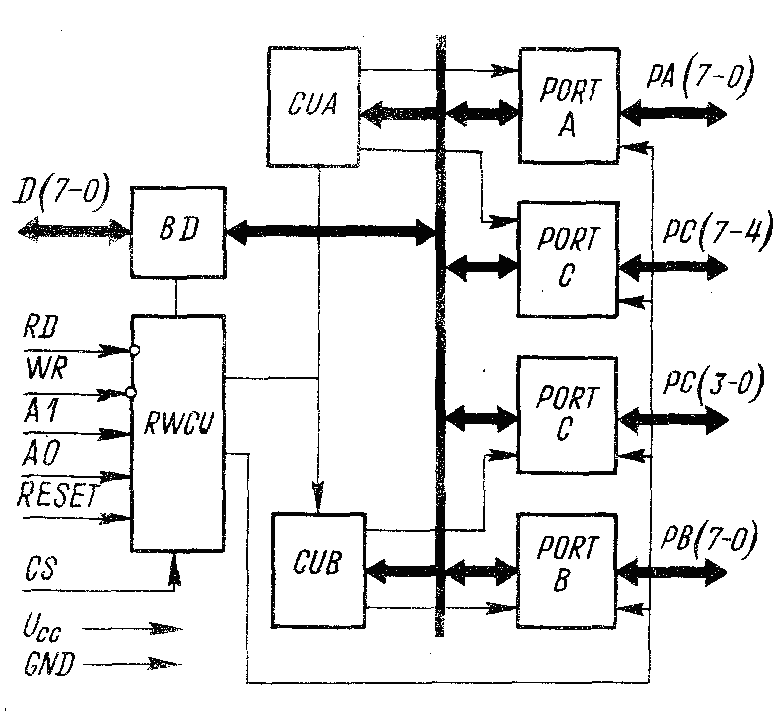

4.3 Программируемый параллельный интерфейс КР580ВВ79

Микросхема КР580ВВ79 представляет собой программируемое устройство, используемое для ввода/вывода параллельной информации. Схема позволяет осуществлять обмен 8-разрядными данными по трем каналам: А, В и С. Направление обмена и режим работы для каждого канала задается программно. Каналы служат для передачи, как данных, так и управляющих сигналов.

В состав БИС входят: двунаправленный 8-разрядный буфер данных ВD, связывающий программируемый параллельный интерфейс с системной шиной данных, блок управления записью/чтением RWCU, обеспечивающий управление внешними и внутренними передачами данных, управляющих слов и информации о состоянии программируемого параллельного интерфейса, три 8-разрядных канала ввода/вывода РОRТ А, В и С для обмена информацией с внешними устройствами, схема управления группой А СUA, вырабатывающая сигналы управления каналом А и старшими разрядами канала С РС (7-4), схема управления группой В СUВ, вырабатывающая сигналы управления каналом В и младшими разрядами канала С РС (3-0).

Назначения входных, выходных и управляющих сигналов приведены в таблице 12. Сигналы управления работой программируемого параллельного интерфейса подаются на блок К/УС11 и вместе с адресными входами А0, А1 задают вид операции, выполняемой БИС.

Структурная схема программируемого параллельного интерфейса КР580ВВ79 представлена на рисунке 23.

PA (7-0)

CUA

PORT

A

D (7-0)

PC (7-4)

PORT

C

BD

PC (3-0)

PORT

C

RD

WR

RWCU

A 1

PB (7-0)

A 0

PORT

B

CUB

RESET

CS

UCC

GND

Рисунок 29 - Структурная схема программируемого параллельного

интерфейса КР580ВВ79

Основные электрические параметры микросхемы КР580ВВ79:

- выходное напряжение логического нуля UOL, В менее 0,4;

- выходное напряжение логической единицы UOH, В более 2,4;

- ток потребления от источника питания ICC, мА менее 60;

- ток утечки каналов А, В, С, D при невыбранном

режиме IIOZ, мкА более 100;

- ток утечки на управляющих входах IIL, мкА 10.

Режимы работы каждого из каналов ППИ программируется с помощью управляющего сигнала. Управляющее слово может задать один из трех режимов основной режим ввода/вывода (режим 0), стробируемый ввод/вывод (режим 1) и режим двунаправленной передачи информации (режим 2).Одним управляющим словом можно установить различные режимы работы для каждого из каналов.

Канал А может работать в любом из трех режимов, канал B в режиме 0 и режиме 1. Канал С может быть использован для передачи данных только в режиме 0, а в остальных режимах он служит для передачи управляющих сигналов , сопровождающих процесс обмена по каналам А и B.

Рисунок 30 - Условное графическое обозначение КР580ВВ79

Таблица 14 – Назначение выводов ПККИ КР580ВВ79

|

№ вывода |

Обозначение

|

Наим-е |

Назначение |

Тип сиг-ла |

Сост-е | |

|

Англ. |

Рус. | |||||

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

39; 38; 8;7;6; 5; 2; 1 |

RET (7-0) |

ВЗВ(7-0) |

Сигналы линий возврата |

Входы линий возврата, служащие для подачи сигналов от датчиков че |

вход |

1 |

Продолжение таблицы 14

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

|

|

|

|

рез контакты клавиш или ключа |

|

|

|

19;18; 17;16; 15;14; 13;12 |

D(7-0) |

Д(7-0) |

Шина данных |

Входы/выходы канала данных |

вх/вых |

1,0, в.с. |

|

3 |

CLK |

ВЫХ |

Импульс синхронизации |

Вход сигнала синхронизации микросхемы |

выход |

1 |

|

4 |

INT |

З.ПР |

Запрос на прерывание |

Высокий уровень сигнала указывает на запрос на прерывание |

вход |

1 |

|

9 |

CLR |

СБР |

Сброс |

Вход сигнала установки ПККИ в исходное состояние |

выход |

1 |

|

10 |

RD |

ЧТ |

Чтение |

Вход сигнала чтения L-уровня, разрешающего передачу информации из ПККИ в канал данных МП |

вход |

0 |

|

11 |

WR |

ЗП |

Запись |

Вход сигнала записи L-уровня, разрешающего передачу информации из канала данных МП в ПККИ |

вход |

0 |

|

14 |

GND |

ОБЩ |

Сигнал питания |

напряжение питания 0 В |

- |

- |

|

20 |

UCC |

UИП1 |

Сигнал питания |

напряжение питания +5 В |

- |

- |

|

21 |

|

ЗПД/ЧТД |

Запись/ чтение данных |

Управление записью/чтением данных или команд; при сигнале Н-уровня происходит запись команды/чтения состояния ПККИ, при сигнале L-уровня — запись/чтение данных |

вход |

0 |

|

23 |

BD |

ГШ |

Сигнал гашения |

Выход сигнала гашения отображения L-уровня |

выход |

0 |

Продолжение таблицы 14

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

22 |

CS |

ВК |

Выбор кристалла |

Вход сигнала выбора микросхемы; L-уровень сигнала разрешает работу схемы |

вход |

0 |

|

24-27 |

DSP A ( 3-0) |

ВЫХ А (3-0) |

Выходы канала А |

Выходы канала А |

выход |

1 |

|

28-31 |

DSP B ( 3-0) |

ВЫХ В (3-0) |

Выходы канала В |

Выходы канала В |

выход |

1 |

|

32-35 |

S0,S1, S2, S3 |

СС |

Схема согласования |

Подключение схемы согласования |

выход |

1 |

|

36 |

SH |

СДВ |

Сигнал сдвига |

Вход сигнала сдвига, используемого для ска-нирования клавиатуры |

вход |

1 |

|

37 |

V/ STB |

СК.К/ СТБ |

Сканирование клавиатуры или стробирующего сигнала |

Вход сигнала управления для режима сканирования клавиатуры или стробирующего сигнала для режима ввода по стробу |

вход |

0 |

Режим 0 применяется при синхронном обмене или при программной организации асинхронного обмена. Микросхема может рассматриваться в этом режиме как устройство, состоящих из четырех портов, независимо настраиваемых на ввод или вывод. Вывод информации осуществляется по команде OUT микропроцессора с фиксацией выводимой информации в регистрах каналов, а ввод - по команде IN, без запоминания информации.

Режим 1 обеспечивает стробируемый однонаправленный обмен информации с внешним устройством. Передача данных производится по канал А и В, а линии канал С управляют передачей. Работу канала в режиме 1 сопровождают три управляющих сигнала.

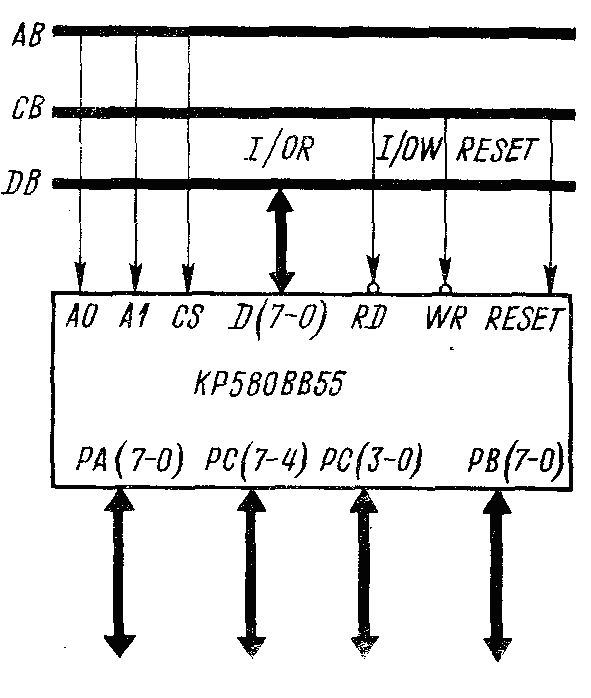

Сопряжение БИС КР580ВВ79 со стандартной системной шиной показано на рисунке 31.

AB

CB

DB

I/OR

I/OW

RESET

A0 A1 CS D (7-0) RD WR RESET

КР580ВВ79

PA (7-0) PC (7-4) PC (3-0) PB (7-0)

Рисунок 31 – Схема сопряжения программируемого параллельного

интерфейса КР580ВВ79 со стандартной системной шиной

В режиме 1 для ввода информации используют следующие управляющие сигналы: строб приема STB - входной сигнал, формируемый внешним устройством, указывает на готовность ВУ к вводу информации; подтверждение приема IBF - выходной сигнал ППИ, сообщающий ВУ об окончании приема данных в канал; запрос прерывания INTER - выходной сигнал ППИ, информирующий МП о завершении приема информации в канале.

Для вывода информации в режиме 1 используются следующие управляющие сигналы: строб записи OBF - выходной сигнал, указывающий внешнему устройству о готовности к выводу, формируется по фронту WR; подтверждение записи ACK - входной сигнал от внешнего устройства, подтверждающий прием информации из ППИ; запрос прерывания INTR - выходной сигнал ППИ, информирующий МП о завершении операции вывода информации.

Режим два обеспечивает двунаправленную передачу информации по каналу А к внешнему устройству и обратно. Процесс обмена сопровождают пять управляющих сигналов, подаваемых по линиям PC7 - PC3. Оставшиеся 11 интерфейсных линий могут настраиваться на режим 0 или режим 1.Управление установкой внутреннего сигнала INTE для операции ввода осуществляется по линии PC4, а для операции вывода по линии PC6.

В режимах 1 и 2 возможно проведение контроля за состоянием работы внешнего устройства и ППИ .Контроль осуществляется чтением слова - состояния канала С по команде OUT.

В состав БИС входят: буферы клавиатуры и датчиков (BF), включающие также схему управления и устранения дребезжания клавиатуры, предназначенные для хранения входной информации в режимах сканирования клавиатуры, наборов датчиков и ввода по стробу; схема управления вводом/выводом (RWCU), вырабатывающая сигналы управления обменом с МП и внутренними пересылками данных и команд; буферы канала данных (ВD), предназначенные для обмена информацией между ПККИ и МП; ОЗУ клавиатуры датчиков (STACK), работающее по принципу FIFO и предназначенное для хранения кодов позиций клавиш и состоянии ключей датчиков; ОЗУ отображения (RAM), сохраняющее информацию, отображаемую на дисплее; регистр адреса ОЗУ отображения (RGА), предназначенный для хранения адреса данных, записываемых или считываемых микропроцессором; схема управления и синхронизации (СU), состоящая из регистров хранения команд и счетчика синхронизации; схема анализа состояния ОЗУ-датчиков (STCU) контролирующая число символов в ОЗУ и формирующая сигнал прерывания INT; регистры ОЗУ отображения (RG), предназначенные для хранения данных отображаемых на выходах каналов А и В; счетчик сканирования (СТ), вырабатывающий сигналы сканирования клавиатуры, датчиков и дисплея.

В качестве схемы согласования используется дешифратор К514ИД1. Его условное графическое обозначение изображено на рисунке 32.

Рисунок 32 – Условное графическое изображение дешифратора К514ИД1

Рисунок 33 - Структурная схема ПККИ

Схема подключения БИС к шинам показана на рисунке 34.

Рисунок 34 - Схема подключения ПККИ

Таблица 15 – Назначение выводов К514ИД1

|

№ вывода |

Обозначение

|

Наименование |

Назначение |

Тип сигнала |

Состояние | |

|

Англ. |

Рус. | |||||

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

7, 1, 2, 6 |

V0 – V3 |

Вх.0 – Вх.3 |

Входной сигнал |

Вход сигнала, который необходимо дешифровать |

вход |

1 |

Продолжение таблицы 15

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

4 |

G |

Г |

Гашение |

При активном состоянии индикация пропадает |

вход |

0 |

|

9, 10, 11, 12, 13, 14, 15 |

a, b, c, d, e, f, g |

Вх.0 – Вх.3 |

Входной сигнал |

Вход сигнала, который необходимо дешифровать |

вход |

1 |

|

8 |

UCC |

UИП1 |

Сигнал питания |

напряжение питания +5 В |

- |

- |

|

16 |

GND |

ОБЩ |

Сигнал питания |

напряжение питания 0 В |

- |

- |

4.4 Программируемый таймер К1810ВИ54

Программируемый таймер (ПТ) К1810ВИ54 предназначен для генерации времязадающих функций, программно-управляемых временных задержек с возможностью программного контроля их выполнения. Программируемые таймеры применяются в МПС, выполненных на базе МПК БИС К580, К1810, К1821, используемых в задачах управления и измерения в реальном масштабе времени с тактовой частотой до 8 МГц. Конструктивно эти ПТ совместимы с ПТ типа К580ВИ53, отличаются от них повышенным быстродействием и расширенными функциональными возможностями.

Рисунок 36 – Структура схема ПТ К1810ВИ54

Программируемый таймер К1810ВИ54 включает три независимых канала, каждый из которых может быть запрограммирован на работу в одном из шести режимов для двоичного или двоично-десятичного счета. Структурная схема ПТ показана на рисунке 36, его условное графическое обозначение – на рисунке 37.

Рисунок 37 - Условно-графическое обозначение ПТ К1810ВИ54

Таблица 16 – Назначение выводов ПТ КР580ВИ54

|

№ вывода |

Обозначение

|

Наименованиие |

Назначение |

Тип сигнала |

Состояние | |

|

Англ. |

Рус. | |||||

|

1; 2: 3: 4.5;6;7;8 |

D(7-0) |

Д0 - Д7 |

Шина данных |

Передача данных |

выход |

1,0,в.с. |

|

22 |

RD |

ЧТ |

Чтение |

Сигнал «чтение» |

вход |

0 |

|

23 |

WR |

ЗП |

Запись |

Сигнал «запись» |

вход |

0 |

|

19; 20 |

А0, A1 |

А0, A1 |

Адресные входы |

Адресные входы, выбирающие один из каналов ПТ или управляющий регистр |

вход |

1,0,в.с. |

|

21 |

CS |

ВК |

Выбор кристалла |

Выбор микросхемы |

вход |

0 |

|

9; 15; 18 |

CLK0 - CLK2 |

ВХ0–ВХ2 |

Импульсы синхронизации |

Входы синхронизации счетчиков |

вход |

1 |

|

11; 14; 16 |

GATA0–GATA2 |

Р0-Р2 |

Импульсы управления |

При GATA=l разрешается выполнение функций; для некоторых режи |

вход |

1 |

Продолжение таблицы 16

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

|

|

|

|

мов работы разрешается поступление тактовых сигналов на вход счетчика/таймера, для других (импульсный генератор и генератор меандра) открывается выходной буфер OUT. |

|

|

|

10; 13: 17 |

OUT0-OUT2 |

ВЫХ0–ВЫХ2 |

Выходные сигналы |

Выходные сигналы |

выход |

1 |

|

24 |

UCC |

UИП |

Сигнал питания |

напряжение питания +5 В |

- |

- |

|

12 |

GND |

ОБЩ |

Сигнал питания |

напряжение питания 0 В |

- |

- |

4.5 Выбор АЦП

АЦП представляют собой устройства, преобразующие амплитуду (уровни) или другие параметры аналоговых сигналов различной природы в цифровой вид. Аналого-цифровые преобразователи позволяют вводить информацию, содержащуюся в массиве аналоговых сигналов, поступающих от датчиков, измерительных приборов и других устройств, в цифровые вычислительные или управляющие устройства, блоки и системы, в которых производится обработка цифровой информации.

К настоящему времени разработаны и широко применяются несколько основных разновидностей АЦП:

- АЦП двойного интегрирования;

- АЦП последовательного счета;

- АЦП поразрядного уравновешивания (последовательного приближения);

-АЦП параллельного действия.

Основными параметрами преобразователей являются: динамический диапазон входных сигналов, передаточная характеристика преобразования, число уровней квантования, цена младшего значащего разряда (МЗР) преобразования (ширина канала), быстродействие, погрешности преобразования (дифференциальная и интегральная нелинейности преобразования).

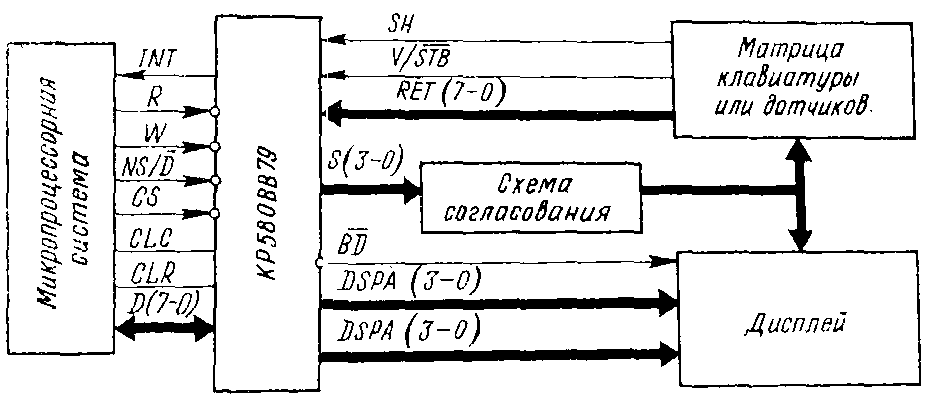

Из всех видов АЦП наиболее простыми по принципу действия, но и наиболее сложными по конструктивной и технологической выполнимости являются АЦП параллельного действия.

На рисунке 21 представлена структурная схема АЦП параллельного действия, который содержит: источник опорного напряжения (Uоп), делитель опорного напряжения (R1-Rn), n компараторов (K1-Kn) равное числу уровней квантования, шифратор унитарного кода в двоичный код (D1). Каждый компаратор имеет входной дифференциальный каскад с двумя входами: инвертирующим и неинвертирующим. АЦП параллельного действия работает следующим образом. Делитель напряжений задает ряд опорных напряжений на всех, например, инвертирующих входах компараторов. Опорное напряжение на любом из компараторов определяется из выражения:

Un= (Uоп/ N) ⋅ n ,

где: N - число уровней квантования АЦП;

n - номер компаратора (номер канала квантования);

Uоп/ N - ширина канала (цена младшего разряда АЦП).

Rn – резисторы прецизионного делителя;

Kn – компараторы уровня сигналов;

D1 – шифратор унитарного кода в двоичный

Рисунок 38 – Структурная схема АЦП параллельного действия

Входное преобразуемое напряжение Uвх поступает на все неинвертирующие входы компараторы. По сигналу "Строб", поступающего с устройства управления, входное напряжение сравнивается каждым компаратором с опорным напряжением. Компараторы выдают на выходе результат сравнения в виде "0" или "1" в зависимости от знака разности между опорным и входным напряжениями на их двух входах. После окончания сравнения кодовая комбинация с компараторов в виде унитарного кода поступает на шифратор, который на выходе выдает двоичный код уровня входного сигнала. Если для преобразователя известна цена младшего разряда (ЦМР), то величина уровня входного сигнала определяется произведением ЦМР и десятичного выходного кода преобразователя.

АЦП параллельного действия обладают самым высоким быстродействием из всех видов преобразователей. Время преобразования у современных устройств такого вида составляет величину 5-10 нс. Эти АЦП отличаются сравнительно небольшим числом уровней квантования (6-8 и редко 9-10 двоичных разрядов) и средней величиной погрешности. Следует отметить также технологическую сложность производства АЦП этого вида из-за большого числа элементов каждого вида, примерно равному числу уровней квантования.

Широкое распространение однобайтных процессоров вызвало разработку восьмиразрядных аналого-цифровых преобразователей. Таковыми, в частности, являются АЦП типов К572ПВ3 и К572ПВ4.

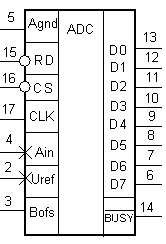

Рисунок 39 – Условное графическое обозначение АЦП К572ПВ3

Условное графическое обозначение АЦП К572ПВ3 показано на рисунке 3. Время преобразования этого АЦП равно 7,5 мкс, ток потребления от одного источника питания 5 В составляет всего лишь 5 мА. Управляется сигналами микропроцессора CS и RD, при этом АЦП функционирует подобно статической памяти с произвольной выборкой (RAM), постоянной памяти (ROM) или медленной памяти. Включает в себя компаратор, тактовый генератор и выходные схемы с тремя состояниями. Это значительно упрощает применение данного АЦП в системах сопряжения с микропроцессором. АЦП КР572ПВ3 выпускается по бКО.348.432-08ТУ в пластмассовом корпусе 238.18-3. В таблице 15 отображены назначения выводов микросхемы КР572ПВ3.

АЦП имеет два одинаковых входа AI1 и AI2, соединённых внутренними резисторами с одним входом компаратора. На этот же вход компаратора подаётся выходной ток цифро-аналогового преобразователя, управляемого регистром последовательного приближения. Таким образом, АЦП обеспечивает преобразование в код суммы напряжений, подаваемых на входы AI1 и AI2. При практическом использовании этого АЦП на вход AI1 подают входное напряжение Uвх, а на вход AI2 – напряжение, с помощью которого производят регулировку нуля АЦП.

Управление

работой АЦП К572ПВ3 осуществляется с

помощью сигналов, подаваемых на входы

(выбор кристалла) и

(выбор кристалла) и (чтение). Переход 0/1 на входе

(чтение). Переход 0/1 на входе запускает схему сброса АЦП, потенциал

0 на входе

запускает схему сброса АЦП, потенциал

0 на входе осуществляет запуск преобразователя

при условии, что предварительно был

осуществлён его сброс. Таким образом,

если

осуществляет запуск преобразователя

при условии, что предварительно был

осуществлён его сброс. Таким образом,

если =0,

то переход 0/1 на входе

=0,

то переход 0/1 на входе обусловит

сброс и запуск преобразователя. Если

же

обусловит

сброс и запуск преобразователя. Если

же =1,

то этот переход вызывает только сброс,

а запуск произойдет по спаду 1/0 на входе

=1,

то этот переход вызывает только сброс,

а запуск произойдет по спаду 1/0 на входе .

Выход BU (АЦП занят) принимает потенциал

«нуль» тогда, когда осуществляется

процесс преобразования. Данные на

кодовом выходе N существуют при сочетании

сигналов

.

Выход BU (АЦП занят) принимает потенциал

«нуль» тогда, когда осуществляется

процесс преобразования. Данные на

кодовом выходе N существуют при сочетании

сигналов =0,

=0, =0,

=0, =1,

если же этого сочетания нет, если же

этого сочетания нет, то выход находится

в высокоимпендансном состоянии.

=1,

если же этого сочетания нет, если же

этого сочетания нет, то выход находится

в высокоимпендансном состоянии.

Таблица 17 – Назначение выводов АЦП К572ПВ3

|

№ вывода |

Обозначение |

Наименование |

Назначение |

Тип сигнала |

Состояние | |

|

Англ. |

Рус. | |||||

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

1 |

Uсс |

Uп |

Напряжение питания |

Напряжение питания +5 В |

- |

- |

|

2 |

UREF |

Uоп |

Опорное напряжение |

Выполняет калибровочную функцию |

вх |

- |

|

3 |

BOFS |

Uсм |

Смещение характеристики преобразования |

Вход напряжения смещения характеристики |

вх |

- |

|

4 |

AIN |

Uвх |

Аналоговый вход |

Вход аналогового сигнала |

вх |

- |

|

5 |

AGND |

ОБЩ |

Аналоговая земля |

Напряжение питания 0 В |

- |

- |

|

6-9, 10-13 |

D7 – D0 |

Д7– Д0 |

Шина данных |

Выход данных |

вых |

1,0 |

|

14 |

_____ BUSY |

ВC |

Выход состояния |

L-уровень сигнала отображает подключение преобразователя к ППИ |

вых |

0 |

Продолжение таблицы 17

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

15 |

___ RD |

СТБ |

Вход управления |

Управление схемой цифрового преобразования |

вх |

0 |

|

16 |

__ CS |

ВК |

Выбор кристалла |

Вход управления |

вх |

0 |

|

17 |

CLK |

СИНХР |

Вход тактирования |

Синхронизация со схемой ППИ |

вх |

1,0 |

|

18 |

DGND |

ОБЩ |

Цифровая земля |

L-уровень сигнала разрешает считывание информации с регистра, |

вх |

0 |

Восьмиразрядный код с АЦП подается на один из портов программируемого параллельного адаптера (ППА) КР580ВВ55. Этот адаптер позволяет по команде микропроцессора передавать данные из АЦП на шину данных, для их дальнейшей обработки. Дальнейшая обработка данных производится в соответствии с программой, обслуживающей процесс измерения. Основной задачей этой программы является опрашивание АЦП с заданной периодичностью и вывод результатов измерения на дисплей. Кроме того, микроЭВМ позволяет записывать данные о результатах измерений в оперативную память для их дальнейшей статистической обработки.

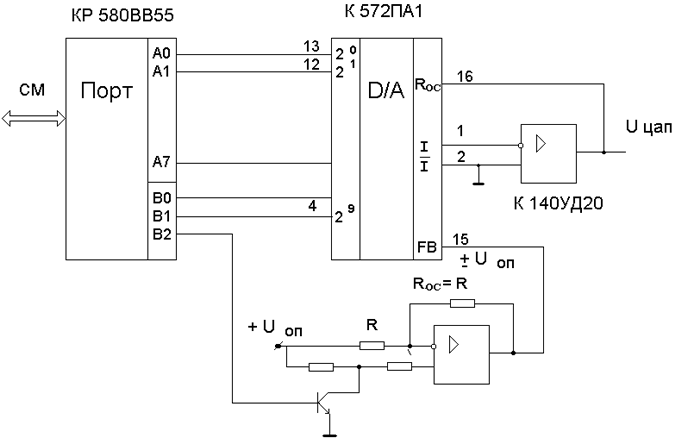

4.6 Выбор ЦАП

Обычно в микропроцессорных системах применяется десятиразрядный ЦАП с внешними или внутренними регистрами с выходным напряжением до +10В. Для нашей системы выберем распространенный цифро-аналоговый преобразователь с токовым выходом К572ПА1. Время преобразования микросхемы - 5 мс. Его условное графическое обозначение изображено на рисунке 40, назначение выводов микросхемы – в таблице 18.

Рисунок 40 – условное графическое обозначение ЦАП К572ПА1

Таблица 18 – Назначение выводов ЦАП К572ПА1

|

№ вывода |

Обозначение |

Наименование |

Назначение |

Тип сигнала |

Состояние | |

|

Англ. |

Рус. | |||||

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

1 |

OUT1 |

Uвых1 |

Аналоговый выход |

Выход аналогового сигнала |

вых |

- |

|

2 |

OUT2 |

Uвых2 |

Аналоговый выход 2 |

Выход аналогового сигнала 2 |

вых |

- |

|

3 |

GND |

ОБЩ |

Общий |

Напряжение питания 0В |

вх |

0 |

|

4-13 |

D7 – D0 |

Д7– Д0 |

Шина данных |

Вход данных в преобразователь |

вх |

1,0 |

|

14 |

Uсс |

Uп |

Напряжение питания |

Напряжение питания +5 В |

- |

- |

|

15 |

UREF |

Uоп |

Опорное напряжение |

Выполняет калибровочную функцию |

вх |

- |

|

16 |

Roc |

ОС |

Обратная связь |

Подключение обратной связи выхода |

вх |

- |

Микросхема К572ПА1 реализована как сетка R-2R резисторов с управляющими МОП-ключами. С выходов 2 и 3 снимаются токи, которые должны быть преобразованы в напряжение разностного сигнала с помощью ОУ. Выводы 15 и 16 служат для включения ЦАП в цепь обратной связи операционного усилителя. На вывод 14 ИМС должно быть подано опорное напряжение, например 12 В, которое используется в данной МПС. Применение второго ОУ обеспечивает двуполярное напряжение на выходе всей схемы. Указанное включение данного ЦАП не единственно возможное. Так как ИМС К572ПА1 - десятиразрядная, а регистр - восьмиразрядный, то использовано может быть только 8 младших его разрядов.

Изменение знака выходного напряжения на выходе ЦАП осуществляется либо изменением знака опорного напряжения, либо путем сложения напряжений.

Рисунок 41 – Подключение ЦАП с духквадрантным умножением

Рисунок 42 – Подключение ЦАП с духквадрантным умножением

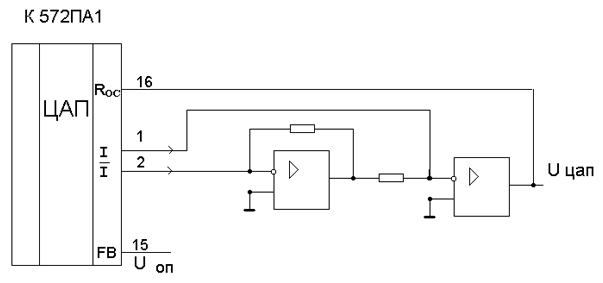

4.7 Выбор программируемого параллельного интерфейса

БИС программируемого параллельного интерфейса КР580ВВ55 предназначена для организации ввода/вывода параллельной информации различного формата и позволяет реализовать большинство известных протоколов обмена по параллельным каналам. БИС программируемого параллельного интерфейса (ППИ) может использоваться для сопряжения микропроцессора со стандартным периферийным оборудованием (дисплеем, телетайпом, накопителем).

В состав БИС входят: двунаправленный 8-разрядный буфер данных (ВD), связывающий ППИ с системной шиной данных; блок управления записью/чтением (RWCU), обеспечивающий управление внешними и внутренними передачами данных, управляющих слов и информации о состоянии ППИ; три 8-разрядных канала ввода/вывода (РОRТ А, В и С) для обмена информацией с внешними устройствами; схема управления группой А (СUA), вырабатывающая сигналы управления каналом А и старшими разрядами канала С[РС(7-4)]; схема управления группой В (СUВ), вырабатывающая сигналы управления каналом В и младшими разрядами канала С[РС(3-0)]. Структурная схема ППИ приведена на рисунке 43.

Рисунок 43 — Структурная схема ППИ КР580ВВ55

Рисунок 44 – Условное графическое обозначение ППИ КР580ВВ55

Таблица 19 - Описание выводов ППИ КР580ВВ55.

|

№ вывода |

Обозначение |

Наименование |

Назначение |

Тип сигнала |

Состояние | |

|

Англ. |

Рус. | |||||

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

27; 28; 29; 30; 31; 32; 33; 34 |

D(7 – 0) |

Д0 - Д7 |

Шина данных |

Вход/выход данных |

вх/вых |

1,0,в.с. |

|

5 |

RD |

СТБ |

Чтение |

L-уровень сигнала разрешает считывание информации с регистра, адресуемого по входам А0, А1 на шинуD(7 – 0) |

вход |

0 |

|

6 |

CS |

ВК |

Выбор кристалла |

L-уровень сигнала подключает ППИ к системной шине |

вход |

0 |

|

7 |

GND |

ОБЩ |

Сигнал питания |

напряжение питания 0 В |

- |

- |

Продолжение таблицы 19

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

9; 8 |

A0, A1 |

A0, A1 |

Входы адреса |

Входы для адресации внутренних регистров ППИ |

вход |

1 |

|

26 |

UCC |

UИП1 |

Сигнал питания |

напряжение питания +5 В |

- |

- |

|

35 |

RESET |

СБР |

Сброс |

Н-уровень сигнала обнуляет регистр управляющего сигнала и устанавливает все порты в режим ввода |

вход |

1 |

|

36 |

WR |

ЗП |

Запись |

L-уровень сигнала разрешает запись информации с шиныD(7 – 0) в регистр ППИ, адресуемый по входам А0, А1 |

вход |

0 |

|

37; 38; 39; 40; 1; 2; 3; 4 |

PA(7 – 0) |

ПА(7-0) |

Канал А |

Вход/выход канала А |

вх/вых |

1 |

|

15; 24; 23; 22; 21; 20; 19; 18 |

PB(7 – 0) |

ПB(7 – 0) |

Канал В |

Вход/выход канала В |

вх/вых |

1 |

|

10; 11; 12; 13; 17; 16; 15; 14 |

PC(7 – 0) |

ПC(7 – 0) |

Канал С |

Вход/выход канала С |

вх/вых |

1 |

Назначения входных, выходных и управляющих сигналов ППИ приведены при описании выводов микросхемы в таблице 19. Сопряжение БИС КР580ВВ55 со стандартной системной шиной показано на рисунке 45. Сигналы управления работой ППИ подаются на блок RWCU и вместе с адресными входами А0, А1 задают вид операции, выполняемой БИС.

Рисунок 45 - Схема подключения ППИ КР580ВВ55