- •1 Анализ технического задания

- •2.2 Арифметическо-логическое устройство

- •2.3 Память микроконтроллера

- •2.4 Управление работой микроконтроллера

- •2.5 Организация ввода-вывода информации в микроконтроллере

- •3.2 Постоянное запоминающее устройство

- •4.3 Контроллер прямого доступа к памяти (кпдп)

- •4.4 Программируемый интервальный таймер (пит)

- •5.2 Шинный формирователь к580ва86

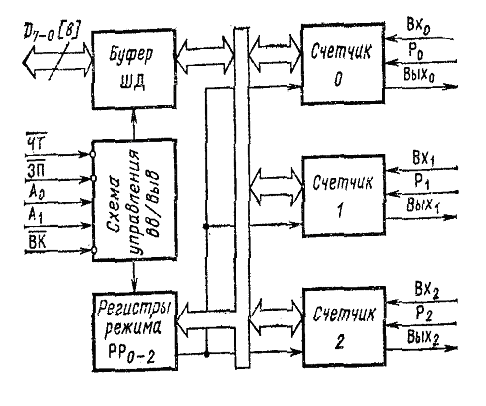

4.4 Программируемый интервальный таймер (пит)

На рисунке 28 показана схема ПИТ К580ВИ53.

Рисунок 28 - Схема программируемого интервального таймера

К580ВИ53

В состав таймера входят три независимых 16-разрядных вычитающих счетчика, схема управления вводом—выводом, регистры режимов работы счетчиков и буфер ШД, через который осуществляется обмен информацией между МП и таймером. Счетчики ПИТ могут работать в диапазоне частот от 0 до 2 МГц в двоичном и двоично-десятичном кодах.

Через

буфер ШД в счетчики ПИТ можно загрузить

начальные значения по сигналам ЗП и

считать текущее значение по сигналам

ЧТ, Входными считаемыми сигналами для

счетчиков являются сигналы Вх, по заднему

фронту которых счетчики выполняют

операцию декрементирования своего

содержимого. До тех пор, пока на ПИТ не

подан сигнал

![]() ,

операции записи и чтения невозможны,

однако сигнал

,

операции записи и чтения невозможны,

однако сигнал

![]() на работу счетчиков влияния не оказывает.

Сигналы на входы А1-0

подаются с соответствующих линий ША и

адресуют один из внутренних регистров

ПИТ.

на работу счетчиков влияния не оказывает.

Сигналы на входы А1-0

подаются с соответствующих линий ША и

адресуют один из внутренних регистров

ПИТ.

Инициализация и управление работой ПИТ, как и других интерфейсных БИС, осуществляется с использованием управляющих слов, загружаемых в регистры режимов работы, и ограниченного числа линий управления и адресации.

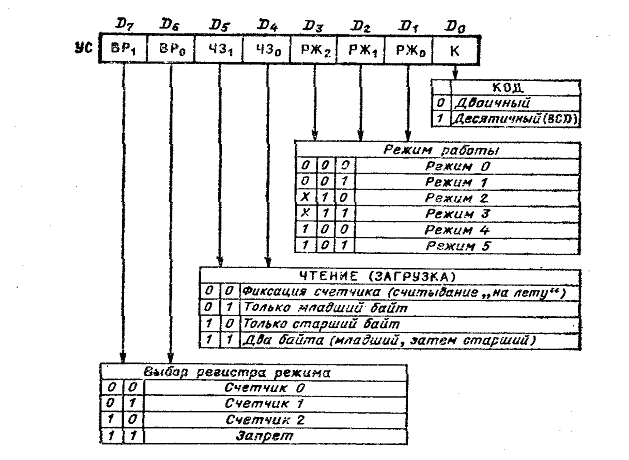

Формат управляющего слова показан на рисунке 29.

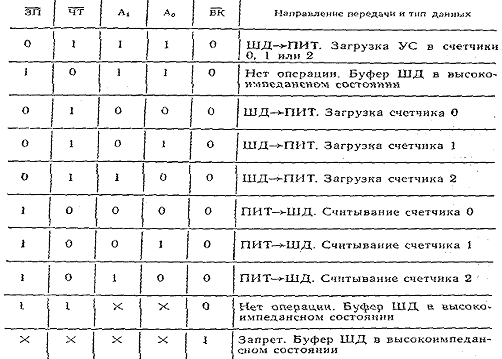

Функции управляющих и адресных входных сигналов перечислены в таблице 7.

Двухразрядное поле ВР1-0 выбора регистра режима адресует регистр режима для счетчиков 0, 1 или 2. Поле ЧЗ1-0 чтения/записи определяет порядок считывания текущего значения адресуемого счетчика или загрузки в него начального значения. В поле РЖ1-0 кодируется один из шести возможных режимов работы адресуемого счетчика. И, наконец, разряд К определяет код, в котором работает счетчик.

Рисунок 29 - Формат управляющего слова

Таблица 7 - Функции управляющих и адресных входных сигналов

5 РАЗРАБОТКА ИНТЕРФЕЙСА И УТОЧНЕННОЙ СТРУКТУРНОЙ

СХЕМЫ МИКРОПРОЦЕСОРНОЙ СИСТЕМЫ

5.1 Буферный регистр КР580ИР82

Буферизация

шин необходима для повышения их

нагрузочной способности по току и

емкости. Применение регистров КР580ИР82

в качестве буфера увеличивает нагрузочную

способность линий ША до 32 мА и 300 пФ. Один

из разрядов регистра (выводы 5, 15)

использован для буферизации линии

сигнала

![]() ,

который управляет режимом записи-считывания.

,

который управляет режимом записи-считывания.

Рисунок 30 – УГО регистра КР580ИР82

Запись

информации осуществляют по стробу,

подаваемому на вход СЕ (вывод 11), либо

при наличии на этом входе постоянного

уровня логической 1. Считывание информации

возможно при наличии на входе ОЕ (вывод

9) сигнала с уровнем логического 0. При

![]() =1

выходы принимают третье состояние.

=1

выходы принимают третье состояние.

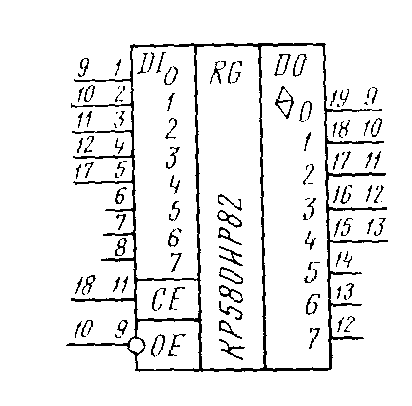

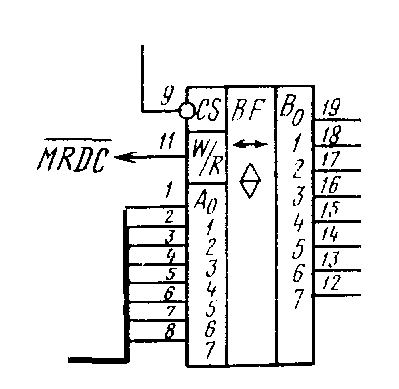

5.2 Шинный формирователь к580ва86

Сопряжение модулей микросхем, входящих в микропроцессорную систему, с шиной данных реализовано на микросхемах шинных формирователей К580ВА86.

Рисунок 31 - Шинный формирователь К580ВА86

Передача

информации обеспечивается при сигнале

с уровнем логического 0 на входе СS.

При наличии на входе СS

сигнала с уровнем логической 1 все выходы

переходят в третье состояние. Сигнал

![]() снимается с выхода ОЕ буферного регистра

КР580ИР82.

снимается с выхода ОЕ буферного регистра

КР580ИР82.

Направление

передачи информации зависит от

сигнала

![]() .

При

.

При![]() = 0 информация с выходов микросхем

поступает в шину данных, при

= 0 информация с выходов микросхем

поступает в шину данных, при

![]() =1

из шины данных на входы микросхем.

=1

из шины данных на входы микросхем.

5.3 Подключение микросхем, входящих в микропроцессорную систему, к

шинам адреса и данных

Подключение микросхем, входящих в микропроцессорную систему, к шинам адреса и данных посредством буферного регистра и шинного формирователя представим на примере подключения модуля ОЗУ.

Подключение модуля ОЗУ представлено на рисунке 32.

Рисунок 32- Подключение ОЗУ к шинам адреса и данных

5.4 Разработка структурной схемы

На основании анализа структурных схем устройств, входящих в разрабатываемую микропроцессорную систему, а также на основании выбранного способа подключения данных устройств к магистралям представим микропроцессорную систему в виде структурной схемы. На схеме каждое устройство представим в виде прямоугольника и обозначим соответствующие входы/выходы и сигналы, которые обеспечивают сопряжение и взаимосвязь всех микросхем, входящих в систему.

Структурная схема приведена в приложении А.

ЗАКЛЮЧЕНИЕ

В результате курсового проектирования в соответствии с заданным вариантом разработана микропроцессорная система на базе микроконтроллера К1816ВЕ48. На основании анализа функционирования данного микроконтроллера разработан процессорный модуль и интерфейс микропроцессорной системы.

В соответствии с техническим заданием разработана подсистема памяти на базе БИС ОЗУ К537РУ8 БИС ПЗУ К556РТ6.

Для обеспечения полноценного и бесперебойного функционирования микропроцессорной системы разработана подсистема ввода/вывода и прерываний.

На основании анализа структурных схем устройств, входящих в разрабатываемую микропроцессорную систему, а также на основании выбранного способа подключения данных устройств к магистралям составлена структурная схема микропроцессорной системы.

СПИСОК ИСПОЛЬЗУЕМОЙ ЛИТЕРАТУРЫ

-

Горбунов В.Л. Микропроцессоры. Основы построения микроЭВМ / В.Л.Горбунов, Д.И.Панфилов, Д.Л. Преснухин. – М.: Высшая школа, 1986.

-

Грицюк С.Н., Власов В.В. Методические указания к курсовому проектированию по дисциплине «Микропроцессорные устройства систем управления» / С.Н. Грицюк, В.В. Власов. – Саратов, 2006.

-

Каган Б.М. Основы проектирования микропроцессорных устройств автоматики / Б.М.Каган, В.В.Сташин. – М.: Энергоатомиздат, 1990.

-

Лебедев О.Н. Микросхемы памяти и их применение / О.Н. Лебедев. – М.: Радио и связь, 1990.

-

Новиков Ю.В., Скоробогатов П.К. Основы микропроцессорной техники / Ю.В. Новиков, П.К. Скоробогатов. – М.: ИНТУИТ.РУ, 2003.

-

Сташин В.В. Проектирование цифровых устройств на однокристальных микроконтроллерах / В.В.Сташин, А.В.Урусов, О.Ф.Мологонцева. – М.: Энергоатомиздат, 1990. – 224с.

-

Хвощ С.Т., Варлинский Н.Н. Микропроцессоры и микроЭВМ в системах автоматического управления: справочник / С.Т. Хвощ, Н.Н. Варлинский, Е.А. Попов. – Л.: - Машиностроение, 1987.

-

Щелкунов Н.Н., Дианов А.П. Микропроцессорные средства и системы / Н.Н. Щелкунов, А.П. Дианов. - М.: Радио и связь, 1989.

ПРИЛОЖЕНИЕ А

(обязательное)

Графическая часть

1 Структура микроконтроллера К1816ВЕ48 66

2 Структурная схема микропроцессорной системы 67