- •1 Анализ технического задания

- •2.2 Арифметическо-логическое устройство

- •2.3 Память микроконтроллера

- •2.4 Управление работой микроконтроллера

- •2.5 Организация ввода-вывода информации в микроконтроллере

- •3.2 Постоянное запоминающее устройство

- •4.3 Контроллер прямого доступа к памяти (кпдп)

- •4.4 Программируемый интервальный таймер (пит)

- •5.2 Шинный формирователь к580ва86

2.5 Организация ввода-вывода информации в микроконтроллере

Для

связи МК 1816 с объектом управления, для

ввода и вывода информации используются

27 линий. Эти линии сгруппированы в 3

порта по 8 линий в каждом и могут быть

использованы для вывода, ввода или для

ввода—вывода через двунаправленные

линии. Кроме портов ввода— вывода,

имеются 3 входные линии, сигналы на

которых могут изменять ход программы

по командам условного перехода: линия

![]() используется для ввода в МК сигнала

запроса прерывания от внешнего источника;

линия Т0 предназначена для ввода

тестирующего сигнала от двоичного

датчика объекта управления; кроме того,

под управлением программы (ENTO

CLC)

по этой линии из МК может выдаваться

сигнал синхронизации; линия Т1 используется

для ввода тестирующего сигнала или в

качестве входа счетчика событий (по

команде STRT

CNT).

используется для ввода в МК сигнала

запроса прерывания от внешнего источника;

линия Т0 предназначена для ввода

тестирующего сигнала от двоичного

датчика объекта управления; кроме того,

под управлением программы (ENTO

CLC)

по этой линии из МК может выдаваться

сигнал синхронизации; линия Т1 используется

для ввода тестирующего сигнала или в

качестве входа счетчика событий (по

команде STRT

CNT).

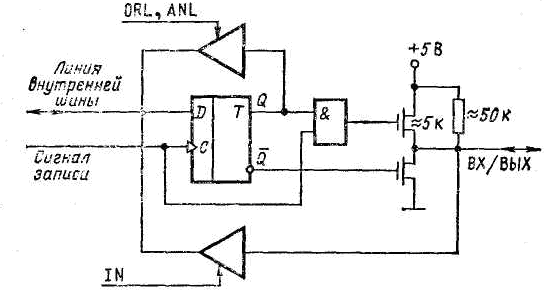

Порты ввода — вывода Р1 и Р2. Каждая линия портов Р1 и Р2 может быть программным путем настроена на ввод, вывод или на работу с двунаправленной линией передачи. Специальная схемотехника цепей вывода портов Р1 и Р2, которая получила название квазидвунаправленной структуры, позволяет выполнять ввод, вывод и двунаправленные передачи, несмотря на то, что выходы схем вывода статически заперты. Каждый контакт ввода - вывода портов Р1 и Р2 является выходом с открытым стоком и входом с высоким импедансом, соответствующим по логическому уровню сигналу 1. На рисунке 9 показана схема одной линии ввода — вывода. Линия постоянно подключена к источнику электропитания +5В через резистор большого сопротивления (50 КОм), обеспечивая для единичной стандартной ТТЛ-нагрузки достаточный входной ток, соответствующий логической 1. В то же время потенциал в линии может быть приближен к потенциалу земли (уровень логического 0) нулевым сигналом на выходе стандартной ТТЛ-схемы.

Рисунок 9 – Функциональная схема портов ввода – вывода Р1 и Р2

Именно это обстоятельство и позволяет использовать статически запертую схему вывода как для ввода, так и для вывода информации.

При передаче на выход из МК уровня 1 по сигналу ЗАПИСЬ для ускорения переходного процесса от 0 к 1 на короткое время (0,5 мкс) открывается верхний МОП-транзистор с относительно низким сопротивлением (5 КОм). При передаче в линию уровня 0 открытым оказывается нижний МОП-транзистор выходной схемы с сопротивлением 3 КОм. Это сопротивление достаточно малое для того, чтобы обеспечить отвод тока из входной цепи ТТЛ-нагрузки.

Для того, чтобы настроить некоторую линию на режим ввода в МК, необходимо перед этим в буферный D-триггер этой линии записать 1. При этом нижний МОП-транзистор выходной схемы окажется закрытым и это обеспечит ТТЛ-источнику вводимого сигнала высокоимпедансную нагрузку. Сигнал системного сброса СБРОС автоматически записывает во все линии портов Р1 и Р2 сигнал 1.

Квазидвунаправленная структура портов Р1 и Р2 специфична тем, что в процессе ввода информации выполняется операция логического И над вводимыми данными и текущими (последними выводимыми) данными. Для того, чтобы можно было осуществить ввод, необходимо следить за тем, чтобы в соответствующих линиях ввода сохранялось значение 1. Квазидвунаправленные буферные схемы портов Р1 и Р2 и команды логических операций ANL и ORL представляют эффективное средство маскирования для обработки однобитовых входов и выходов в МК.

В системе команд МК есть команды, которые позволяют выполнять запись нулей и единиц в любой разряд или группу разрядов порта. Но так как в этих командах маска задается непосредственным операндом, то необходимо знать распределение сбрасываемых и устанавливаемых линий на этапе разработки исходной программы. В том случае, если маска вычисляется программой и заранее не известна, то в ОЗУ необходимо иметь копию состояния порта вывода. Эта копия по командам логических операций соединяется с вычисляемой маской в аккумуляторе и затем загружается в порт. Необходимость этой процедуры вызвана тем, что квазинаправленная структура не позволяет выполнить операцию чтения состояний портов Р1 и Р2, зафиксированных по последней команде вывода.

Порт Р2 отличается от порта Р1 тем, что его младшие 4 бита могут быть использованы для расширения МК-системы по вводу - выводу. Через младшую тетраду порта Р2 по специальным командам с обращением к портам Р4—Р7 возможен доступ к четырем внешним четырехбитным портам ввода—вывода. Работа этих внешних портов синхронизируется сигналом ПРОГ/СТБВВ.

Порт BUS представляет собой двунаправленный буфер с тремя состояниями и предназначен для побайтного ввода, вывода или ввода—вывода информации.

Если порт BUS используется для двунаправленных передач, то обмен информацией через него выполняется по командам MOVX. При выводе байта генерируется стробирующий сигнал ЗП, а выводимый байт фиксируется в буферном регистре. При вводе байта генерируется стробирующий сигнал ЧТ, но вводимый байт в буферном регистре не фиксируется. В отсутствие передач порт BUS по своим выходам находится в высокоимпедансном состоянии.

Если порт BUS используется как однонаправленный, то вывод через него выполняется по команде OUTL, а ввод— по команде INS.

Вводимые и выводимые через порт BUS байты можно маскировать с помощью команд AND и OR, что позволяет выделять и обрабатывать в байте отдельный бит или группу бит. Для этого предварительно по команде OUTL BUS, A в порт BUS из аккумулятора должна быть загружена маска.

В МК-системах простой конфигурации, когда порт BUS не используется в качестве порта-расширителя системы, обмен выполняется по командам INS, OUTL и MOVX. Возможно попеременное использование команд OUTL и MOVX. Однако при этом необходимо помнить, что выводимый по команде OUTL байт фиксируется в буферном регистре порта BUS, а команда MOVX уничтожает содержимое буферного регистра порта.

В МК-системах, имеющих внешнюю память программ, порт BUS используется для выдачи адреса внешней памяти и для приема команды из внешней памяти программ. В таких системах использование команды OUTL BUS недопустимо, так как фиксация в буферном регистре порта BUS выводимого байта явится причиной неправильной выборки следующей команды.

В командах ввода—вывода информации имя порта, через который осуществляется передача, содержится в коде команды. Следовательно (из-за невозможности динамического определения имени порта в каком-либо рабочем регистре), отсутствует возможность использования одной программы управления идентичными устройствами, подключенными к разным портам. Это вынуждает программиста загружать в память программ две или более по существу (но не по кодам) одинаковых программ управления однотипными устройствами.

Однако динамический выбор идентичных устройств, а следовательно, и использование одной параметризуемой подпрограммы управления этими устройствами возможны в том случае, если обращение к внешним портам ввода— вывода выполнять по командам обращения к внешней памяти MOVX.

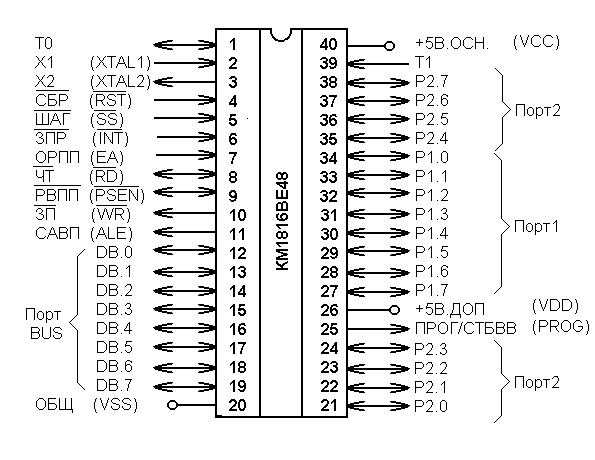

2.6 Цоколевка корпуса МК К1816ВЕ48

Цоколевка корпуса МК48 показана на рисунке 10.

Рисунок 10 - Цоколевка корпуса МК КМ1816ВЕ48

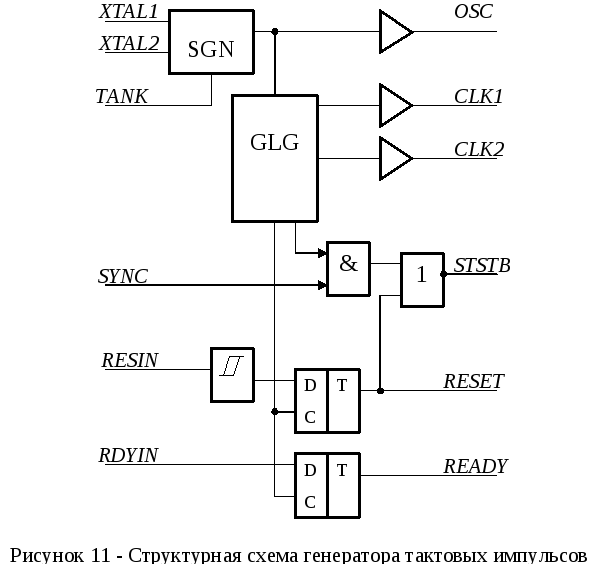

2.7 Генератор тактовых импульсов

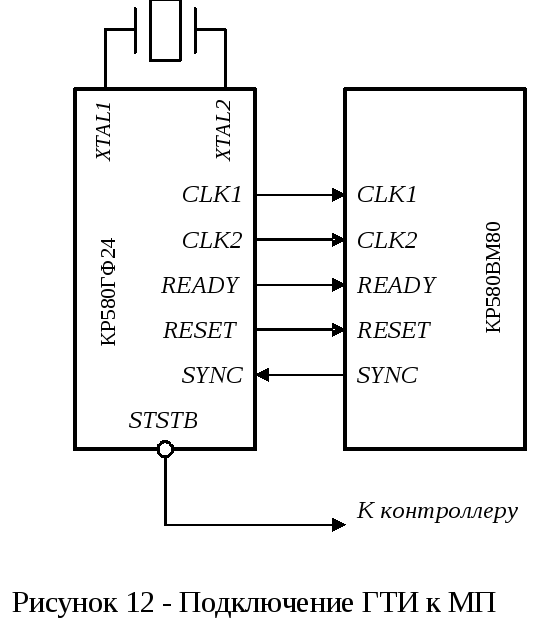

Генератор тактовых импульсов выполнен на микросхеме КР580ГФ24 и предназначен для синхронизации микропроцессорной системы. Генератор тактовых импульсов (ГТИ) формирует тактовые импульсы с частотой до 2,5 МГц и амплитудой 12В, а так же некоторые управляющие сигналы для микропроцессорной системы.

Структурная схема ГТИ представлена на рисунке 11, а подключение ГТИ к МП показано на рисунке 12. ГТИ состоит из задающего генератора, (SGN), генератора тактовых импульсов (GLG), порогового элемента, формирователей и логических схем. Для работы ГТИ необходимо подключение внешнего кварцевого резонатора с частотой в 9 раз большей, чем частота выходных тактовых импульсов ГТИ.

Основные временные характеристики тактовых импульсов следующие:

Время переднего и заднего фронтов (tLH, tHL), нс 0÷50

Ширина импульса CLK1 (tCLK1), нс ≥60

Ширина импульса CLK2 (tCLK2), нс ≥220

Временной интервал между задним фронтом

CLK1 и передним фронтом CLK2 (tD1), нс ≥0

Временной интервал между задним фронтом

CLK2 и передним фронтом CLK1 (tD2), нс ≥70

Задержка CLK2 по отношению к CLK1, tD3,нс ≥80

Основные электрические параметры микросхемы КР580ГФ24 следующие:

Входное напряжение L-уровня UIL, В 0,8

Входное напряжение H-уровня UIH, В 0,2

Напряжение RESIN, UIH-UIL, В 0,25

Выходное напряжение L-уровня UOL, В 0,45

Выходное напряжение H-уровня UOH, В:

на выходах CLK1, CLK2 9,4

на выходах READY, RESET 3,6

на всех других выходах 2,4

Ток источника питания ICC, мА 115

Н азначение

входных и выходных сигналов:

азначение

входных и выходных сигналов:

XTAL1, XTAL2 – входы для подключения кварцевого резонатора.

TANK – вход для подключения параллельного LC-контура.

SYNC – вход синхронизации.

RESIN – входной сигнал «СБРОС».

RDYIN – вход сигнала «ГОТОВ», для подачи сигналов о готовности внешних устройств к работе с МП.

OSC – выход генератора, используемый для тактирования периферийных устройств.

CLK1, CLK2 – выходы тактовых импульсов.

STSTB – строб состояния – сигнал L-уровня, используемый для фиксации слова состояния МП.

RESET – выходной сигнал «СБРОС».

READY– выходной сигнал «ГОТОВ».

П итание

генератора тактовых импульсов

осуществляется источником напряжения

+5В.

итание

генератора тактовых импульсов

осуществляется источником напряжения

+5В.

2.8 АЦП

Широкое распространение однобайтных процессоров вызвало разработку восьмиразрядных аналого-цифровых преобразователей. В разрабатываемой МПС применим АЦП типа К572ПВ3.

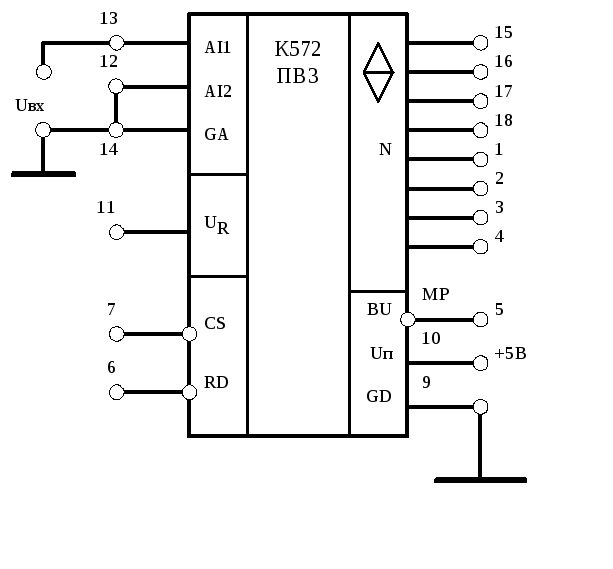

Схема подключения АЦП К572ПВ3 к МП показана на рисунке 13.

Рисунок 13 – Схема подключения АЦП К572ПВ3

Время преобразования этого АЦП равно 7,5 мкс, ток потребления от одного источника питания 5 В составляет всего лишь 5 мА. АЦП имеет два одинаковых входа AI1 и AI2, соединённых внутренними резисторами с одним входом компаратора.

Н а

этот же вход компаратора подаётся

выходной ток цифро-аналогового

преобразователя, управляемого регистром

последовательного приближения. Таким

образом, АЦП обеспечивает преобразование

в код суммы напряжений, подаваемых на

входы AI1 и AI2. При практическом использовании

этого АЦП на вход AI1 подают входное

напряжение Uвх, а на вход AI2 – напряжение,

с помощью которого производят регулировку

нуля АЦП. Управление работой АЦП К572ПВ3

осуществляется с помощью сигналов,

подаваемых на входы

а

этот же вход компаратора подаётся

выходной ток цифро-аналогового

преобразователя, управляемого регистром

последовательного приближения. Таким

образом, АЦП обеспечивает преобразование

в код суммы напряжений, подаваемых на

входы AI1 и AI2. При практическом использовании

этого АЦП на вход AI1 подают входное

напряжение Uвх, а на вход AI2 – напряжение,

с помощью которого производят регулировку

нуля АЦП. Управление работой АЦП К572ПВ3

осуществляется с помощью сигналов,

подаваемых на входы

![]() (выбор кристалла) и

(выбор кристалла) и

![]() (чтение). Переход 0/1 на входе

(чтение). Переход 0/1 на входе

![]() запускает схему сброса АЦП, потенциал

0 на входе

запускает схему сброса АЦП, потенциал

0 на входе

![]() осуществляет запуск преобразователя

при условии, что предварительно был

осуществлён его сброс. Таким образом,

если

осуществляет запуск преобразователя

при условии, что предварительно был

осуществлён его сброс. Таким образом,

если

![]() =0,

то переход 0/1 на входе

=0,

то переход 0/1 на входе

![]() обусловит

сброс и запуск преобразователя. Если

же

обусловит

сброс и запуск преобразователя. Если

же

![]() =1,

то этот переход вызывает только сброс,

а запуск произойдет по спаду 1/0 на входе

=1,

то этот переход вызывает только сброс,

а запуск произойдет по спаду 1/0 на входе

![]() .

Выход BU (АЦП занят) принимает потенциал

«нуль» тогда, когда осуществляется

процесс преобразования. Данные на

кодовом выходе N существуют при сочетании

сигналов

.

Выход BU (АЦП занят) принимает потенциал

«нуль» тогда, когда осуществляется

процесс преобразования. Данные на

кодовом выходе N существуют при сочетании

сигналов

![]() =0,

=0,

![]() =0,

=0,

![]() =1,

если же этого сочетания нет, если же

этого сочетания нет, то выход находится

в высокоимпендансном состоянии.

=1,

если же этого сочетания нет, если же

этого сочетания нет, то выход находится

в высокоимпендансном состоянии.

3 РАЗРАБОТКА ПОДСИСТЕМЫ ПАМЯТИ

3.1 Оперативное запоминающее устройство

Оперативные ЗУ предназначены для хранения переменной информации и имеют практически одинаковое быстродействие при считывании и записи.

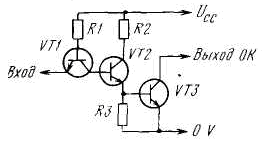

Микросхемы серии К134РУ6, относится к типу асинхронных статических ОЗУ, емкостью 1КХ 1 бит, получена по ИИЛ-ТТЛ-технологии. Ее особенность заключается в том, что выход построен по схеме с открытым коллектором (рисунок 14).

Рисунок 14 – Функциональный элемент микросхемы ОЗУ на биполярных

транзисторах: инвертор с открытом коллекторным выходом.

Наличие такого выхода не позволяет объединять информационные входы и выходы. При соединении нескольких микросхем по выходам можно использовать схему «монтажного ИЛИ» с подключением к точке соединения источника питания через внешний токоограничивающий резистор. При хранении потребляемая мощность снижается вдвое.

Электрические параметры микросхем памяти разделяют на статические и динамические.

Электрические статические параметры К537РУ8:

Напряжение

питания

![]() ,В

5

,В

5

Напряжение выходное:

-

высокого уровня

![]() ,

В

5

,

В

5

-

низкого уровня

![]() ,

В

0,01

,

В

0,01

Напряжение

![]() ,

В

2,5

,

В

2,5

Динамические параметры микросхемы К134РУ6:

Время

цикла записи/чтения

![]() ,

нс 1000

,

нс 1000

Время

выбора

![]() ,

нс

200

,

нс

200

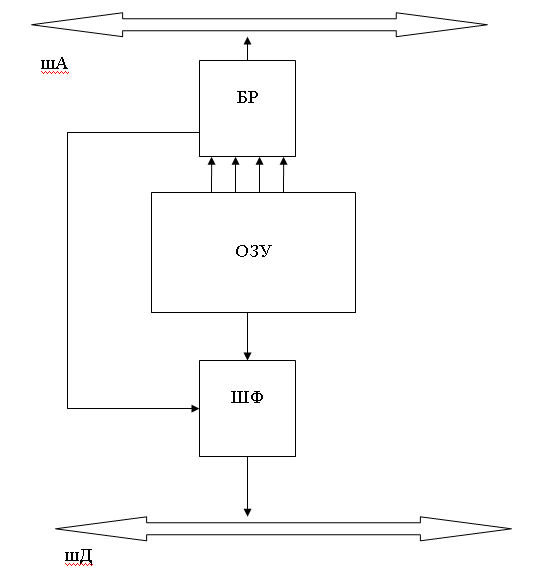

Подробная схема подключения ОЗУ к шинам адреса и данных посредством буферного регистра и шинного формирователя будет представлена в пункте разработки уточненной схемы микропроцессорной системы, сигналы и выходы, с помощью которых производится подключение микросхемы будут указаны в пункте подбора буферного регистра и шинного формирователя.

Рисунок 19 – Подключение ОЗУ к шинам данных и адреса