- •1.Организация микроконтроллера мк1816

- •1.1.Общие сведения о семействе микроконтролеров к1816.

- •2.Арифметическо-логическое устройство (алу) микроконтроллера мк1816

- •3.Память микроконтроллера мк1816

- •3.1.Память программ (или - память команд, пк)

- •3.2.Память данных (или - оперативная память, озу)

- •4.Организация ввода – вывода в микроконтроллере мк1816

- •4.1.Порты (или каналы) ввода - вывода р1 и р2.

- •4.2.Порт ввода - вывода bus (или db).

- •5.Управление работой микроконтроллера мк1816

- •5.1.Синхронизация микроконтроллера.

- •5.2.Системный сброс.

- •5.3.Пошаговый режим работы.

- •6.Варианты структур микроконтроллерных систем(мкс) на основе мк1816

- •6.1.Мк-система с расширенной памятью программ.

- •6.2.Мк-система с расширенной памятью данных.

- •6.3.Мк-система с расширенным вводом-выводом.

- •7.Система команд микроконтроллера мк1816

- •7.1.Команды пересылки и обмена

- •7.2.Команды арифметических и логических операций (в том числе и операций над признаками)

- •7.2.1.Общие сведения.

- •7.2.2.Команды группы арифметических операций

- •7.2.3.Команды группы логических операций:

- •Xrl a,Rr - Исключающее или аккумулятора с маской в регистре

- •Xrl a,#d - Исключающее или аккумулятора с непосредственным операндом

- •Xrl a,@Rr - Исключающее или аккумулятора и маской в ячейке памяти

- •7.3.Команды ввода – вывода

- •7.4.Команды передачи управления (в том числе и операций с подпрограммами)

- •7.5.Команды операций с таймером

- •7.6.Команды управления режимом работы мк

6.1.Мк-система с расширенной памятью программ.

Следующий рисунок иллюстрирует процесс выборки команды из внешней памяти:

В процессе выборки команды выполняются следующие шаги:

содержимое счетчика команд выводится через порт BUS и младшую тетраду порта Р2;

по заднему фронту сигнала САВП на внешнем регистре фиксируется адрес;

сигналом РВП разрешается работа внешней памяти;

по окончании сигнала РВП шина BUS переходит в режим ввода.

Шина BUS (DB) MK K1816 подобна двунаправленной шине данных МП K580, и все расширения МК выполняются с использованием этой шины. При обращении к резидентной памяти программ МК не генерирует внешних управляющих сигналов (за исключением САВП, который всегда идентифицирует каждый машинный цикл). Начиная с адреса 1024, МК 1816 автоматически формирует управляющие сигналы, обеспечивающие выборку команд из внешней памяти.

Ячейки памяти с адресами, лежащими за пределами блока памяти 0, могут быть доступны по команде переключения блоков памяти "SEL MB1", за которой должна следовать команда перехода (JMP или CALL), так как СК11 не изменяет своего состояния под воздействием команды "SEL MB", а загружается из специального триггера признака блока памяти по очередной команде перехода. Это предохраняет пользователя от неумышленного пересечения границы 2К, но влечет за собой следующую особенность: так как все 12 разрядов СК сохраняются в стеке при вызове подпрограмм, то переход к подпрограмме можно выполнять с пересечением границы 2К, а номер блока памяти будет восстановлен при возврате из подпрограммы. При этом, однако, триггер признака блока памяти не будет изменен по возврату и очередная команда перехода, если ей не предшествует команда "SEL MB", может исказить вычислительный процесс. Все эти особенности работы счетчика команд проиллюстрированы на рисунке выше.

На рисунке ниже показана структура МК-системы с расширенной памятью программ (ПЗУ).

Три дополнительных БИС памяти емкостью по 1 Кбайт подключаются к шине BUS своими информационными входами. Младший байт адреса по сигналу САВП фиксируется на внешнем буферном регистре. Старшая тетрада адреса, выводимая через порт Р2, не нуждается в буферизации, так как она фиксирована в порте Р2 и стабильна на протяжении цикла выборки. Два самых старших бита адреса заводятся на внешний дешифратор (стробируемый сигналом РВП*) для селекции требуемой БИС памяти программ.

6.2.Мк-система с расширенной памятью данных.

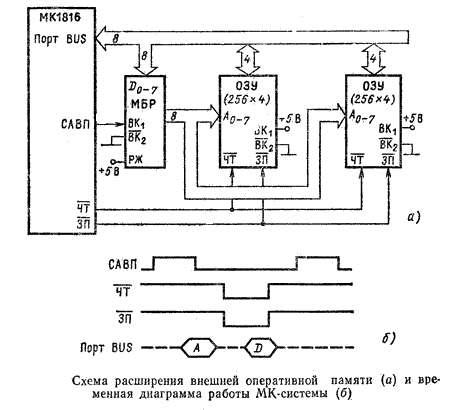

На рисунке ниже показана схема МК-системы, в состав которой включены две дополнительные БИС ОЗУ емкостью 256 байт (256 x 4).

Внешняя оперативная память доступна МК по командам пересылки "MOVX A,@R" и "MOVX @R,А", которые по косвенному адресу (регистр R0 или R1) выполняют передачу байта между внешним ОЗУ и аккумулятором. Сигналом САВП косвенный адрес, выводимый по шине BUS, фиксируется в МБР. Сигналы ЗП* и ЧТ* определяют режим работы БИС ОЗУ. Так как косвенный адрес имеет формат байта, то схема на рисунке выше обеспечивает адресацию 256 ячеек ОЗУ в дополнение к 64 ячейкам резидентного ОЗУ микроконтроллера.

При необходимости дальнейшего наращивания объема внешнего ОЗУ можно реализовать механизм перелистывания страниц памяти через дополнительные линии порта Р2.