- •1.Организация микроконтроллера мк1816

- •1.1.Общие сведения о семействе микроконтролеров к1816.

- •2.Арифметическо-логическое устройство (алу) микроконтроллера мк1816

- •3.Память микроконтроллера мк1816

- •3.1.Память программ (или - память команд, пк)

- •3.2.Память данных (или - оперативная память, озу)

- •4.Организация ввода – вывода в микроконтроллере мк1816

- •4.1.Порты (или каналы) ввода - вывода р1 и р2.

- •4.2.Порт ввода - вывода bus (или db).

- •5.Управление работой микроконтроллера мк1816

- •5.1.Синхронизация микроконтроллера.

- •5.2.Системный сброс.

- •5.3.Пошаговый режим работы.

- •6.Варианты структур микроконтроллерных систем(мкс) на основе мк1816

- •6.1.Мк-система с расширенной памятью программ.

- •6.2.Мк-система с расширенной памятью данных.

- •6.3.Мк-система с расширенным вводом-выводом.

- •7.Система команд микроконтроллера мк1816

- •7.1.Команды пересылки и обмена

- •7.2.Команды арифметических и логических операций (в том числе и операций над признаками)

- •7.2.1.Общие сведения.

- •7.2.2.Команды группы арифметических операций

- •7.2.3.Команды группы логических операций:

- •Xrl a,Rr - Исключающее или аккумулятора с маской в регистре

- •Xrl a,#d - Исключающее или аккумулятора с непосредственным операндом

- •Xrl a,@Rr - Исключающее или аккумулятора и маской в ячейке памяти

- •7.3.Команды ввода – вывода

- •7.4.Команды передачи управления (в том числе и операций с подпрограммами)

- •7.5.Команды операций с таймером

- •7.6.Команды управления режимом работы мк

4.Организация ввода – вывода в микроконтроллере мк1816

Для связи МК 1816 с объектом управления, для ввода и вывода информации используется 27 линий. Эти линии сгруппированы в 3 порта по 8 линий в каждом и могут быть использованы для вывода, ввода или для вывода - ввода через двунаправленные линии. Кроме портов ввода - вывода, имеются 3 входные линии, сигналы на которых могут изменять ход программы, а именно:

линия ЗПР* используется для ввода в МК сигнала запроса прерывания от внешнего источника;

линия Т0 предназначена для ввода тестирующего сигнала от двоичного датчика объекта управления.

Кроме того, под управлением программы (ENT0 CLC - команда "разрешение выдачи сигнала синхронизации") по этой линии из МК может выдаваться сигнал синхронизации;

линия Т1 используется для ввода тестирующего сигнала или в качестве входа счетчика событий (по команде STRT CNT - "запуск счетчика событий").

4.1.Порты (или каналы) ввода - вывода р1 и р2.

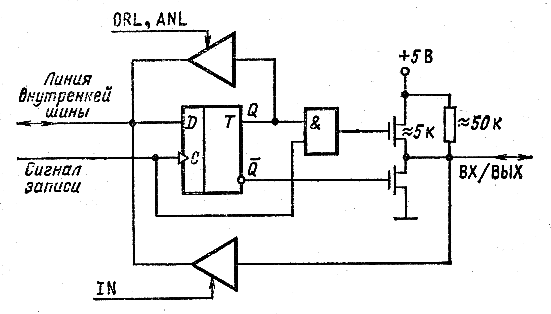

Каждая линия портов Р1 и Р2 может быть программным путем настроена на ввод, вывод или на работу с двунаправленной линией передачи. Специальная схемотехника цепей вывода портов Р1 и Р2, обеспечивающая квазидвунаправленную работу портов, несмотря на то, что выходы схем вывода статически заперты. На нижеследующем рисунке представлена схема одной линии (одного разряда) порта.

Каждый контакт ввода - вывода портов Р1 и Р2 является выходом с открытым стоком и входом с высоким импедансом, соответствующим по логическому уровню сигналу 1. Линия постоянно подключена к источнику электропитания +5 В через резистор большого сопротивления (50 КОм), чем обеспечивается для единичной стандартной ТТЛ-нагрузки достаточный ток, соответствующий логической 1. В то же время потенциал в линии может быть приближен к потенциалу "земли" (уровень логического 0) нулевым сигналом на выходе стандартной ТТЛ-схемы. Чем и обеспечивается возможность использовать статически запертую схему вывода как для ввода, так и для вывода информации.

При передаче на выход из МК уровня 1 по сигналу ЗАПИСЬ для ускорения переходного процесса от 0 к 1 на короткое время (0,5 мкс) открывается верхний МОП-транзистор с относительно низким сопротивлением (5 КОм). При передаче в линию уровня 0 открытым оказывается нижний МОП-транзистор выходной схемы с сопротивлением 3 КОм. Это сопротивление достаточно малое для того, чтобы обеспечить отвод тока из входной цепи ТТЛ-нагрузки.

Для того, чтобы настроить некоторую линию на режим ввода в МК, необходимо перед этим в буферный D-триггер этой линии записать 1. При этом нижний МОП-транзистор выходной схемы окажется закрытым и это обеспечит ТТЛ-источнику вводимого сигнала высокоимпедансную нагрузку. Сигнал системного сброса СБРОС* автоматически записывает во все линии портов Р1 и Р2 сигнал 1.

Квазидвунаправленная структура портов Р1 и Р2 для программиста МК 1816 специфична тем, что в процессе ввода информации выполняется операция логического И над вводимыми данными и текущими (последними выводимыми) данными. Для того, чтобы можно было осуществить ввод, программист должен следить за тем, чтобы в соответствующих линиях ввода сохранялось значение 1. Квазидвунаправленные буферные схемы портов Р1 и Р2 и команды логических операций ANL (логическое И аккумулятора с маской в регистре) и ORL (логическое ИЛИ аккумулятора с непосредственным операндом или с маской в регистре или в ячейке памяти) представляют программисту эффективное средство маскирования для обработки однобитовых входов и выходов в МК.