- •Введение

- •Xseg Пространство внешней памяти;

- •2.1.7 Система прерываний. Упрощенная схема прерываний мк51 приведена на рисунке 6.

- •2.2.5 Работа с портами. Порты р1 - р3 имеют идентичные характеристики. Данные, записанные в них, статически фиксируются и не изменяются до перезаписи.

- •2.3 Упрощенная структурная схема разрабатываемой микропроцессорной системы

- •3.2 Описание микросхемы бис пзу к541ре1

- •3.3 Подключение озу и пзу к системной шине

- •4.3 Контроллер прямого доступа к памяти кр580вт57

- •4.4 Многорежимный буферный регистр к589ир12

- •4.5.3 Режимы работы клавиатуры.

- •4.6 Уточненная схема управляющей микроЭвм

- •5.2 Разработка блок-схемы управляющей системы

- •6 Реализация устройства на базе микропроцессора

- •6.2 Устройство

-

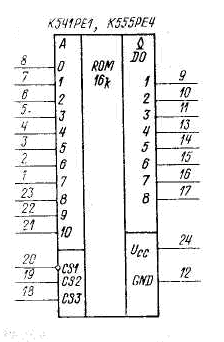

3.2 Описание микросхемы бис пзу к541ре1

Масочные ПЗУ серии К541. Микросхема ПЗУ типа 541РЕ1 представляет собой постоянное ЗУ с емкостью 16 384 бит для хранения и считывания информации в объеме 2048 8-разрядных слов.

Входные и выходные уровни напряжений совместимы с ТТЛ ИС. Микросхема К541РЕ1 имеет выходы с открытым коллектором. Программирование ПЗУ осуществляется с помощью фотошаблона технологического слоя «диэлектрик». Накопитель представляет собой набор диэлектрических окон с развязывающими элементами. Наличие и отсутствие этих окон определяют хранимую информацию в накопителе.

Условное обозначение и назначение выводов приведены на рисунке 12.

Микросхемы серии имеют напряжение питания 5 В, ТТЛ входные и выходные уровни, выход на три состояния, характеризуются сравнительно высоким уровнем энергопотребления, по сравнению с микросхемами серии К132, причем не обладают свойством снижать уровень потребляемой мощности и режиме хранения.

Рисунок 12 – Условное обозначение БИС ПЗУ К541РЕ1

Основные электрические параметры БИС К541РЕ1 в диапазоне температур от -10 до +70°С при Uсс = (5±0,5) В:

Ток потребления в статическом режиме Icc, мА ≤ 100;

Выходное напряжение низкого уровня UOL при IOL= 8 мА, В ≤ 0.45;

Ток утечки на выходе IOH, мкА ≤ 40;

Входное напряжение низкого уровня UIL при IIL = 0.4 мА, В ≤ 0,5;

Входное напряжение высокого уровня UIH при IIH = 40 мкА, В ≥2,4;

Время выбора адреса tAA, не ≥100;

» выборки разрешения tCS, не > 70;

» восстановления tOFF, не ≤ 70;

» цикла tC, не > 150;

Входная емкость С1, пФ < 3;

Выходная емкость Со, пФ < 6;

Емкость нагрузки CL, пФ < 200.

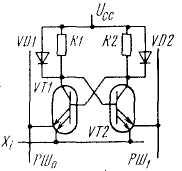

Рисунок 13 – Функциональные элементы микросхем статических ОЗУ на

биполярных транзисторах, элемент памяти ТТЛ

Структура микросхем содержит все функциональные узлы типичного варианта ее построении рисунок 13. В качестве элемента памяти использован статический триггер на четырех транзисторах, два из которых, VT3 и VТ4, являются инжекторами транзисторов VT2 и VT1 соответственно. Двухэмиттерными транзисторами управляют сигналы адресной шины Xi и разрядных шин РШо, РШ1. При Хi=0 триггер находится в режиме хранения, так как при этом фиксируется состояние плеч триггера. При Xi = 1 оба эмиттерных перехода, подключенных к адресной шине, закрываются, и состояние триггера зависит от потенциалов разрядных шин: при низком потенциале шин в режиме считывания в одну из них потечет ток, а именно в ту, со стороны которой транзистор открыт; в другой тока не будет.

При записи но шинам в форме парафазного сигнала РШ1=D, РШо=D к плечам триггера подводится информации. Асимметрия и потенциалах шин вызовет переключение триггер в состояние, определяемое потенциалами шин: например, при РШ1=O, РШо=1 (запись 0) откроется VT2, через него в шипу потечет ток инжектора VT4, а транзистор' VT1 закроется. При записи .1 состояния транзисторов изменятся па обратные.

Выходные и входные цепи выполнены па элементах ТТЛ, поскольку низкопороговые функциональные узлы ИИЛ имеют низкую помехоустойчивость и, кроме того, не согласованы по уровням напряжения с элементами других типов логики.