- •Введение

- •Xseg Пространство внешней памяти;

- •2.1.7 Система прерываний. Упрощенная схема прерываний мк51 приведена на рисунке 6.

- •2.2.5 Работа с портами. Порты р1 - р3 имеют идентичные характеристики. Данные, записанные в них, статически фиксируются и не изменяются до перезаписи.

- •2.3 Упрощенная структурная схема разрабатываемой микропроцессорной системы

- •3.2 Описание микросхемы бис пзу к541ре1

- •3.3 Подключение озу и пзу к системной шине

- •4.3 Контроллер прямого доступа к памяти кр580вт57

- •4.4 Многорежимный буферный регистр к589ир12

- •4.5.3 Режимы работы клавиатуры.

- •4.6 Уточненная схема управляющей микроЭвм

- •5.2 Разработка блок-схемы управляющей системы

- •6 Реализация устройства на базе микропроцессора

- •6.2 Устройство

2.2.5 Работа с портами. Порты р1 - р3 имеют идентичные характеристики. Данные, записанные в них, статически фиксируются и не изменяются до перезаписи.

В режиме работы с внешней памятью программ порт Р2 служит для выдачи сигналов старших разрядов адреса и статически фиксирует его до момента изменения. В этом режиме порт Р2 для расширения ввода-вывода не используется.

Для использования портов Р1 - Р3 в качестве входов ОМЭВМ по команде выдачи данных должна выдать напряжение высокого уровня Uoh по соответствующим линиям Р2, Р1, Р3, однако после подачи сигнала сброс порты Р1 - Р3 устанавливаются в состояние готовности приема без дополнительных усилий.

Порт Р0 - 8-ми разрядный двунаправленный порт с тремя состояниями, может использоваться в качестве статически фиксирующего выходного порта и нефиксирующего входного порта. Информация, выдаваемая портом Р0 с помощью команд выдачи, сопровождается строб - импульсом WR. При записи информации в порт Р0 с помощью команд приема вырабатывается строб-импульс RD.

Кроме операций ввода-вывода информации, предусмотрена возможность выполнения логических операций И, ИЛИ и исключающее ИЛИ непосредственно на фиксаторах портов Р0 - Р3.

В режиме работы с внешней памятью программ порт Р0 служит для выдачи младших разрядов адреса памяти программ, приема кодов команд, а также для выдачи адреса внешнего ОЗУ данных и приема-выдачи данных обмена с внешним ОЗУ, если оно используется.

При выполнении инструкции, которая разрешает чтение порта, новая информация поступает на внутреннюю магистраль ОМЭВМ во время последнего цикла инструкции. На выходе порта новые данные могут появиться до начала следующего цикла.

Имеются два способа считывания из портов: система команд ОМЭВМ позволяет считывать информацию с фиксатора порта или непосредственно с выхода в зависимости от кода инструкции.

Последовательный порт ОМЭВМ используется как для расширения ввода/вывода, так и в качестве универсального асинхронного приемо-передатчика (УАПП) с фиксированной или переменной скоростью последовательного обмена. Предусмотрена также возможность дуплексного включения.

При проектировании системы необходимо учитывать, что в состав МК51 уже включены программируемый системный таймер, порты последовательного и параллельного ввода-вывода, система прерываний.

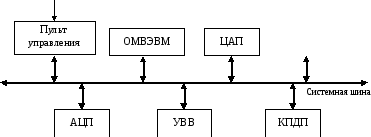

2.3 Упрощенная структурная схема разрабатываемой микропроцессорной системы

Упрощенная структурная схема микро - ЭВМ представлена на рисунке 8.

Все модули разрабатываемой системы объединяются общей системной шиной, состоящей из шин адреса, данных и управления. Обмен данными по магистрали осуществляется в адресном пространстве, разделенном с помощью управляющих сигналов обращения к запоминающему устройству и внешним устройствам.

О

K

Память

Y4

ПЗУ

ОЗУ

Сигналы с датчиков

Рисунок 8 – Упрощенная схема микропроцессорной системы

Хранение информации происходит в модуле памяти, состоящей и блока ПЗУ, выполненной на МС КР537РУ8, отвечающая за хранение программ и констант, и блока ОЗУ, реализованной на МС КР556РТ6, служащей для хранения входных и выходных данных, а также промежуточных результатов.

Осуществление операции преобразования аналоговых сигналов в цифровую форму и обратно происходит при помощи АЦП и ЦАП, реализованные на МС К1113ПВ1 и МС К572ПА1 соответственно.

Устройства ввода для связи с ОУ обеспечивают ввод в ОМВЭВМ значений x1, x2, x3, двоичных датчиков, а также 8 – разрядных двоичных кодов NU1, NU2, NU3, принимаемых с выходов АЦП.

Устройства вывода на ОУ обеспечивают выдачу двоичных управляющих воздействий y1, y2, y3 определенной длительности и кода управляющего напряжения Y4 - 8 – разрядного двоичного вектора на вход ЦАП.

В качестве контроллера прямого доступа к памяти КПДП, принимающего массив данных из ПЗУ (ОЗУ) в режиме ПДП использована МС КР580ВТ57.

Устройства ввода-вывода (УВВ) обеспечивают ввод управляющих сигналов, и вывод результатов значений x1, x2, x3, y1, y2, y3. NU1,Y4 на дисплей.

Пульт управления обеспечивает ввод в систему значения 8 – разрядной двоичной константы К, ввод двоичного значения сигнала «СТОП», формирование сигнала начальной установки системы.

3 РАЗРАБОТКА ПОДСИСТЕМЫ ПАМЯТИ

Подсистема памяти разрабатываемой системы включает в себя модуль ОЗУ и модуль ПЗУ, доступ к которым осуществляется по системной магистрали.

3.1 Описание микросхемы КР537РУ8

Оперативные ЗУ предназначены для хранения переменной информации и имеют практически одинаковое быстродействие при считывании и записи. МС статической ОЗУ КР537РУ8 характеризуется: по технологии изготовления – КМДП, по режиму доступа – Т, емкость составляет 2Кх8 бит.

Основные электрические параметры.

Напряжение питания UCC, B 4,75 - 5,25.

Ток потребления динамический ICCAV, мА менее 20.

Ток потребления хранения ICCS, мкА менее 1000.

Ток потребления в режиме хранения от

резервного источника питания ICCB, мкА менее 200.

Выходное напряжение высокого уровня UOH, В более 2,4.

Высокое напряжение низкого уровня UOL, В менее 0,4.

Ток утечки на входе ILI, мкА менее 5.

Ток утечки на выходе ILO, мкА менее 5.

Выходной ток низкого уровня IOL, мА менее 2.

Входная емкость С1, пФ менее 8.

Выходная емкость С0, пФ менее 10.

Предельная емкость нагрузки, пФ менее 1000.

Время цикла считывания (записи) tCR(CW), нс более 300. Время выборки разрешения tAС, нс 270.

Длительность сигнала CS tCS, нс 220.

Длительность сигнала WE tW, нс 80 – 120.

Время сдвига CS относительно адреса tCSA, нс более 50.

Время сдвига WE относительно DI tWS, нс более 20.

Время сдвига CS относительно WE tCSW, нс более 20.

Время сохранения адреса после CS tCHA , нс более 60.

Время сохранения WE после CS tCHW, нс более 30.

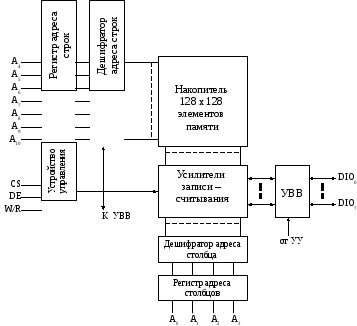

Структуру МС КР537РУ8 рассмотрим на рисунке 9.

Рисунок 9 - Структура микросхемы КР537РУ8

Организация одноразрядная и словарная с числом разрядов в слове четыре, восемь и шестнадцать. Для КМДП - микросхем характерен самый низкий уровень потребляемой мощности. Многие из них способны сохранять записанную информацию при пониженном до 2-3 В напряжении питания, что позволяет реализовать энергонезависимые ОЗУ с встроенным низковольтным источником питания.

Данная МС содержит матрицу запоминающих элементов 2048*8, представляющую собой накопитель ёмкостью 16384 бит (16 Кбит), дешифраторы адреса строк (DCK) и столбцов (DCS), блок управления СИ, адресные и выходные формирователи и разрядные усилители записи-считывания. Режим работы устанавливается с помощью сигналов CS1, CS2, W/R.

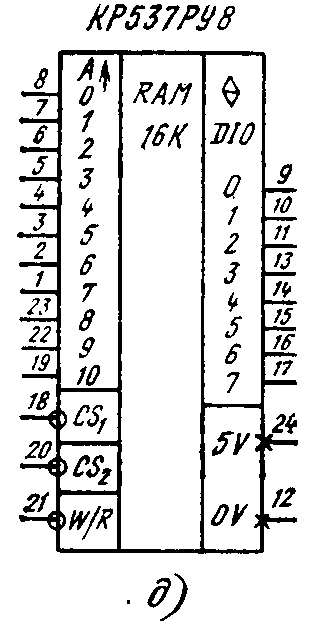

О бозначение

выводов

МС КР537РУ8

представлено на рисунке 10, назначение

выводов микросхемы –

в таблице 2.

бозначение

выводов

МС КР537РУ8

представлено на рисунке 10, назначение

выводов микросхемы –

в таблице 2.

Рисунок 10 - Цоколевка микросхемы КР537РУ8

Таблица 2 - Назначение выводов микросхемы КР537РУ8

|

Номера контактов |

Обозначение

|

Назначение |

Тип сигнала |

Состояние |

|

1-8 |

А0 - А7 |

Порты адреса |

вх |

1, 0, z |

|

9 - 11, 13 - 17 |

D0 - D7 |

Входы-выходы порта D |

вх/вых |

1, 0, z |

|

12 |

OV |

"Земля" (Общий вывод И.П.) |

|

|

|

18 |

CS1 |

Сигнал выбора микросхемы 1 |

вх |

0 |

|

19 |

A10 |

Порты адреса |

вх/вых |

1, 0, z |

|

20 |

CS2 |

Сигнал выбора микросхемы 2 |

вх |

0 |

|

21 |

W/R |

Сигнал записи |

вых |

0 |

|

22-23 |

A8, A9 |

Порты адреса |

вх |

1, 0, z |

|

24 |

5 V |

Питание + 5В |

|

|

МС КР537РУ8 имеет встроенные входные регистры - «защелки», срабатывающие от перепада сигнала CS. Наличие входных регистров придает МС ряд особенностей, прежде всего в режимах управления.

Истинность представленной МС рассмотрена в таблице 3.

Таблица 3 – Истинность микросхемы КР537РУ8

|

CS1vCS2 |

WR/RD |

А0…А10 |

DIO0…DIO7 |

Режим работы |

|

1 |

Х |

X |

Z |

Хранение |

|

0 |

0 |

А |

D0…D7 |

Запись |

|

0 |

1 |

А |

D0…D7 |

Считывание |

Статический режим КР537РУ8 характеризуется напряжением питания 5 В, близкими значениями уровней выходных сигналов, сравнительно небольшими выходными токами, наличием выходов с тремя состояниями, значительной предельной емкостью нагрузки.

Большой недостаток оперативной памяти состоит в том, что информация, записанная в нее, исчезает при выключении источника питания. Поэтому часто используется дополнительный источник питания, который питает при выключении источника питания только микросхемы памяти. МС КР537РУ8, является энергонезависимой оперативной памятью, содержимое которой может легко перезаписываться, но не пропадает при выключении питания, как в ПЗУ.

Схема энергонезависимой памяти (рисунок 11) довольно проста, хотя и имеет ряд неочевидных особенностей.

Рисунок 11 - Энергонезависимая оперативная память

Управляющие сигналы памяти – WR и – CS имеют активный низкий уровень, а при выключении питания все входные сигналы памяти, естественно, станут нулевыми. Это приведет к искажению записанной в память информации. Поэтому необходимо обеспечить, чтобы при выключении питания сигналы на входах –WR и –CS были пассивными, то есть имели уровень логической единицы. Для этого обычно используются логические элементы с выходами ОК, нагрузочные резисторы которых присоединяются не к пропадающему напряжению питания памяти Uип, а к сохраняющемуся напряжению питания памяти Uпам. Для получения напряжения Uпам используется простая схема на двух диодах, которая передает на выход Uпам напряжение источника питания Uип (если питание включено) или напряжение от гальванической батареи 3 – 4,5 В (если питание выключено).

Для большей гарантии от пропадания информации во время переходных процессов (при постепенном нарастании Uип и при постепенном его уменьшении) необходимо управлять прохождением сигналов WR и CS на память с помощью управляющего сигнала "Сброс". Этот сигнал равен нулю при напряжения Uип менее 4,7– 4,8 В и равен единице при нормальном напряжении Uип = 5 В (временная диаграмма приведена на рисунке). В результате такого решения память отключается от остальной схемы при недостаточном напряжении питания (сигналы -WR и –CS равны единице) и подключается к остальной схеме при нормальном напряжении питания.