- •Введение

- •1 Анализ технического задания

- •2 Разработка процессорного модуля и интерфейса

- •2.1 Анализ структуры цп к1816ве51

- •2.2 Система команд к1816ве51

- •3 Выбор модулей памяти

- •3.1 Выбор оперативно запоминающего устройства

- •3.2 Выбор постоянно запоминающего устройства

- •4 Разработка подсистем ввода/вывода, прерываний, прямого доступа к памяти. Выбор таймера

- •4.1 Архитектура параллельного интерфейса кр580вв55

- •4.2 Архитектура программируемого контролера прерываний кр580вн59

- •4.3 Архитектура программируемого таймера кр580ви53

- •4.5 Архитектура контролера прямого доступа к памяти кр580вт57

- •5 Разработка интерфейса и уточненной структурной схемы микропроцессорной системы

- •5.1 Буферный регистр кр580ир83

- •5.2 Шинный формирователь кр580ва87

- •5.3 Подключение микросхем, входящих в мпс к шинам данных и шинам адреса

- •5.4 Разработка структурной схемы мпс

- •6 Разработка программного обеспечения

- •Заключение

- •Список используемых источников

- •Приложение а

3 Выбор модулей памяти

3.1 Выбор оперативно запоминающего устройства

Для данной МПС в качестве оперативно запоминающего устройства будем использовать статическое ОЗУ К565РУ6. Микросхемы серии К565 представляют собой оперативные запоминающие устройства с произвольной выборкой динамического типа, изготавливаются по n– канальной МОП – технологии с кремниевыми затворами и двумя типами транзисторов (с индивидуальным и встроенным каналом) и предназначены для построения накопителей ОЗУ большой емкости.

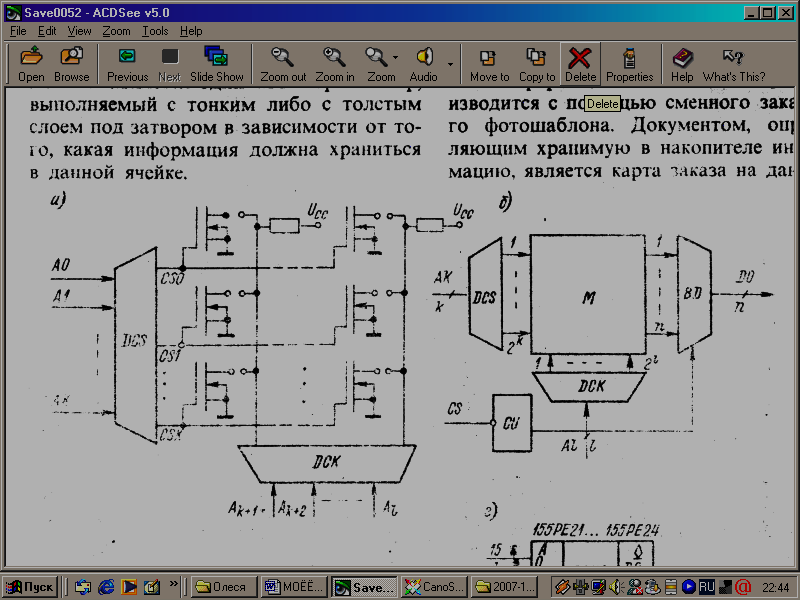

В ПЗУ запоминающие элементы объединяются в двухкоординатную матрицу, образованную при пересечении совокупности входных (чисел) и выходных (разрядов) информационных шин. В местах пересечения шин могут быть включены диоды, биполярные транзисторы и МОП – транзисторы. Запоминающим элементом накопителя ПЗУ является один МОП – транзистор, выполняемый с тонким либо с толстым слоем под затвором в зависимости от того, какая информация должна храниться в данной ячейке.

Рисунок 7 – Организация масочного ПЗУ (а) и обобщенная логическая __структура (б) КР565РУ6

Рисунок 8 – Цоколевка корпуса КР565РУ6

А0 – А6 - входы адреса;

RAS– сигнал выбора адреса строк;

CAS- сигнал выбора адреса столбца;

WE– сигнал записи/чтения;

D0 - используются для считывания информации;

DI- используются для записи информации;

Ucc– напряжение питания.

Регенерация информации в динамических ячейках памяти осуществляется за 128 циклов путем обращения к каждой из 128 строк не ранее, чем через каждые 2 мс перебором адресов А(0-6). Регенерация может быть осуществлена в любом из режимов ОЗУ, однако наиболее просто ее выполнить в режиме регенерации по сигналу RAS, когда сигналCASнаходиться в неактивном высоком логическом состоянии.

Основные параметры ОЗУ:

Напряжение питания, Uсс В 4,5-5,5;

Ток потребления, мА:

динамический ICCAV <45(27);

хранения ICCS <3,2;

Входное напряжение, В:

высокого уровня UIN 2,4-6,0;

низкого уровня UIL1,0…+0,8;

Выходное напряжение, В:

высокого уровня UOHприIOH= -2 мА >2,4;

низкого уровня UOL при IOL= 4 мА <0,4;

Время выборки относительно сигнала выбора адреса столбцов tCAS, нс 70.

Подробная схема подключения ОЗУ к шинам адреса и данных посредством буферного регистра и шинного формирователя будет представлена в пункте разработки уточненной схемы МП БИС, сигналы и входы с помощью которых производиться подключение микросхемы будут указаны в пункте подбора буферного регистра и шинного формирователя.

БР

ША

ОЗУ

ФШ

ШД

Рисунок 9 – Подключение ОЗУ к шинам адреса и данных

3.2 Выбор постоянно запоминающего устройства

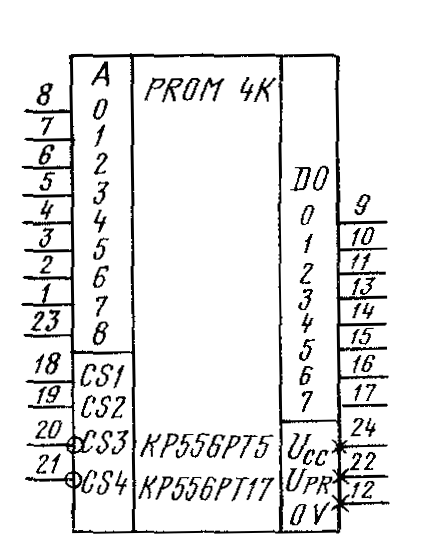

Для расширения памяти программ микроконтроллера в соответствии с заданием выберем К556РТ5. Это ППЗУ, изготовленная по ТТЛШ-технологии. Технические характеристики ПЗУ представлены в таблице 3.

Таблица 3 – Основные электрические параметры микросхемы К556РТ5

|

Название параметра |

Значение параметра |

|

Емкость |

512х8 (4К) |

|

Напряжение питания в статическом режиме |

Ucc=5±0,5 В |

|

Время выборки |

80 нс |

|

Потребляемая мощность |

1000 мВт |

|

Тип выхода |

ТТЛ-ОК |

|

Ток потребления, мА |

190 |

Условное обозначение микросхемы К556РТ5 приведено на рисунке 10.

Рисунок 10 – Микросхема К556РТ5

Матрица до программирования, т. е. в исходном состоянии, содержит однородный массив проводящих перемычек, соединяющих строки и столбцы во всех точках их пересечений. Перемычки устанавливают из поликристаллического кремния. Перемычка в матрице выполняет роль ЭП. Наличие перемычки кодируют логической 1, если усилитель считывания является повторителем, и логическим 0, если усилитель считывания — инвертор. Следовательно, микросхема ППЗУ в исходном состоянии перед программированием в зависимости от характеристики выходного усилителя может иметь заполнение матрицы либо логическим 0, либо логической 1.

Операция-программирования заключается в разрушении (пережигании) части плавких перемычек на поверхности кристалла импульсами тока амплитудой 30 ... 50 мА. Технические средства для выполнения этой операции достаточно просты и могут быть построены самим пользователем.

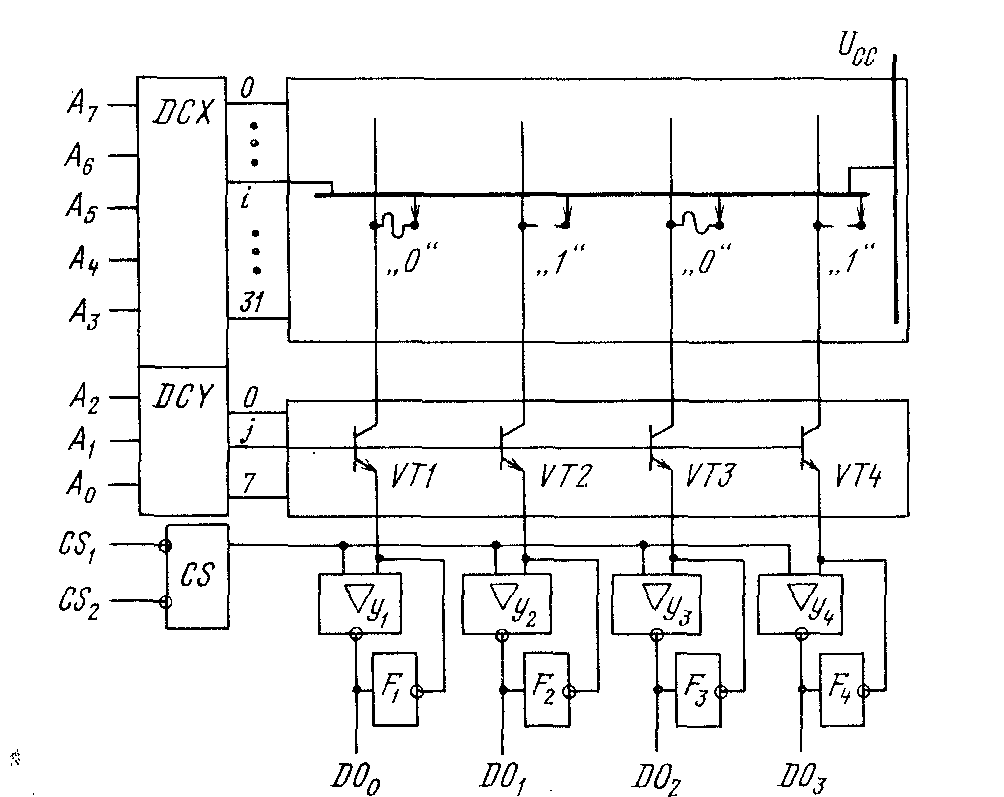

Типичный вариант реализации микросхемы ППЗУ представлен на рисунке 11.

Рисунок 11 – Структурная схема микросхемы К556РТ5.