- •Введение

- •1 Анализ технического задания

- •2.1.5 Управление работой микроконтроллера. Устройство управления в каждом цикле команды формирует последовательность сигналов, управляющих всеми блоками мп и организует их взаимосвязь.

- •2.2 Система команд к1816ве51

- •2.3 Генератор тактовых импульсов

- •4.2 Архитектура параллельного интерфейса кр580вв55

- •4.3 Архитектура программируемого контролера прерываний кр580вн59

- •4.5 Архитектура контролера прямого доступа к памяти кр580вт57

- •5.3 Подключение микросхем, входящих в мпс к шинам данных и

- •Заключение

- •Список используемых источников

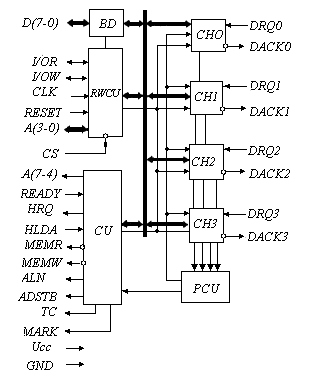

4.5 Архитектура контролера прямого доступа к памяти кр580вт57

БИС контролера прямого доступа к памяти (КПДП) предназначена для организации высокоскоростного обмена данными между памятью и внешними устройствами, выполняемого по инициативе внешнего устройства. КПДП генерирует управляющие сигналы, необходимые для организации обмена. КПДП содержит четыре канала прямого доступа, каждый из которых обеспечивает передачу блока данных размером до 16К байт с произвольным начальным адресом.

Упрощенная структурная схема КПДП представлена на рисунке 19.

Рисунок 19 – Структурная схема КПДП

В состав БИС входят: двунаправленный двустабильный буфер данных (BD), предназначенный для обмена информацией между МП и КПДП; схема управления чтением/записью (RWCU), адресующая внутренние регистры КПДП и управляющая обменом по шине D(7-0); блок управления (CU), содержащий регистры режима и состояния и обеспечивающий последовательность операций, необходимую для организации режима прямого доступа к памяти; блок управления приоритетами (PCU), обеспечивающий определенный порядок обслуживания запросов внешних устройств; четыре канала прямого (СН0 – СН3), каждый из которых содержит регистр адреса ячейки памяти, с которой производится обмен, и счетчик циклов обмена, два старших разряда которого отведены для задания операций обмена.

5 РАЗРАБОТКА ИНТЕРФЕЙСА И УТОЧНЕННОЙ СТРУКТУРНОЙ

СХЕМЫ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ

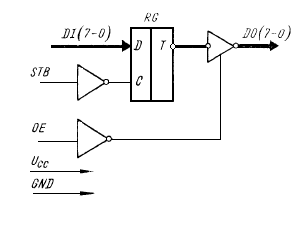

5.1 Буферный регистр КР580ИР83

Буферный регистр КР580ИР83 представляет собой 8-разрядный параллельный регистр с тристабильным выходом. Он используется для реализации схем фиксации, буферизации и мультиплексирования в микропроцессорной системе.

Структурная схема КР580ИР83 представлена на рисунке 20.

Рисунок 20 – Структурная схема КР580ИР83

Запись входных данных в буферные регистры производится при переходе сигнала STB с Н-уровня в L-уровень.

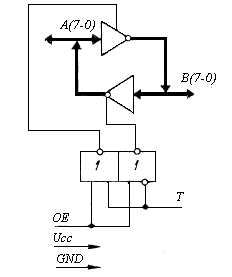

5.2 Шинный формирователь КР580ВА87

Шинный формирователь КР580ВА87 представляет собой 8-разрядный параллельный приемопередатчик с тристабильным выходом. Он используется для реализации различных буферных схем в микропроцессорных системах. На выходах микросхемы генерируются инвертированные выходные данные.

Структурная схема шинного формирователя КР580ВА87 представлена на рисунке 21.

Рисунок 21 – Структурная схема шинного формирователя КР580ВА87

При Н-уровне входного сигнала на входе Т и L-уровне сигнала на входе ОЕ информация с выводов А (7 – 0) передается на выводы В (7 – 0). При L-уровне сигнала на входе Т и L-уровне сигнала на входе ОЕ информация с выводов

В(7 – 0) передается на выводы А(7 – 0).

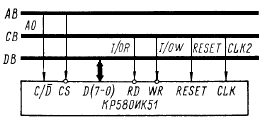

5.3 Подключение микросхем, входящих в мпс к шинам данных и

шинам адреса

Подключение БИС последовательного интерфейса КР580ИК51 представлено на рисунке 22.

АВ – шина адреса; СВ –шина управления; DB – шина данных

Рисунок 22 – Подключение БИС последовательного интерфейса

КР580ИК51 к шинам адреса, данных и управления

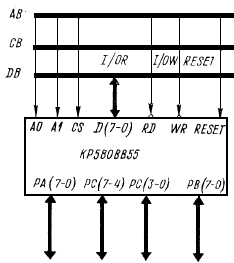

Подключение БИС параллельного интерфейса КР580ВВ55 представлено на рисунке 23.

АВ – шина адреса; СВ –шина управления; DB – шина данных

Рисунок 23 – Подключение БИС параллельного интерфейса

КР580ВВ55 к шинам адреса, данных и управления

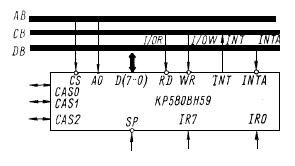

Подключение БИС программируемого контролера прерываний КР580ВН59 представлено на рисунке 24.

АВ – шина адреса; СВ –шина управления; DB – шина данных

Рисунок 24 – Подключение БИС программируемого контролера

прерываний к шинам адреса, данных и управления

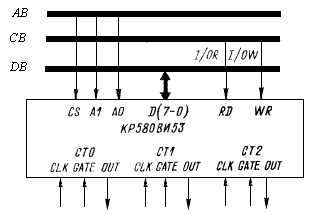

Подключение БИС таймера КР580ВИ53 представлено на рисунке 25.

АВ – шина адреса; СВ –шина управления; DB – шина данных

Рисунок 25 – Подключение БИС таймера КР580ВИ5 к шинам

адреса, данных и управления

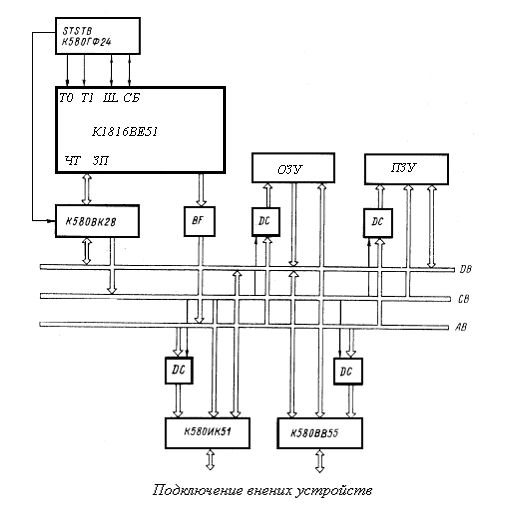

5.4 Разработка структурной схемы МПС

МикроЭВМ на основе микросхем комплекта К580 строятся по модульному принципу, который обеспечивает подключение к единой магистрали модулей ЦП, ЗУ и УВВ. Магистральная структура связей между модулями минимизирует аппаратуру, уменьшает число схем сопряжения и обеспечивает возможность простого расширения схем.

Структурная схема микроЭВМ на основе МП К1816ВЕ51 приведена на рисунке 26.

BF – буферный регистр; DB – шина данных; СВ – шина управления;

АВ– шина адреса

Рисунок 26 – Структурная схема микроЭВМ на основе МП К1816ВЕ51

6 РАЗРАБОТКА ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ

Обработка информации от цифровых датчиков производится путем ввода значений х1, х2, х3, х4 и вычисления булевой функции f1(х1, х2, х3, х4)= у1=Х1&Х2vХ3

При единичном значении f1 вырабатывается управляющий сигнал у1=1 длительностью t1=80 мкс.

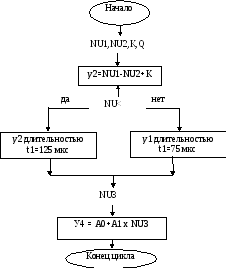

При обработке информации с датчиков ПМ принимает коды NU1,NU2 с выходов АЦП и код константы К с регистра пульта управления.

Далее производится вычисление функций у2=NU1-NU2+К и сравнивается с константой Q, которая хранится в ПЗУ. В зависимости от результата сравнения вырабатывается один из двух двоичных управляющих сигналов у2 или у3 заданной длительности по следующему правилу: если NU<Q, то вызывать у2 длительностью 125 мкс, иначе выдать у3 длительностью 75 мкс. Далее производится вычисление у4 и результат в виде 8-разрядного кода выдается на вход ЦАП, встроенного в БИС К1816ВЕ51.

Все двоичные переменные и константы рассматриваются как целые без знака.

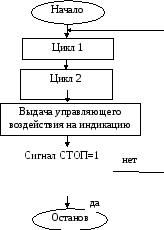

После выдачи всех управляющих воздействий проверяется состояние тумблера «СТОП» на пульте управления. Если СТОП=0, цикл управления начинается с начала, иначе выполняется процедура останова системы, включающая следующие действия: формируется сигнал установки системы в исходное состояние путем подачи на линию начальной установки интерфейса двух прямоугольных импульсов, выполняется команда СТОП.

Блок схема управления представлена в виде двух циклов.

Рисунок 27 – Цикл 1 управляющей программы

Рисунок 28 – Цикл 2 управляющей программы

Рисунок 29 – Блок – схема программы управления

Листинг программы в Ассемблере: