- •Введение

- •1 Анализ технического задания

- •2.1.5 Управление работой микроконтроллера. Устройство управления в каждом цикле команды формирует последовательность сигналов, управляющих всеми блоками мп и организует их взаимосвязь.

- •2.2 Система команд к1816ве51

- •2.3 Генератор тактовых импульсов

- •4.2 Архитектура параллельного интерфейса кр580вв55

- •4.3 Архитектура программируемого контролера прерываний кр580вн59

- •4.5 Архитектура контролера прямого доступа к памяти кр580вт57

- •5.3 Подключение микросхем, входящих в мпс к шинам данных и

- •Заключение

- •Список используемых источников

1 Анализ технического задания

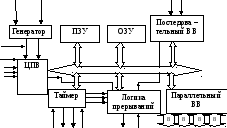

Управляющая микроЭВМ проектируется на базе однокристального МП или однокристальной микроЭВМ К1816ВЕ51 и включает в себя основные устройства: процессорный модуль, память ОЗУ и ПЗУ, устройства параллельного ввода/вывода для связи с объектом управления, блок последовательного канала для связи с ЭВМ верхнего уровня, программируемый системный таймер, контролер прерываний, контролер прямого доступа в память, пульт управления.

Все модули системы объединяются интерфейсом (магистралью), требованию к которому определяются заданным типом микропроцессора – К1816ВЕ51. Обмен данными может осуществляться как в едином адресном пространстве, так и в разделенном с помощью управляющих сигналов обращения к ВУ и ЗУ.

Процессорный модуль включает в себя микропроцессор и дополнительные БИС: тактовый генератор, шинные формирователи, регистры защелки и др.

Устройства ввода для связи с ОУ должны обеспечить ввод в процессорный модуль значения х1, х2, х3, х4 с двоичных датчиков, а также 8 –разрядных двоичных кодов NU1, NU2, NU3, принимаемых с выхода АЦП. Сигнал датчика в аварийной ситуации ха воспринимается только подсистемой прерываний.

Устройства вывода должны обеспечить выдачу двоичных управляющих воздействий у1, у2, у3 определенной длительности и кода управляющего напряжения У4 – 8 – разрядного двоичного вектора на вход ЦАП. В структуру ОУ входит устройство принимающее массив данных из ПЗУ(ОЗУ) в режиме прямого доступа в память (ПДП). Запрос на ПДП возникает асинхронно по отношению к процедуре управления.

Пульт управления должен обеспечивать ввод в ПМ значения 8 – разрядной двоичной константы К, ввод двоичного значения сигнала «СТОП», формирование сигнала начальной установки системы, вывод на светодиодную

индикацию значений х1, х2, х3, х4, у1, у2, у3, NU1, У4.

Системный таймер должен обеспечивать отсчет временных задержек, реализуемых при работе алгоритма управления.

Блок последовательного обмена предназначен для передачи на микроЭВМ верхнего уровня информации о состоянии процесса управления. По запросу со стороны микроЭВМ разрабатываемая управляющая микроЭВМ должна обеспечивать выдачу по последовательному каналу кадра. Передача информации с верхнего уровня не предусмотрена.

Контролер прерываний обеспечивает фиксацию запросов от различных источников и дисциплину обслуживания запросов.

Алгоритм управления определяется функциями:

у1=Х1&Х2vХ3, t1=80 мкс,

где Х1,Х2,Х3 – значения с двоичных датчиков;

у2=NU1-NU2+К, t2=125 мкс t3=75 мкс,

где NU1,NU2 – 8-разрядные двоичные коды;

t1,t2,t3 – длительность управляющих сигналов.

Блок памяти реализуется на БИС следующих типов: БИС ОЗУ – К537РУ3, БИС ПЗУ – К556РТ6.

2 РАЗРАБОТКА ПРОЦЕССОРНОГО МОДУЛЯ И ИНТЕРФЕЙСА

2.1 Анализ структуры ЦП К1816ВЕ51

В состав однокристального МК К1816ВЕ51 (рисунок 1) входит 8-разрядный ЦП, управляющее ПЗУ, внутреннее ОЗУ данных, 32 линии прямого ВВ, четыре тестируемых входа, канал последовательного ВВ, два или три 16-разрядных таймера/счетчика Т и логика двухуровневой системы прерываний с пятью или шестью источниками запросов. Эти средства образуют резидентную часть МК, размешенную непосредственно на кристалле. Базовая организация предоставляет встроенные средства расширения своих ресурсов, которые предусматривают либо реализацию вне кристалла всей памяти программ, либо расширение памяти, имеющейся внутри кристалла до 64К байт. Имеется возможность подключения дополнительной внешней памяти данных в 64К байт. Дальнейшее расширение ресурсов может быть выполнено только с помощью внешних средств.

Приборы семейства ВЕ51/8052 размещаются в стандартных 40 выводных корпусах, для их работы требуется единственный источник питания +5 В.

Основные параметры БИС К1816ВЕ51:

Источник питания, В 5.

Рассеиваемая мощность, В 1,5.

Диапазон рабочих температур,0С 0…+70.

Частота синхронизации, МГц 2,5.

Емкость ОЗУ, Кбайт 64.

Емкость ПЗУ, Кбайт 1.

Для сокращения ширины физического интерфейса большинство логических линий совмещаются. Так при обращениях к внешней памяти порт Р0 выполняет роль совмещенной шины адреса/данных, а Р2 - шины старшей части адреса.

Все выводы порта РЗ выполняют роль линий управления и специального ВВ. В архитектуре К1816ВЕ51 и ее модификациях использован стандартный для МК принцип независимости сред для хранения программ и данных. Всего же архитектура ВЕ51 включает пять типов пространств, четыре из которых являются областями данных:

RSEG Пространство регистров

DSEG Пространство внутренней памяти

BSEG Битовое пространство данных

XSEG Пространство внешней памяти

CSEG Пространство программного кода

P3.0 P3.1

RxD TxD

XTAL1 XTAL2

ЕА

ALE

RST

RSEN

P3.7RD

P3.6WR

T0 T1 T2*T2EK* INT0 INT1 P0 P1 P2 P3

P3.4 P3.5 P1.0 P1.1 P3.2 P3.3 A0 A

AD0 – AD7

A8 – A15

Рисунок 1 – Схема микроконтроллера

Набор регистров ВЕ51. Набор программно-доступных регистров процессора ВЕ51 приведен на рисунке 2. Архитектура относится к классу аккумуляторных с переключаемыми банками рабочих регистров. Поэтому центральным регистром набора считается 8-разрядный аккумулятор А, выполняющий обычные функции основного арифметического регистра.

Регистр В служит расширением аккумулятора А, необходимым для осуществления операций умножения и деления, причем он является как источником, так и приемником операндов. Во всех других операциях регистр В выполняет функции, определяемые пользователем.

|

15 87 0 |

|||||||||

|

|

РС |

||||||||

|

DPH |

DPL |

DPTR

|

|||||||

|

B |

A |

||||||||

|

|

C Y |

A C |

F 0 |

RC |

O V |

P |

|

PSW

SP |

|

|

|

|

||||||||

|

R0 |

|

R1 |

|

R2 |

|

R3 |

|

R4 RB0 |

|

R5 |

|

R6 RB1 |

|

R7 RB2 |

Рисунок 2 – Набор регистров

Регистр слова состояния программы включает в себя флажки:

PSW.7 CY Перенос из старшего разряда АЛУ;

PSW.6 АС Дополнительный перенос из младшей тетрады АЛУ;

PSW.5 F0 Флажок пользователя общего назначения включает

также флажки;

PSW.2 OV Признак арифметического переполнения результата;

PSW.1 P Признак четности.

Сюда же входит двухразрядное поле RS (Registers Select) выбора одного из четырех возможных банков рабочих регистров. Флажки признаков результата CY, АС и OV, как правило, отражают состояние последней арифметической операции, флажок Р - четность содержимого А. Флажок переноса CY является аккумулятором булевого процессора. назначение флажка F0 определяется пользователем в конкретной ситуации.

Шестнадцатиразрядный программный счетчик PC управляет последовательностью выполнения команд, хранящихся в программной памяти объемом до 64К байт. Указатель данных DPTR также имеет длину 16 разрядов, каждая его половина может быть адресована независимо от другой. Этот регистр используется в качестве адресного при пересылке констант из памяти программ и доступе к переменным из внешней памяти данных, а также для организации передачи управления.

Указатель стека образует системный стек глубиной до 256 байт. Он всегда содержит адрес последнего байта, занесенного в стек. Стек растет в сторону увеличения содержимого SP.

В МК ВЕ51 предусмотрено четыре банка по восемь рабочих регистров R0-R7 в каждом, переключаемых полем RS слова состояния программы. Регистры выполняют общецелевые функции промежуточного хранения данных. По аналогии с ВЕ48 два регистра R0 и R1 каждого банка реализуют также функции 8-разрядных указателей данных.

Использование наборов рабочих регистров позволяет существенно уменьшить длительность переключения контекстов ЦП, что очень важно для МС реального времени. Следует также отметить, что в ВЕ51 отсутствует ряд ограничений, накладываемых на обработку подпрограмм и процедур обслуживания прерываний.

При сбросе МК все регистры устанавливаются в исходное состояние. Программный счетчик PC принимает значение 0000Н, аккумулятор А - 00Н; В - 00Н; PSW - 00Н; SP - 07H и DPTR - 0000Н. Сброс PC обеспечивает передачу управления по стартовому адресу 0000Н, а установка SP в состояние 07Н поддерживает совместимость со стеком ВЕ48. Сброс PSW реализует выбор нулевого регистрового банка RB0.

2.1.1 Арифметико – логическое устройство ВЕ51.В состав АЛУ входят блоки: комбинационная схема обработки байтов, регистры, аккумулятор, схема десятичного корректора и схема формирования признаков. Аккумулятор используется в качестве регистра операнда и регистра результата.

Комбинационная схема АЛУ выполняет следующие операции:

- операции сложения;

- логические операции И, ИЛИ и исключающее ИЛИ;

- инкремент, декремент, инверсию, циклический сдвиг влево и

вправо через флаг переноса;

- десятичную коррекцию содержимого аккумулятора.

Флаги переноса фиксируются на триггерах, входящих в состав регистра слова состояния программы – ССП (рисунок 3). Логика условных переходов МП оперирует флагами F0 и F1 (их функции определяет разработчик), флагом переполнения таймера TF, сигналами на входах Т0 и Т1.

7 6 5 4 3 2 1 0

|

С |

AC |

F0 |

BS |

1 |

S2 |

S1 |

S0 |

C –перенос; АС – вспомогательный перенос; F0 – флаг пользователя;

BS – банк регистров; S0-S1 – указатель стека

Рисунок 3 – Формат слова состояния программы

Программистом могут быть использованы флаги рабочего банка регистров.

2.1.2 Организация памяти ВЕ51.Пространство, внутренней памяти DSEG имеет общий объем 256 байт. Однако организация ВЕ51 предусматривает реализацию только первой его половины (128 байт).

Все банки рабочих регистров, а также системный стек в МК ВЕ51 располагаются во внутренней памяти данных и могут рассматриваться как обычные ячейки памяти. Существуют два способа адресации памяти данных МК: прямой (direct) и косвенный (Ri, i = 0-1) через регистры R0, R1 выбранного в данный момент одного из банков RB0 - RB3. При прямой адресации доступна только младшая половина адресного пространства внутренней памяти данных (128 байт), при косвенной обеспечивается доступ к любой ее ячейке (256 байт). Введение прямой адресации значительно расширило возможности обработки данных МК, в частности появились средства прямого доступа в соседние регистровые банки и стек системы, интерпретируемые как обычные ячейки памяти.

Микроконтроллер ВЕ51 имеет мощную и развитую подсистему ВВ и средства поддержки режима реального времени. Для их управления в МК предусмотрен ряд регистров, которые размещаются во второй половине прямо адресуемого пространства, образующей пространство специальных регистров (128 байт). Сюда же включены порты и основные регистры ЦП.

Центральный процессор ВЕ51 содержит специальную логику, предназначенную для выполнения нескольких однобитовых операций – булев, или одноразрядный процессор для вычисления булевых выражений. В основу булева процессора положен стандартный аккумуляторный принцип организации. В данном случае роль аккумулятора выполняет флажок переноса CY.

Для хранения булевых данных в архитектуре ВЕ51 предусмотрено специальное одноразрядное линейно упорядоченное пространство BSEG объемом

256 байт, которое физически совмещено с байтовым пространством данных DSEG. При этом одна часть пространства BSEG попадает на обычные ячейки памяти DSEG и может рассматриваться как область общего назначения. Обычно она используется для хранения булевых переменных. Другая часть пространства BSEG попадает на ячейки памяти, совмещенные с регистрами МК. что обеспечивает независимый доступ к их отдельным разрядам. В булевом пространстве определена только прямая адресация bit.

Пространство внешней памяти XSEG имеет объем 64К байт и реализуется внешними по отношению к МК средствами. В команде используются два типа адресации: косвенная регистровая по DPTR и страничная с номером страницы в Р2 и смещением в R0, R1.

Память программ CSEG адресуется 16-разрядным счетчиком PC и, следовательно, может иметь объем до 64 Кбайт.

2.1.3 Порты ввода-вывода. Подсистема ВВ микроконтроллера ВЕ51 размещается непосредственно на кристалле. Для ВВ данных и управления процессом их передачи в состав МК введен ряд портов данных и регистров управления/состояния, совокупность которых образует набор специальных регистров.

Физическая система ВВ микроконтроллера ВЕ51 состоит из четырех двунаправленных 8-разрядных портов Р0 - РЗ. Все порты ВВ отображены в пространстве внутренней памяти DSEG по адресам 80Н, 90Н, 0А0Н, 0В0Н и ничем не отличаются от обычных ячеек памяти. Отказ от изолированного пространства ВВ. используемого в архитектуре ВЕ48, позволил увеличить вычислительную эффективность МС интенсивного ВВ, привел к более регулярной структуре набора команд ВЕ51. Если ранее для увеличения возможностей арифметической – логической обработки данных ВВ было необходимо вводить ряд новых команд, то теперь любая команда с операндом из внутренней памяти может быть применена к содержимому портов Р0 - РЗ.

Кроме того, порты Р0 - РЗ совмещены с битовым пространством BSEG, что обеспечивает доступ к отдельным его разрядам независимо от других. Порты Р0 - РЗ занимают адреса BSEG: 80Н - 87Н, 90Н - 97Н, 0А0Н -0А7Н и 0В0Н - 0В7Н соответственно.

Расширение пространства ВВ может быть выполнено за счет области XSEG или другими средствами с помощью самих портов Р0 - РЗ и SBUF.

При обращении к внешней памяти программ или данных порты Р0, Р2 выполняют функции системных шин AD и АВ соответственно. Младший байт адреса и данные передаются через Р0 в мультиплексном режиме: сначала выводится адрес, а затем для передачи данных используется порт. Старший байт адреса формируется на Р2. Линии порта РЗ реализуют управление циклами обмена и другие специальные функции аппаратного уровня:

Р3.0 RxD Вход приемника последовательного канала;

Р3.1 TxD Выход передатчика последовательного канала;

Р3.2 INT0 Вход запроса на прерывание 0;

РЗ.З INT1 Вход запроса на прерывание 1;

Р3.4 T0 Внешний вход таймера/счетчика 0;

Р3.5 T1 Внешний вход таймера/счетчика 1;

Р3.6 WR Строб записи в XSEG;

Р3.7 RD Строб чтения XSEG.

Порты Р1 - РЗ имеют встроенную нагрузку, тогда как для порта Р0, выполненного по схеме с открытым коллектором, требуется внешняя нагрузка. Каждый вывод портов Р0 - РЗ может быть использован в качестве выходного независимо от других. Для перевода какого-либо вывода в режим входа в соответствующий разряд выходного регистра должна быть записана 1.

Следует отметить, что в отличие от ВЕ48 в МК ВЕ51 все 32 вывода портов Р0 - РЗ тестируются индивидуально с помощью условных команд

ветвления:

JB bit, rel ; Если BSEG(bit)=1, то SJMP rel

JNB bit, rel ; Если BSEG(bit) = 0, то SJMP rel

JBC bit, rel ; Если BSEG(bit) = 1, то SJMP rel и BSEG(bit) ← 0

Последняя команда после тестирования всегда на выводе порта, как и в любом другом разряде из пространства BSEG, устанавливает 0.

2.1.4 Таймеры/счетчики. К стандартным средствам поддержки режима реального времени относятся таймеры/счетчики и подсистема прерываний. Если таймеры необходимы для организации системных меток реального времени и отработки временных интервалов, то подсистема прерываний обеспечивает своевременную реакцию МК на асинхронные события, происходящие как внутри МС, так и вне ее. В состав BE51 входят два 16-разрядных таймера/счетчика СТО, СТ1. Состояние таймеров/счетчиков отражается программно-доступными регистровыми парами (TH0,TL0), (TH1, ТL1) и (ТН2, TL2) соответственно, размещенными в пространстве DSEG по адресам (8СН, 8АН),(8DH, 8ВН) и (0CDH, 0ССН).

Таймеры/счетчики СТ0 - СТ2 могут быть запрограммированы для работы либо в качестве таймера, либо в качестве счетчика. Функция таймера состоит в счете числа машинных циклов, следующих с частотой OSC/12.

Функция счетчика заключается в отслеживании числа переходов из 1 в 0 на соответствующих входах ТО, Tl, T2.

Управление режимом работы СТО, СТ1 осуществляет регистр TMOD (Timer/Counter Mode), который расположен по адресу 89Н. Регистр разбит на два 4-разрядных подрегистра T0MOD и T1MOD, которые ответственны за управление СТО и СТ1 соответственно.

За управление СТ0, СТ1 также ответствен регистр TCON (Timer/Counter Control), расположенный по адресу 88Н.

Для управления работой СТ2 служит регистр T2CON (Timer/Counter 2 Control), расположенный по адресу 0С8Н.