- •Введение

- •1 Анализ технического задания

- •2.1.5 Управление работой микроконтроллера. Устройство управления в каждом цикле команды формирует последовательность сигналов, управляющих всеми блоками мп и организует их взаимосвязь.

- •2.2 Система команд к1816ве51

- •2.3 Генератор тактовых импульсов

- •4.2 Архитектура параллельного интерфейса кр580вв55

- •4.3 Архитектура программируемого контролера прерываний кр580вн59

- •4.5 Архитектура контролера прямого доступа к памяти кр580вт57

- •5.3 Подключение микросхем, входящих в мпс к шинам данных и

- •Заключение

- •Список используемых источников

2.1.5 Управление работой микроконтроллера. Устройство управления в каждом цикле команды формирует последовательность сигналов, управляющих всеми блоками мп и организует их взаимосвязь.

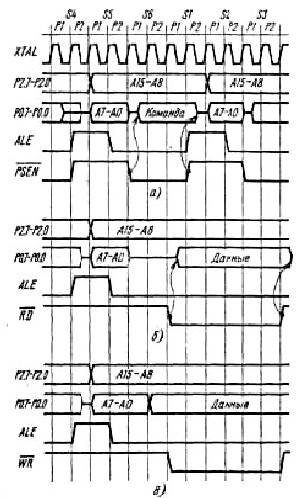

Синхронизация микроконтроллера. Приборы семейства ВЕ51 размещаются в стандартных 40-выводпых корпусах (рисунок 4), для их работы требуется единственный источник питания +5 В. Встроенный в схему генератор рассчитан на работу с кварцевым резонатором (диапазон частот 3,5-12 МГц), подключенным к выводам XTAL1 и XTAL2 (рисунок 5). Возможно также использование внешнего ГТИ с подачей тактовых импульсов па вывод XTAL1. При делении частоты OSC на 2 получается основная внутренняя тактовая частота CLK. Первая половина периода CLK называется фазой Р1, вторая - фазой Р2. Каждый машинный цикл состоит из шести периодов CLK, называемых состояниями S1, S2, …, S6 или 12 периодов OSC, называемых фазами S1P1. S1P2, S2P1,S2P2 S6P1. S6P2.

Командный цикл МК содержит несколько машинных циклов и отсчитывается от фазы S1P1. По фазе S1P2 в IR фиксируется код операции. Второй байт двухбайтовой команды читается в S4P2 того же машинного цикла, третий - в S1P2 следующего. Таким образом, для ввода каждого байта требуется один машинный полуцикл. Вовремя всех оставшихся полуциклов в фазах S1P2 и S4P2 читается код операции следующей размещенной в памяти команды. Однако байт в IR не вводится и PC не инкрементируется, что приводит к его игнорированию. Ввод повторяется до окончания текущего командного цикла, который всегда завершается в фазе S6P2. Вслед за этим начинается новый командный цикл с вводом в IR кода операции следующей по исполнению команды.

Другую временную последовательность исполнения имеет однобайтовая двух цикловая команда обращения к внешнему ОЗУ Данных MOVX. Доступ к ОЗУ реализуется во втором машинном Цикле, поэтому первый машинный цикл

соответствует общей схеме, а во втором отсутствуют пустые операции FETCH. Во

время второго машинного цикла первый строб ALE отсутствует, так как доступ к внешнему ОЗУ требует всего машинного цикла.

|

XTAL1 19 18 XTAL2 9 RST |

MC |

39

AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7

P0.0 38

P0.1 37

P0.2 36

P0.3 35

P0.4 34

P0.5 33

P0.6 32

P0.7 |

|

10

K=D T=D INT0 INT1 T0 T1 WR RD P3.0 11

P3.1 12

P3.2 13

P3.3 14

P3.4 15

P3.5 16

P3.6 17

P3.7 |

|

1 T2*

T2EX* P1.0 2

P1.1 3

P1.2 4 P1.3 5 P1.4 6 P1.5 7 P1.6 8 P1.7 |

|

31

EA |

|

A8 A9 A10 A11 A12 A13 A14 A15

21 P2.0 22

P2.1 23

P2.2 24

P2.3 25

P2.4 26

P2.5 27

P2.6 28

P2.7 30

|

|

ALE 29

PSEN |

Рисунок 4 – Условное графическое обозначение МП

Запись результата операции в порты Р0 —РЗ реализуется в фазе S6P2 последнего машинного цикла соответствующей команды, однако на выходе порта новое значение появляется только в следующей фазе S1P1.

При записи в порты Р1—РЗ информации, требующей перехода из 0 в 1, через выходную цепь в течение S1P1 и S1P2 пропускается импульс тока,

амплитуда которого в 100 раз превышает номинальное значение.

10 мкФ 20МГц

|

XTAL1 10 мкФ

Кварц XTAL2

10 мкФ

RST |

|

|

8.2 k

Рисунок 5 – Схема синхронизации МП

Это делается для повышения скорости переключения выходных сигналов. Порт Р0 такими свойствами не обладает. Выходы портов Р1—Р3 обеспечивают управление четырьмя маломощными ТТЛ – входами (IOL = 1,6 мА). Нагрузочная способность порта Р0 IOL = 3,2 мА. Вход RST служит для приведения МК в исходное состояние. Сигнал запроса воспринимается всякий раз, когда на входе RST удерживается напряжение высокого уровня более двух машинных циклов (24 периода OSC) при условии, что генератор запущен. В течение следующего машинного цикла формируется внутренний сигнал сброса, который, повторяется до тех пор, пока вход RST активен.

Микроконтроллеры семейства ВЕ51 осуществляют режим хранения записанных в их внутреннюю память данных при выключенном источнике питания +5В. В данном режиме запасное напряжение питания поступает на вход RST, а ток потребления очень мал.

а – считывание CSEG; б – считывание XSEG; в – запись XSEG

Рисунок 6 – Временная диаграмма обращения к внешней памяти:

При подаче напряжения +5 В запасной источник должен оставаться во включенном состоянии еще два машинных цикла, в течение которых выполняется общий сброс МК.