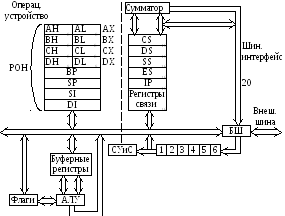

30. Архитектура 16 разрядного МП (основные блоки, краткая характеристика)

В МП i8086 применена конвейерная архитектура, которая позволяет совмещать во времени циклы исполнения и выборки из памяти кодов последующих команд. Это достигается параллельной работой 2-х независимых устройств – операционного устройства и шинного интерфейса.

Операционное устройство выполняет команду, а шинный интерфейс осуществляет взаимодействие с внешней шиной: выставляет адреса, считывает коды команд и операнды, записывает результаты вычисления в память или устройства ввода/вывода.

Операционное устройство состоит из РОН для хранения промежуточных результатов вычислений (данных и адресов).

РОН делится на:

1. Регистры данных – 4е 16ти разрядных регистра (АХ, ВХ, СХ, ДХ), каждый из которых состоит из 2х 8ми разрядных регистров и регистры-указатели (BP, SP, SI, DI). Они служат для хранения адресов при косвенной адресации.

2. АЛУ с буферными регистрами.

3. Схема управления и синхронизации, дешифрует коды команд и генерирует управляющие сигналы для всех блоков схемы МП.

4. Шинный интерфейс, состоит:

- 4х сегментных регистров (CS, DS, SS, ES): CS – сегмент кодов, DS – сегмент данных, SS – сегмент стека, ES – сегмент дополнительных данных.

- указатель команд IP

- регистры связи

- буферная схема шин адреса/данных

- сумматора

- 6-ти байтная регистровая память (очередь команд) работает по принципу FIFO-FIRSTINPUT-FIRSTOUTPUT (первый пришел – первый вышел), сохраняет на выходе порядок поступления команд.

Длина очереди 6 байт.

Если операционное устройство занято выполнением команды, шинный интерфейс самостоятельно инициирует выборку кодов команд из памяти в очередь команд.

//Флаг регистр 16- разрядный устанавливает 9 флагов.//

Выборка из памяти очередного командного слова осуществляется когда в очереди команд обнаруживаются 2 свободных байта. Очередь увеличивает быстродействие МП в случае последовательного выполнения команд. При выборке команд переходов, запросов и возвращения из подпрограмм обработки запросов прерываний, очередь команд сбрасывается и выборка начинается с нового места программной памяти.

Шинный интерфейс формирует физический 20-ти разрядный адрес из 2х 16ти разрядных слов. Первым словом является содержимое одного из сегментных регистров, второе слово зависит от типа адресации операнда или кода команды. Суммирование 16-ти разрядных слов происходит со смещением на 4 разряда и осуществляется с помощью сумматора, который входит в состав шинного интерфейса.