- •Національний університет „Львівська політехніка” Кафедра атхп Курсовий проект

- •1. Індивідуальне завдання до курсового проекту з дисципліни «мікропроцесорна техніка» на тему «проектування інтелектуального давача на базі мікоконтролера 89с51»

- •Структурна схема інтелектуального давача, побудованого на базі мікроконтролера 89с51 .

- •2.1 Мікроконтролер 89с51 .

- •Опис роботи інтелектуального давача.

- •Побудова контролера клавіатури та семисегментного індикатора.

- •3.1. Ввід інформації з клавіатури.

- •3.2. Вивід інформації на семисегментний індикатор.

- •3.3. Програма для програмування програмованого логічного пристрою контролера

- •3.4. Часові діаграми pоботи програмованого логічного пристрою контролера

- •4. Робота аналого-цифрового перетворювача

- •Контролери послідовного каналу вводу-виводу.

- •Програма для роботи мікропроцесорного пристрою, побудованого на базі мікроконтролера 89с51

- •Висновки

- •Література

-

Структурна схема інтелектуального давача, побудованого на базі мікроконтролера 89с51 .

Cтруктурна схема інтелектуального давача побудованого на базі мікроконтролера 89С51 складається з:

- мікроконтролера 89С51, який здійснює керування зовнішніми пристроями вводу/виводу та проводить обчислення, згідно програми по обчисленню величини µвп - динамічна в’язкість вологої водяної пари (рівняння наведені в індивідуальному завданні);

- двох аналогово-цифрових перетворювачів (АЦП ADS 1286 PK), які здійснюють перетворення аналогового сигналу, що надходить з первинного перетворювача,у послідовний цифровий сигнал;

- клавіатури (5x3), за допомогою якої вводяться постійні величини або виводяться певні величини для перевірки програми;

- дев’ятирозрядного рідкокристалічного семисегментного індикатора, який потрібен для показу величин, які вводяться, знаходяться в пам’яті (тобто вже введені), вимірюються чи обраховуються в даний момент часу;

- контролеру клавіатури (5С090) та дев’ятирозрядного рідкокристалічного семисегментного індикатора, який обслуговує клавіатуру та індикатор;

- контролеру каналу послідовного вводу/виводу , який дозволяє обмінюватися інформацією з іншими контролерами чи з вищим рівнем керування (наприклад комп’ютером);

- блоку живлення.

Структурна схема інтелектуального давача наведена на рис.2.1.

Рис.2.1 Загальна структурна схема мікропроцесорного пристрою: ША - шина адресів; ШД - шина даних; КШ - керуюча шина.

2.1 Мікроконтролер 89с51 .

Основним елементом інтелектуального давача є мікроконтролер. Для даного проекта застосовується мікроконтролер 89С51, загальний вигляд та призначення ніжок якого показано на рис.2.2.

Мікроконтролер

має чотири порти вводу-виводу Р0-Р3. Порт

Р0 мікроконтролера 89С51 використовується,

як шина даних (коли сигнал ALE=0) і шина

адресів від А0 до А7 (коли сигнал ALE=1).

Порт Р3 використовується як порт, який

видає сигнали керування мікроконтролером.

Сигнали керування, які ідуть від порту

Р3, наведені на рис.2.2.

Опис сигналів керування наведено в

табл.3.1.

Кожний порт може видавати сигнали

керування.

Мікроконтролер

має чотири порти вводу-виводу Р0-Р3. Порт

Р0 мікроконтролера 89С51 використовується,

як шина даних (коли сигнал ALE=0) і шина

адресів від А0 до А7 (коли сигнал ALE=1).

Порт Р3 використовується як порт, який

видає сигнали керування мікроконтролером.

Сигнали керування, які ідуть від порту

Р3, наведені на рис.2.2.

Опис сигналів керування наведено в

табл.3.1.

Кожний порт може видавати сигнали

керування.

Пам’ять у мікроконтролері поділяється на внутрішню пам’ять програм та даних та зовнішню пам’ять програм да даних.

Зовнішня пам’ять програм та даних поділяється на постійну зовнішню пам’ять програм (ПЗП), де знаходяться коди операцій, та зовнішню пам’ять даних (ОЗП), де знаходяться проміжні результати розрахунків. Звернення до ПЗП здійснюється за допомогою керуючого сигналу /PSEN, який виконує функцію строб-сигналу читання. Код команди вибирається із ПЗП при встановленні на /PSEN сигналу рівного логічному 0. Звернення (читання або запис) до ОЗП забезпечується керуючими сигналами /RD або /WR, які формуються на лініях Р3.7 та Р3.6 при виконанні відповідних операцій переміщення даних та команд керування процесором. Звернення до ОЗП здійснюється при встановленні на /RD або /WR сигналів логічного 0. Для того, щоб одночасно читати коди команд із ПЗП та дані із ОЗП сигнали /PSEN та /RD об’єднують в один сигнал /PSEN*/RD.

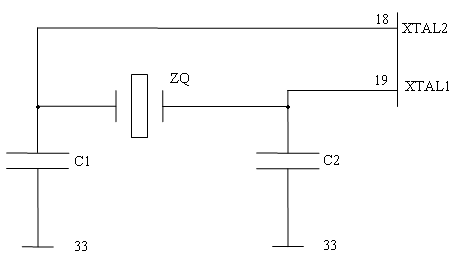

Рис.2.3. Схема генератора тактових імпульсів для мікроконтролера 89С51

До ніжок XTL2, XTL1 МК-51 підєднується генератор синхроімпульсів який зображений на малюнку 2.3. Цей кварцовий генератор виробляє імпульси із частотою 12Мгц і 24Мгц, оскільки цикл виконується однієї команди сладає 12 тактів, то виконання однієї команди займає одну мікросекунду, при частоті 12Мгц і 0.5 мікросекунди при частоті 24Мгц.

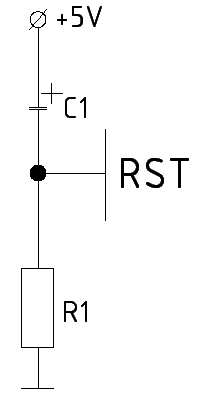

Схема скиду МК на нульовий адрес показана на рис 2.4.

Рис 2.4. Схема скиду МК

С1 - К50-35-10,0х6,3V , R1 – 8,2кОм