- •Вычислительные машины, системы и сети

- •Оглавление

- •Введение

- •Раздел 1. Центральный процессор

- •1.1. Архитектура центрального процессора

- •1.2. Организация памяти и способы адресации

- •1.3. Общая характеристика системы команд

- •1.4. Команды пересылки данных

- •1.5. Арифметические команды

- •1.6. Сдвиги и логические команды

- •1.7. Команды обработки строк данных

- •1.8. Команды передачи управления

- •1.9. Команды управления процессором

- •Раздел 2. Арифметический процессор

- •2.1. Архитектура арифметического процессора

- •2.2. Программная модель арифметического процессора

- •2.3. Система команд арифметического процессора

- •Раздел 3. Эволюция характеристик цп

- •3.1. Архитектура цп Pentium

- •3.2. Программная модель цп Pentium

- •3.3. Система команд ммх-расширения

- •3.4. Система команд sse-расширения

- •Раздел 4. Системные устройства вм

- •4.1. Программируемый контроллер прерываний

- •4.2. Программируемый контроллер пдп

- •4.3. Системный таймер

- •4.4. Системные регистры

- •Раздел 5. Защищенный режим работы вм

- •5.1. Максимальный режим работы цп

- •5.2. Дескрипторы и шлюзы

- •Контрольные вопросы

- •Раздел 6. Язык ассемблера

- •6.1. Программирование на языке ассемблера

- •6.2. Директивы языка ассемблера asm-86

- •6.3. Использование регистров Pentium

- •6.4. Директивы языка ассемблера asm-89

- •6.5. Модели программ, компиляция и отладка

- •Контрольные вопросы

- •Раздел 7. Специфика вычислительных систем

- •7.1. Мультипроцессорные системы

- •7.2. Управление процессами

- •7.3. Семафорные операции

- •7.4. Разделение общих процедур

- •7.5. Управление памятью

- •Контрольные вопросы

- •Раздел 8. Специализированные процессоры и вм

- •8.1. Процессор ввода-вывода

- •8.2. Программная модель процессора ввода-вывода

- •8.3. Система команд процессора ввода-вывода

- •8.4. Процессор операционной системы

- •Контрольные вопросы

- •Раздел 9. Назначение и топология сетей

- •9.1. Особенности и назначение сетей различных типов

- •Топология «звезда».

- •9.2. Кодирование информации

- •9.3. Назначение и структура пакетов

- •9.4. Методы управления обменом

- •9.5. Эталонные модели

- •Контрольные вопросы

- •Раздел 10. Практическая реализация сетей

- •10.1. Адресация в сетях

- •10.2. Основные службы Internet

- •10.3. Особенности web-дизайна

- •10.4. Особенности и тенденции развития Internet

- •Контрольные вопросы

- •Глоссарий

- •Литература

Раздел 3. Эволюция характеристик цп

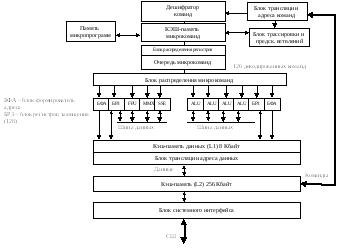

3.1. Архитектура цп Pentium

Эволюция центральных процессоров Intel – от первого 16-разрядного Intel 8086 до Pentium IV – составила значительное число шагов. Основные вехи этой эволюции отражены в табл. 3.1. Первой существенной вехой явилось расширение разрядности внутренних регистров ЦП с 16 до 32 и увеличение адресного пространства до 4 Гбайт при переходе к ЦП Intel 80386. Немаловажным явилось событие в размещении на одном кристалле ЦП и АП, а также появление внутренней кэш-памяти у ЦП Intel 80486.

Кэш первого уровня процессора Intel 80486 имеет четырехканальную структуру (рис. 3.1). Каждый канал состоит из 128 строк по 16 байт в каждой. Одноименные строки всех четырех каналов образуют 128 наборов из четырех строк, каждый из которых обслуживает свои адреса памяти. Каждой строке соответствует 21-разрядная информация об адресе скопированного в нее блока системной памяти. Эта информация называется тегом (tag) строки.

Рис. 3.1. Структура внутреннего кэша ЦП Intel 80486

Кроме того, в состав кэша входит так называемый диспетчер, то есть область памяти с организацией 128 х 7, в которой хранятся 4-битные теги действительности (достоверности) для каждого из 128 наборов и 3-битные коды LRU (Least Recently Used) для каждого из 128 наборов. Тег действительности набора включает в себя 4 бита достоверности каждой из 4 строк, входящих в данный набор. Бит достоверности, установленный в единицу, говорит о том, что соответствующая строка заполнена; если он сброшен в нуль, то строка пуста. Биты LRU говорят о том, как давно было обращение к данному набору. Это нужно для того, чтобы обновлять наименее используемые наборы.

Адресация кэш-памяти осуществляется с помощью 28 разрядов адреса. Из них 7 младших разрядов выбирают один из 128 наборов, а 21 старший разряд сравнивается с тегами всех 4 строк выбранного набора. Если теги совпадают с разрядами адреса, то получается ситуация кэш-попадания, а если нет, то ситуация кэш-промаха.

В случае цикла чтения при кэш-попадании байт или слово читаются из кэш-памяти. При кэш-промахе происходит обновление (перезагрузка) одной из строк кэш-памяти. В случае цикла записи при кэш-попадании производится запись как в кэш-память, так и в основную системную память. При кэш-промахе запись производится только в системную память, а обновление строки кэш-памяти не производится. Эта строка становится недостоверной (ее бит достоверности сбрасывается в нуль).

Такая политика записи называется сквозной или прямой записью (Write Through). В более поздних моделях процессоров применяется и обратная запись (Write Back), которая является более быстрой, так как требует гораздо меньшего числа обращений по внешней шине. При использовании обратной записи в основную память записываемая информация отправляется только в том случае, когда нужной строки в кэше нет. В случае же попадания модифицируется только кэш. В основную память измененная информация попадет только при перезаписи новой строки в кэш. Прежняя строка при этом целиком переписывается в основную память, и тем самым восстанавливается идентичность содержимого кэша и основной памяти.

В случае, когда требуемая строка в кэше не представлена (ситуация кэш-промаха), запрос на запись направляется на внешнюю шину, а запрос на чтение обрабатывается несколько сложнее. Если этот запрос относится к кэшируемой области памяти, то выполняется цикл заполнения целой строки кэша (16 байт из памяти переписывается в одну из строк набора, обслуживающего данный адрес). Если затребованные данные не укладываются в одной строке, то заполняется и соседняя строка.

Внутренний запрос процессора на данные удовлетворяется сразу, как только данные считываются из памяти, а дальнейшее заполнение строки может идти параллельно с обработкой данных. Если в наборе, который обслуживает данный адрес памяти, имеется свободная строка, заполнена будет именно она. Если же свободных строк нет, заполняется строка, к которой дольше всех не обращались. Для этого используются биты LRU, которые модифицируются при каждом обращении к строке данного набора. Кроме того, существует возможность аннулирования строк (объявления их недостоверными) и очистки всей кэш-памяти. При сквозной записи очистка кэша проводится специальным внешним сигналом процессора, программным образом с помощью специальных команд, а также при начальном сбросе – по сигналу RESET. При обратной записи очистка кэша подразумевает также выгрузку всех модифицированных строк в основную память.

Появление процессора Pentium MMX (Multi Media Extension), существенно расширило систему команд ЦП, введением специальных команд для нужд мультимедийных приложений. Этот процессор положил начало новой технологии обработки данных – SIMD (Single Instruction Multiply Data), при которой одна команда обрабатывает параллельно несколько данных.

Выпуск процессора Pentium III, также добавил большое число новых команд для потоковой обработки чисел с плавающей запятой. Эта новация носит название SSE (Streaming SIMD Extention) – потоковое SIMD расширение.

Наконец, большие успехи в технологии изготовления кристаллов микросхем позволили практически на порядок повысить их сложность, благодаря чему появился процессор Pentium IV, обладающей внутренней двухуровневой КЭШ памятью и достигшему в настоящее время огромного быстродействия, превышающего 3 ГГц.

Таблица 3.1

|

Модель |

Год

|

Млн. тр-ров |

Ч-та (Мгц) |

Регистры (бит) |

ШД (бит) |

Адреса (Гбайт) |

КЭШ (Кбайт) |

|

Intel 8086 |

1978 |

0.029 |

8 |

16 |

16 |

0.001 |

Нет |

|

Intel 386 |

1985 |

0.275 |

40 |

32 |

32 |

4 |

Нет |

|

Intel 486 |

1989 |

1.2 |

100 |

32 |

32 |

4 |

8 + 8 |

|

Pentium |

1993 |

3.1 |

200 |

32 |

64 |

4 |

8 + 8 |

|

Pentium Pro |

1995 |

5.5 |

200 |

32 |

64 |

64 |

8 + 8 |

|

Pentium MMX |

1997, янв |

6.5 |

233 |

32 / 64 |

64 |

64 |

8 + 8 |

|

Pentium II (Xeon) |

1997, май |

7.5 |

450 |

32 / 64 |

64 |

64 |

16 + 16 |

|

Celeron |

1998 |

7.5 |

750 |

32 / 64 |

64 |

64 |

128 |

|

Pentium III |

1999 |

8.5 |

1000 |

32 / 64 / 128 |

64 |

64 |

16 + 16 |

|

Pentium IV |

2000 |

42.0 |

2000 |

32 / 64 / 128 |

64 |

64 |

256 / 12 / 8 |

Совокупность технических решений, применённых в процессоре Pentium IV, получила собственное название: «архитектура NetBurst (пакетно-сетевая)». Архитектура процессора Pentuim IV представлена на рис. 3.2.

Основные особенности архитектуры NetBurst.

Для того, чтобы ЦП

могли работать на частотах порядка

нескольких ГГц Intel увеличил длину

конвейера Pentium IV

до 20 стадий (Hyper Pipelined Technology) - для сравнения

– длина конвейера Pentium III составляет 10

стадий. Чего же достиг Intel, так удлинив

конвейер? Благодаря декомпозиции

выполнения каждой команды на более

мелкие этапы, каждый из этих этапов

теперь может выполняться быстрее, что

позволяет увеличивать частоту процессора.

Так, если при используемом технологическом

процессе 0.18 мкм предельная частота для

Pentium III составляет 1 ГГц, то Pentium IV

мог достигнуть частоты в 2 ГГц. Однако

у чрезмерно длинного конвейера есть и

свои недостатки. Первый недостаток -

каждая команда, проходя большее число

стадий, выполняется дольше.

![]() Второй

недостаток длинного конвейера вскрывается

при ошибках в предсказании переходов.

Второй

недостаток длинного конвейера вскрывается

при ошибках в предсказании переходов.

Из-за такого увеличения длины конвейера время выполнения одной команды в процессорных тактах также увеличивается. Поэтому компания осуществила модернизацию алгоритмов предсказания переходов.

Advanced Dynamic Execution - осуществляет минимизацию простоя процессора при неправильном предсказании переходов и увеличение вероятности правильных предсказаний. Для этого Intel улучшил блок выборки инструкций для внеочередного выполнения и повысил правильность предсказания переходов. Правда, для этого алгоритмы предсказания переходов были доработаны минимально, основным же средством для достижения цели было выбрано увеличение размеров буферов, с которыми работают соответствующие блоки процессора. Количество предварительно загружаемых инструкций увеличилось до 126 по сравнению с 48 у Pentium III. Буфер, хранящий адреса условных переходов, также увеличился с 512 байт до 4 КБ. Все это позволило увеличить вероятность правильного предсказания переходов на 33%.

Рис. 3.2. Архитектура процессора Pentium IV

Для ускорения работы целочисленных операций в Pentium IV применена технология удвоения внутренней тактовой частоты (Rapid Execution Engine). Два блока АЛУ, выполняющие операции над целочисленными данными, работают на частоте вдвое большей, чем частота самого процессора. Таким образом, например, в Pentium IV с частотой 1.4 ГГц АЛУ работает на частоте 2.8 ГГц. В АЛУ исполняются простые целочисленные инструкции, поэтому, производительность нового процессора при операциях с целыми числами очень высока. Однако, на производительности Pentium IV при операциях с вещественными числами, MMX или SSE двукратное ускорение АЛУ никак не сказывается.

Кэш 1-го уровня в процессоре также претерпел значительные изменения. В отличие от Pentium III, кэш которого мог хранить команды и данные, Pentium IV имеет всего 8 КБ кэш данных. Команды, поступающие на исполнение процессору, сохраняются в так называемом Trace Cach (кэш-память микрокоманд). Там они хранятся уже в декодированном виде, т.е. в виде последовательности микроопераций, поступающих для выполнения в исполнительные устройства процессора. Емкость этого кэша составляет 12000 микроопераций и по сравнению с обычным L1-кэшем он имеет много преимуществ, направленных на минимизацию простоев процессора при выполнении неправильных предсказаний переходов.

Особенностью новых процессоров Pentium IV является расширение набора команд командами SSE2. К 70-ти командам SSE, работающим с потоковыми данными одинарной точности добавились 144 команды для работы с вещественными числами двойной точности, а также с целыми числами длиной от одного до восьми байт. Дальнейшее расширение – командами SSE3, добавившее еще 13 новых команд. Наконец, заявленное расширение SSE4 еще на несколько десятков команд.