- •А.Л. Ахтулов, л.Н. Ахтулова, с.И. Смирнов основы микропроцессорной техники

- •Содержание

- •Глава 1. Структура, архитектура и функционирование Электонных Вычислительных Машин и микропроцессорных систем

- •1.1. История развития информации и вычислительной техники

- •1.2. Этапы развития электронно-вычислительной техники

- •1.3. Классическая архитектура электронной вычислительной машины и принципы фон Неймана

- •1.4. Архитектура мини-эвм и микропроцессора

- •1.5. Принцип работы микро-эвм

- •Глава 2. Числа, кодирование и арифметические операции

- •2.1. Арифметические основы микропроцессорной техники

- •2.2. Двоичная арифметика

- •2.3. Дополнительный код

- •2.4. Арифметика в дополнительном коде

- •2.5. Группировка бит

- •2.6. Буквенно-цифровой код

- •Глава 3. Основные элементы микропроцессорной техники

- •3.1. Логические элементы

- •3.2. Электронные логические вентили

- •3.3. Комбинации логических элементов

- •3.4. Практическая реализация логических вентилей

- •3.5. Задержка на распространение сигнала

- •3.6. Ограничения по входу и выходу

- •3.7. Тристабильные элементы

- •3.8. Мультиплексор и демультиплексоры

- •3.9. Дешифраторы

- •3.10. Модули интегральных микросхем

- •3.11. Триггеры и защелки

- •3.12. Тактирование фронтом сигнала

- •3.15. Триггеры с дополнительными входами для установки и очистки

- •3.16. Регистры и сдвиговые регистры

- •3.17. Счетчики

- •Глава 4. Программируемые логические устройства

- •4.1. Программируемая логическая матрица

- •4.2. Программируемая матричная логика

- •4.3. Сложные программируемые логические устройства

- •4.4. Программируемые вентильные матрицы

- •4.5. Пример счетчика с прямым/обратным счетом

- •4.6. Временные диаграммы

- •4.7. Модель конечного автомата

- •4.8. Синтез конечных автоматов

- •Глава 5. Полупроводниковая память

- •5.1. Микросхемы rom

- •5.2. Затенение rom

- •5.3. Прожигаемая при изготовлении память rom

- •4.4. Память prom

- •5.5. Память eprom

- •5.6. Системная память

- •5.7. Быстродействие озу

- •5.8. Динамическая и статическая память

- •5.9. Память типа dram

- •5.10. Статическая память

- •5.13. Подсистема памяти

- •5.14. Организация кэш-памяти

- •5.15. Принципы организации основной памяти в современных компьютерах

- •5.16. Виртуальная память и организация защиты памяти

- •5.17. Модули памяти

- •5.18. Использование оперативной и постоянной памяти

- •Глава 6. Основы микропроцессорной техники

- •6.1. Архитектура простой микро-эвм

- •6.2. Структура простейшей памяти

- •6.3. Состав команд

- •6.4. Структура элементарного микропроцессора

- •6.5. Функционирование микро-эвм

- •6.9. Код коррекции ошибок

- •Глава 7. Микропроцессорная система

- •7.1. Классификация

- •7.2. Определение понятия микропроцессор

- •7.3. Основные характеристики микропроцессора

- •7.4. Шинная структура связей

- •7.5. Логическая структура микропроцессора

- •7.6. Режимы работы микропроцессорной системы

- •7.7. Архитектура микропроцессорных систем

- •7.8. Типы микропроцессорных систем

- •Глава 8. Организация обмена информацией

- •8.1. Циклы обмена микропроцессорной системы

- •8.2. Шины микропроцессорной системы

- •8.3. Организация циклов обмена информацией

- •8.4. Прохождение сигналов по магистрали

- •8.5. Функции устройств магистрали

- •Глава 9. Функционирование процессора

- •9.1. Адресация операндов

- •9.2. Регистры процессора

- •9.3. Система команд процессора

- •Глава 10. Организация микроконтроллеров

- •10.1. Процессорное ядро и память микроконтроллеров

- •10.2. Классификация и структура микроконтроллеров

- •10.3. Система команд процессора мк

- •10.4. Схема синхронизации мк

- •10.5. Память программ и данных мк

- •10.6. Порты ввода/вывода

- •Библиографический список

- •Основы микропроцессорной техники

- •Издательство государственного образовательного учреждения высшего профессионального образования

- •625000, Тюмень, ул. Володарского, 38

- •6 25039, Г. Тюмень, ул. Киевская, 52

2.2. Двоичная арифметика

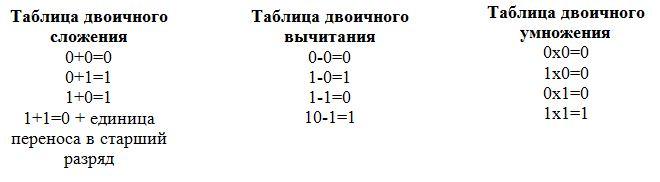

Сложение, вычитание или умножение двоичных чисел (рис.2.4) выполняются так же, как и в арифметике десятичных чисел.

а)

б)

Рис. 2.4. Двоичная арифметика: а — правила; б — примеры

Правила выполнения арифметических действий над двоичными числами можно задать таблицами сложения вычитания и умножения (рис.2.4, а).

На рис. 2.4, а (слева) представлены простые правила двоичного сложения. Два первых (слева) правила очевидны, третье показывает, что 1 + 1 = 10, т.е. наиболее значимая 1 переносится в ближайший старший разряд.

Четвертое правило, наконец, показывает, что 1 + 1 + 1 = 11. В этом случае первое, второе слагаемые и запоминаемое в результате сложения в младшем разряде число — все 1. Результатом - является сумма—1 с переносом 1.

Сложим двоичные числа 0011 1011 и 0010 1010 (операция показана на рис. 2.4,6). Для большей ясности действия с десятичными эквивалентами обрабатываемых чисел показаны на рисунке 2.5.

Рис. 2.5. Двоичное сложение: а — правила; б — пример

Суммой двух чисел 0011 1011 и 0010 1010 будет 0110 01012.

На рис. 2.4, б и 2.6, а приведены правила двоичного вычитания. Первые три аналогичны десятичному вычитанию. Последнее требует заема из более значимого предшествующего разряда (в этом случае вес 2). Уменьшаемым является двоичное число 10, вычитаемым 1, разностью - 1.

Вычтем двоичное число 0011 1001 из 0101 0101. Этот пример приведен на рис. 2.6,6. Разряды весов 1, 2 и 4 этого двоичного вычитания просты для выполнения и относятся к первым трём правилам на рис. 2.4, б. В колонке веса: 8 имеет место вычитание 1 из 0. Тогда 1 занимается из колонки веса 16. Единиц вычитается из 102, что дает разность 1 согласно четвертому правилу на рис. 2.6, а.

Рис. 2.6. Двоичное вычитание: а — правила; б — пример

После этого заема в колонке веса 16 имеет место вычитание 1 из нового вычитаемого 0. Согласно четвертому правилу 1 должна быть занята из следующей, более значимой позиции (колонка веса 32), но в колонке 32 имеем 0; поэтому колонка 32 должна сделать заем из колонки веса 64, что и выполнено. Окончательно колонка 16 делает заем из колонки 32, уменьшаемым в коленке 16 становится 102, вычитаемым 1, разностью 1. В колонке 32 имеем 1—1=0, в колонке 64 —0—0=0, в колонке 28 — 0—0=0. Таким образом, рис. 2.5,6 иллюстрирует операцию вычитания 10012 из 0101 01012 (справа эта задача решена в десятичной записи).

Приведем правила десятичного умножения:

Множимые 0 1 0 1

× × × ×

Множители 0 0 1 1

Произведения 0 0 0 1

Два первых правила не требуют никаких пояснений. В двух следующих множителем является 1: когда множителем является 1 при двоичном умножении, множимое становится результатом и представляет собой произведение. Когда множитель 0, произведение всегда 0.

Выполним умножение 1101 на 101. Как и в случае умножения десятичных чисел, множимое сначала умножается на число, стоящее в младшем разряде (в рассматриваемом случае — бит в колонке веса).

Множимое 1101 13

× ×

Множитель 101 5_

1-е частичное произведение 1101 6510

2-е частичное произведение 0000

3-е частичное произведение 1101

Конечное произведение 10000012

Поскольку бит множителя в разряде веса 1 является 1, множимое копируется и составляет первое частичное произведение. Вторым битом множителя является 0, тогда второе частичное произведение есть 0000 (заметим, что оно, сдвинуто на одну позицию влево). Битом разряда веса 4; множителя является 1, тогда для получения третьего частичного произведения снова следует копирование множимого (заметим, что копирование завершается новым сдвигом на одну позицию влево). После этого выполняем сложение трех частичных произведений что дает результат 10000012. Полученный результат 11012 1012 = 10000012 соответствует произведению десятичных чисел 13 10×5 10 = 6510.

Большинство микропроцессоров владеет командами сложения и вычитания двоичных чисел, однако некоторые, менее многочисленные выполняют команды умножения и деления.