- •А.Л. Ахтулов, л.Н. Ахтулова, с.И. Смирнов основы микропроцессорной техники

- •Содержание

- •Глава 1. Структура, архитектура и функционирование Электонных Вычислительных Машин и микропроцессорных систем

- •1.1. История развития информации и вычислительной техники

- •1.2. Этапы развития электронно-вычислительной техники

- •1.3. Классическая архитектура электронной вычислительной машины и принципы фон Неймана

- •1.4. Архитектура мини-эвм и микропроцессора

- •1.5. Принцип работы микро-эвм

- •Глава 2. Числа, кодирование и арифметические операции

- •2.1. Арифметические основы микропроцессорной техники

- •2.2. Двоичная арифметика

- •2.3. Дополнительный код

- •2.4. Арифметика в дополнительном коде

- •2.5. Группировка бит

- •2.6. Буквенно-цифровой код

- •Глава 3. Основные элементы микропроцессорной техники

- •3.1. Логические элементы

- •3.2. Электронные логические вентили

- •3.3. Комбинации логических элементов

- •3.4. Практическая реализация логических вентилей

- •3.5. Задержка на распространение сигнала

- •3.6. Ограничения по входу и выходу

- •3.7. Тристабильные элементы

- •3.8. Мультиплексор и демультиплексоры

- •3.9. Дешифраторы

- •3.10. Модули интегральных микросхем

- •3.11. Триггеры и защелки

- •3.12. Тактирование фронтом сигнала

- •3.15. Триггеры с дополнительными входами для установки и очистки

- •3.16. Регистры и сдвиговые регистры

- •3.17. Счетчики

- •Глава 4. Программируемые логические устройства

- •4.1. Программируемая логическая матрица

- •4.2. Программируемая матричная логика

- •4.3. Сложные программируемые логические устройства

- •4.4. Программируемые вентильные матрицы

- •4.5. Пример счетчика с прямым/обратным счетом

- •4.6. Временные диаграммы

- •4.7. Модель конечного автомата

- •4.8. Синтез конечных автоматов

- •Глава 5. Полупроводниковая память

- •5.1. Микросхемы rom

- •5.2. Затенение rom

- •5.3. Прожигаемая при изготовлении память rom

- •4.4. Память prom

- •5.5. Память eprom

- •5.6. Системная память

- •5.7. Быстродействие озу

- •5.8. Динамическая и статическая память

- •5.9. Память типа dram

- •5.10. Статическая память

- •5.13. Подсистема памяти

- •5.14. Организация кэш-памяти

- •5.15. Принципы организации основной памяти в современных компьютерах

- •5.16. Виртуальная память и организация защиты памяти

- •5.17. Модули памяти

- •5.18. Использование оперативной и постоянной памяти

- •Глава 6. Основы микропроцессорной техники

- •6.1. Архитектура простой микро-эвм

- •6.2. Структура простейшей памяти

- •6.3. Состав команд

- •6.4. Структура элементарного микропроцессора

- •6.5. Функционирование микро-эвм

- •6.9. Код коррекции ошибок

- •Глава 7. Микропроцессорная система

- •7.1. Классификация

- •7.2. Определение понятия микропроцессор

- •7.3. Основные характеристики микропроцессора

- •7.4. Шинная структура связей

- •7.5. Логическая структура микропроцессора

- •7.6. Режимы работы микропроцессорной системы

- •7.7. Архитектура микропроцессорных систем

- •7.8. Типы микропроцессорных систем

- •Глава 8. Организация обмена информацией

- •8.1. Циклы обмена микропроцессорной системы

- •8.2. Шины микропроцессорной системы

- •8.3. Организация циклов обмена информацией

- •8.4. Прохождение сигналов по магистрали

- •8.5. Функции устройств магистрали

- •Глава 9. Функционирование процессора

- •9.1. Адресация операндов

- •9.2. Регистры процессора

- •9.3. Система команд процессора

- •Глава 10. Организация микроконтроллеров

- •10.1. Процессорное ядро и память микроконтроллеров

- •10.2. Классификация и структура микроконтроллеров

- •10.3. Система команд процессора мк

- •10.4. Схема синхронизации мк

- •10.5. Память программ и данных мк

- •10.6. Порты ввода/вывода

- •Библиографический список

- •Основы микропроцессорной техники

- •Издательство государственного образовательного учреждения высшего профессионального образования

- •625000, Тюмень, ул. Володарского, 38

- •6 25039, Г. Тюмень, ул. Киевская, 52

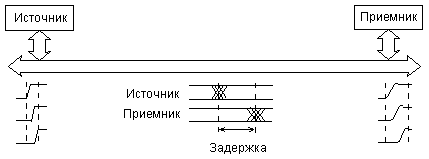

8.4. Прохождение сигналов по магистрали

При организации обмена по магистралям и шинам разработчику необходимо учитывать несколько важных моментов, связанных как с особенностью распространения сигналов по шинам, так и с самой природой шин. В противном случае микропроцессорная система может попросту не работать или работать неустойчиво, хотя вся логика цифровых устройств, входящих в систему, будет спроектирована безошибочно.

В случае, когда системная шина (магистраль) микропроцессорной системы является внешней, а не скрыта внутри микросхемы, необходимо учитывать особенности распространения сигналов по длинным линиям. Хотя в большинстве случаев длина магистрали не слишком велика, не превышает 1—2 десятков сантиметров, это все равно оказывает большое влияние на синхронизацию обмена.

На прохождение сигналов по магистрали влияют следующие факторы:

-

конечная величина задержки распространения сигналов по линиям магистрали;

-

различие задержек распространения сигналов по разным линиям шины;

-

неодновременное выставление сигналов на линии шины;

-

искажение фронтов сигналов, проходящих по линиям магистрали;

-

отражение сигналов от концов линий связи (рис. 8.14).

Рис. 8.14. Прохождение сигналов по шине

Для учета всех этих факторов разработчики стандартных магистралей обмена и стандартных протоколов обмена всегда закладывают необходимые задержки между сигналами, участвующими в обмене. Кроме того, задержки между сигналами выбираются таким образом, чтобы устройство, которому адресован тот или иной сигнал, имело достаточно времени для его обработки. Если разрабатывается новая магистраль, все это тоже надо учитывать.

Поэтому пытаться «модернизировать» какой-то стандартный протокол и ускорять обмен по магистрали путем уменьшения задержек, предусмотренных стандартом, очень опасно. Точно так же опасно, не изменяя протокола обмена, пытаться увеличить длину магистрали, увеличивая тем самым задержки распространения сигналов по линиям и шинам. Особенно чувствительны к такого рода «модернизациям» синхронные магистрали, в которых не предусмотрено обязательное подтверждение выполнения каждой операции.

Например, длительность фазы адреса в цикле обмена выбирается таким образом. В течение адресной фазы все сигналы всех разрядов кода адреса, пусть даже и сформированные процессором не одновременно, должны дойти до устройства-исполнителя по своим проводам шины. А устройство-исполнитель должно этот код адреса принять и обработать (то есть отличить свой адрес от чужого). Естественно, для гарантии в длительность адресной фазы еще добавляется небольшая дополнительная задержка.

Точно так же длительность фазы данных в цикле чтения должна выбираться такой, чтобы устройство-исполнитель успело получить строб чтения и выдать код читаемых данных на шину данных. Затем этот код должен успеть дойти до процессора и процессор должен успеть его прочитать. После чего процессор снимает сигнал строба чтения, этот задний фронт сигнала доходит с задержкой до устройства-исполнителя, которое также с задержкой снимает свой код данных. Аналогично и в цикле записи.

Для улучшения формы сигналов, распространяющихся по магистрали, иногда применяют оконечные согласователи (терминаторы) на концах линий магистрали. Особенно важно их применение в случае, когда допустимая длина магистрали превышает несколько метров. Например, в случае магистрали Q-bus применяются два типа согласователей: 120-омный и 250-омный (рис. 8.15).

Рис. 8.15. Оконечные согласователи на магистрали Q-bus

Включение согласователей предъявляет дополнительные требования к нагрузочной способности передатчиков, работающих на линии магистрали. В магистрали ISA подобные согласователи не используются, хотя к некоторым линиям присоединены резисторы, соединенные другим своим выводом с шиной питания (прежде всего это линии, тип выходного каскада для которых — ОК).

В любом случае выходные каскады передатчиков, работающих на линии магистрали, должны обеспечивать высокие выходные токи, так как к магистрали может подключаться несколько устройств, каждое из которых потребляет входной ток. Типичные величины требуемых выходных токов магистральных передатчиков находятся в пределах 20—30 мА. В то же время входные токи магистральных приемников должны быть малыми, чтобы не перегружать передатчики. Типичные величины допустимых входных токов магистральных приемников лежат в пределах 0,2—0,8 мА.