- •А.Л. Ахтулов, л.Н. Ахтулова, с.И. Смирнов основы микропроцессорной техники

- •Содержание

- •Глава 1. Структура, архитектура и функционирование Электонных Вычислительных Машин и микропроцессорных систем

- •1.1. История развития информации и вычислительной техники

- •1.2. Этапы развития электронно-вычислительной техники

- •1.3. Классическая архитектура электронной вычислительной машины и принципы фон Неймана

- •1.4. Архитектура мини-эвм и микропроцессора

- •1.5. Принцип работы микро-эвм

- •Глава 2. Числа, кодирование и арифметические операции

- •2.1. Арифметические основы микропроцессорной техники

- •2.2. Двоичная арифметика

- •2.3. Дополнительный код

- •2.4. Арифметика в дополнительном коде

- •2.5. Группировка бит

- •2.6. Буквенно-цифровой код

- •Глава 3. Основные элементы микропроцессорной техники

- •3.1. Логические элементы

- •3.2. Электронные логические вентили

- •3.3. Комбинации логических элементов

- •3.4. Практическая реализация логических вентилей

- •3.5. Задержка на распространение сигнала

- •3.6. Ограничения по входу и выходу

- •3.7. Тристабильные элементы

- •3.8. Мультиплексор и демультиплексоры

- •3.9. Дешифраторы

- •3.10. Модули интегральных микросхем

- •3.11. Триггеры и защелки

- •3.12. Тактирование фронтом сигнала

- •3.15. Триггеры с дополнительными входами для установки и очистки

- •3.16. Регистры и сдвиговые регистры

- •3.17. Счетчики

- •Глава 4. Программируемые логические устройства

- •4.1. Программируемая логическая матрица

- •4.2. Программируемая матричная логика

- •4.3. Сложные программируемые логические устройства

- •4.4. Программируемые вентильные матрицы

- •4.5. Пример счетчика с прямым/обратным счетом

- •4.6. Временные диаграммы

- •4.7. Модель конечного автомата

- •4.8. Синтез конечных автоматов

- •Глава 5. Полупроводниковая память

- •5.1. Микросхемы rom

- •5.2. Затенение rom

- •5.3. Прожигаемая при изготовлении память rom

- •4.4. Память prom

- •5.5. Память eprom

- •5.6. Системная память

- •5.7. Быстродействие озу

- •5.8. Динамическая и статическая память

- •5.9. Память типа dram

- •5.10. Статическая память

- •5.13. Подсистема памяти

- •5.14. Организация кэш-памяти

- •5.15. Принципы организации основной памяти в современных компьютерах

- •5.16. Виртуальная память и организация защиты памяти

- •5.17. Модули памяти

- •5.18. Использование оперативной и постоянной памяти

- •Глава 6. Основы микропроцессорной техники

- •6.1. Архитектура простой микро-эвм

- •6.2. Структура простейшей памяти

- •6.3. Состав команд

- •6.4. Структура элементарного микропроцессора

- •6.5. Функционирование микро-эвм

- •6.9. Код коррекции ошибок

- •Глава 7. Микропроцессорная система

- •7.1. Классификация

- •7.2. Определение понятия микропроцессор

- •7.3. Основные характеристики микропроцессора

- •7.4. Шинная структура связей

- •7.5. Логическая структура микропроцессора

- •7.6. Режимы работы микропроцессорной системы

- •7.7. Архитектура микропроцессорных систем

- •7.8. Типы микропроцессорных систем

- •Глава 8. Организация обмена информацией

- •8.1. Циклы обмена микропроцессорной системы

- •8.2. Шины микропроцессорной системы

- •8.3. Организация циклов обмена информацией

- •8.4. Прохождение сигналов по магистрали

- •8.5. Функции устройств магистрали

- •Глава 9. Функционирование процессора

- •9.1. Адресация операндов

- •9.2. Регистры процессора

- •9.3. Система команд процессора

- •Глава 10. Организация микроконтроллеров

- •10.1. Процессорное ядро и память микроконтроллеров

- •10.2. Классификация и структура микроконтроллеров

- •10.3. Система команд процессора мк

- •10.4. Схема синхронизации мк

- •10.5. Память программ и данных мк

- •10.6. Порты ввода/вывода

- •Библиографический список

- •Основы микропроцессорной техники

- •Издательство государственного образовательного учреждения высшего профессионального образования

- •625000, Тюмень, ул. Володарского, 38

- •6 25039, Г. Тюмень, ул. Киевская, 52

4.8. Синтез конечных автоматов

Теперь давайте подытожим сказанное и определим общую последовательность создания представленной на рис. 4.11 синхронной схемы, в основу которой положена диаграмма состояний, показанная на рис. 4.8. Процесс можно разбить на следующие ключевые этапы.

-

Составление диаграммы или таблицы состояний.

-

Определение количества и выбор подходящего типа триггеров.

-

Определение значений, которые будут храниться в триггерах по каждому из состояний, указанных в диаграмме состояний (этот этап называется назначением состояний).

-

Составление таблицы состояний.

-

Составление таблицы истинности для блока комбинаторной логики.

-

Разработка схемы реализации блока комбинаторной логики.

Пример

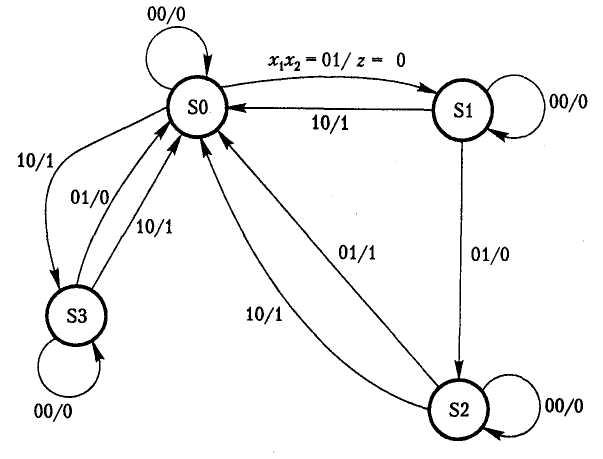

В качестве еще одного примера конечного автомата со входами и выходами будет рассмотрен торговый автомат, принимающий монеты и выдающий некоторый товар. Для того чтобы упростить изложение, предположим, что этот автомат принимает только монеты достоинством 25 и 10 центов. Автомат принимает монеты до пор, пока не получится сумма в 30 или более центов, после чего выдает товар.

Причем, получив больше 30 центов, автомат сдачи не дает. Пусть опускаемые в автомат монеты представляют две двоичные переменные, x1 и х2. Монете достоинством в 25 центов соответствует значение х1 = 1 (х2 = 0), а монете достоинством в 10 центов — значение х2 = 1 (x1 = 0). Монеты опускаются по одной, так что комбинации x1х2 = 11 быть не может. Пусть двоичная выходная переменная z обозначает выдачу автоматом товара, то есть z = 0, когда товар не выдается, и z = 1 в противном случае При синтезе логической схемы такого автомата первым делом нужно построить диаграмму или составить таблицу состояний. Имеет смысл для каждого из состояний составить словесное описание, чтобы позднее легче было определить, сколько триггеров потребуется для представления нужного количества состояний. Состояния определяют общую сумму денег, опущенных в автомат на данный момент. Поскольку монеты могут опускаться в любом порядке до тех пор, пока их общая сумма не составит или не превысит 30 центов, нам потребуются следующие четыре состояния:

♦ S0 — ничего не опущено (начальное состояние);

-

S1 — 10 центов;

-

S2 - 20 центов;

-

S3 - 25 центов.

Другие состояния не потребуются, поскольку по достижении состояния S2 или S3 любая следующая монета дополнит сумму до необходимого максимума, после чего будет сгенерировано выходное значение z = 1 и автомат вернется в состояние S0, то есть будет готов к следующей операции продажи. Диаграмма состояний, описывающая поведение нашего торгового автомата, приведена на рис. 4.12.

Обратите внимание, что в диаграмме отсутствует входная пара значений x1х2 =11, поскольку опустить в автомат обе монеты одновременно невозможно. Кроме того, как видите, из каждого узла-состояния исходит стрелка, указывающая на него же и обозначенная как 00/0. Эта стрелка говорит о том, что пока в автомат не опущена ни одна монета, он остается в прежнем состоянии.

x1 = 1 — опущена монета в 25 центов; х2 = 1 — опущена монета в 10 центов

z = 1 — выдача товара (получена сумма в 30 или более центов)

Рис. 4.12. Диаграмма состояний торгового автомата

Описанный автомат может иметь всего четыре состояния, для реализации которых достаточно двух триггеров. Обозначим их как у2 и y1 и назначим им следующие значения: S0 = 00, S1 = 01, S2 = 10 и S3 = 11. Результирующая таблица состояний приведена на рис. 4.3. Прочерки в таблице соответствуют комбинации x1х2 = 11, которая на практике невозможна. Эти элементы, являющиеся безразличными значениями, при разработке схемы будут нам очень полезны, о чем узнаете позднее.

Таблица 4.3

Таблица состояний для торгового автомата

|

Текущее состояние |

Следующее состояние |

Выход Z |

|||||||

|

Х1х2 = 00 |

X1x2 =01 |

X1x2 =10 |

x1х2 =11 |

X1x2 =00 |

X1x2 =01 |

X1x2 =10 |

X1X2 = 11 |

||

|

|

Y2Y1 |

Y2Y1 |

Y2Y1 |

Y2Y1 |

Y2Y1 |

||||

|

S0 S1 S2 S3 |

0 0 0 1 1 0 1 1 |

0 0 0 1 1 0 1 1 |

0 1 1 0 0 0 0 0 |

1 1 0 0 0 0 0 0 |

--- --- - - |

0 0 0 0- |

0 0 1 1 |

0 1 1 1 |

- - - - |

Этим завершается первый этап процесса разработки автомата. Составленной нами таблице состояний соответствует таблица истинности (табл. 4.4) - она определяет функцию, которую нам предстоит реализовать в блоке комбинаторной логики. Из таблицы легко вывести следующие выражения:

Y2

=

![]()

![]() y2

+

x2

y2

+

x2![]() y1

+ x1

y1

+ x1![]()

![]()

Y1

=

![]()

![]() y1

+

y1

+

![]()

![]() (x1

+ х2)

(x1

+ х2)

z = y2(x1 + х2) + x1y1

Таблица 4.4

Спецификация комбинаторной логики для торгового автомата

|

1 х2 У1 У2 |

Y2 |

Y1 |

z |

|

0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 |

0 0 1 1 0 1 0 0 1 0 0 0 d d d d |

0 1 0 1 1 0 0 0 1 0 0 0 d d d d |

0 0 0 0 0 0 1 1 0 1 1 1 d d d d |

Как

видите, термы

![]()

![]() и

(x1

+ х2) встречаются в приведенных выражениях

более одного раза. Это удешевляет

реализацию логического блока.

Последовательные схемы удобнее всего

реализовывать в виде ПМЛ, СПЛУ и

программируемых вентильных матриц,

поскольку все эти типы схем состоят из

триггеров и логических вентилей.

Современные средства автоматизированного

проектирования позволяют синтезировать

последовательные схемы непосредственно

на основе спецификаций, составленных

в терминах диаграммы состоянии.

и

(x1

+ х2) встречаются в приведенных выражениях

более одного раза. Это удешевляет

реализацию логического блока.

Последовательные схемы удобнее всего

реализовывать в виде ПМЛ, СПЛУ и

программируемых вентильных матриц,

поскольку все эти типы схем состоят из

триггеров и логических вентилей.

Современные средства автоматизированного

проектирования позволяют синтезировать

последовательные схемы непосредственно

на основе спецификаций, составленных

в терминах диаграммы состоянии.

В таблице 4.3 для состоянии S2, значения следующих состояний и выходной переменной одинаковы при всех входных комбинациях, в которых происходит изменение состояния. Это означает, что для представления итоговых сумм в 20 и 25 центов двух разных состояний не требуется. Для них достаточно одного общего состояния, поскольку, как только в автомате окажется одна из этих двух сумм, поступление любой следующей монеты приведет к выдаче товара (z = 1) и возврату в состояние S0. Таким образом, состояния S2 и S3 эквивалентны и могут быть заменены одним состоянием. Это означает, что для реализации нашего торгового автомата достаточно трех состояний. Однако для них по-прежнему требуется два триггера. В общем случае, с уменьшением количества состояний обычно уменьшается и количество триггеров, а вся схема упрощается.

Напоследок заметим, что для представления переменных состояния могут применяться и триггеры других типов. Мы использовали триггеры типа D, чтобы предельно упростить задачу. Более гибкие триггеры, и в частности JK, позволяют сократить объем необходимых логических схем. Рассказывая о последовательных схемах, мы опирались на схемы, управляемые тактовым сигналом. Но последовательную схему можно создать и без тактового входа. Такие схемы, называемые асинхронными последовательными схемами, разрабатывать несколько сложнее, чем синхронные последовательные.