2 Перевод

Контроллер прямого доступа к памяти (DMA)

Этот раздел применим для всего семейство контроллеров STM32F4xx, если не указано иное.

1 Введение в DMA

Прямой доступ к памяти (DMA) используется для обеспечения высокоскоростной передачи данных между периферийными устройствами и памятью или между памятью и памятью. Данные могут быть быстро перемещены с помощью DMAбез любых действий процессора (CPU). Эти сохранённые ресурсы процессора свободны для других операций.

Контроллер DMAсовмещает мощную двойную архитектуруAHBмастер-шины с независимымFIFOдля оптимизации пропускной способности системы, основанный на сложной шине с матричной архитектурой.

Два контроллера DMAимеют в сумме 16 потоков (8 для каждого контроллера), каждый из которых используется для управления запросами доступа к памяти из одного или нескольких периферийных устройств. Каждый поток может содержать до 8 каналов (запросов) в сумме. И каждый из них имеетарбитра для обработки приоритет между DMA запросов.

2 Основные возможности DMA

Основные возможности DMA:

двойная архитектура AHBмастер-шины, одна выделена для доступа к памяти и другая для доступа к периферии;

ведомый AHBпрограммируемый интерфейс поддерживает только 32-битный доступ;

8 потоков для каждого контроллера DMA, до 8 каналов (запросов) на поток;

4 разделенных 32-битных «первый вошел, первый вышел» буферов памяти (FIFO) на поток, которые могут быть использованы в режимеFIFOили в режиме прямого доступа

Режим FIFO: с пороговым значением, выбираемым программным между 1/4, 1/2 или 3/4 от размера FIFO

Прямой режим.

Каждый запрос DMA, сразу же возбуждали передачу из/в память. Когда он настроен в прямом режиме (FIFO отключен), для передачи данных в режиме из памяти в периферию, DMA выполняет предварительную загрузку только одного блока данным из памяти во внутрь.

FIFO обеспечивает немедленную передачу данных, как только запрос DMA вызывается периферийным устройством.

Каждый поток может быть настроен с помощью аппаратных средств, чтобы быть:

Обычный канал, который поддерживает передачу из периферии в память, из памяти в периферию и из памяти в память

двухканальный буфер, который также поддерживает двойную буферизацию на стороне памяти

каждый из 8 потоков присоединяется к выделенному аппаратному каналу DMA

Приоритеты между потоками DMA программно программируемые (4 уровня, включающие очень высокий, высокий, средний, низкий) или аппаратно в случае равенства (поток 0 имеет приоритет над потоком 1 и т.д.)

Каждый поток, также, поддерживает программный триггер для передачи из памяти в память (доступно только для контроллера DMA2)

Каждый поток может быть выбран среди 8 возможных каналов. Этот выбор программно-конфигурируемый и позволяет нескольким периферийным устройствам, инициировать DMA запросы

Количеством элементов данных, которые будут переданы можно управлять либо с помощью контроллера DMA или периферией:

Контроллер потока DMA: количество передаваемых данных для передачи программно программируется в диапазоне от 1 до 65535

Периферийный контроллер потока: количество элементов данных, подлежащих передаче неизвестно, и управляется источником или периферийным устройством назначения, которое аппаратно сигнализирует об окончании передачи

Независимость ширины передаваемых данных источника и приемника (байт, полслова, слово): когда ширины данных источника и приемника не равны, DMA автоматически упаковывает/распаковывает необходимые передачи для оптимизации полосы пропускания. Эта функция доступна только в режиме FIFO

Приращение или не приращение адресации для источника и приемника

Поддержка пакетной передачи для 4, 8 или 16 элементов данных. Размер пакета является программный настраиваемым, как правило, равен половине размера FIFO периферийного устройства

Каждый поток поддерживает циклическое управление буфером

5 флагов событий (DMA половина передачи, DMA окончание передачи, DMA ошибка передачи, DMA ошибка FIFO, ошибка прямого режима) логически объединены по схеме ИЛИ в одном запросе прерывания для каждого потока

3 DMAОписание функций

3.1 Общее описание

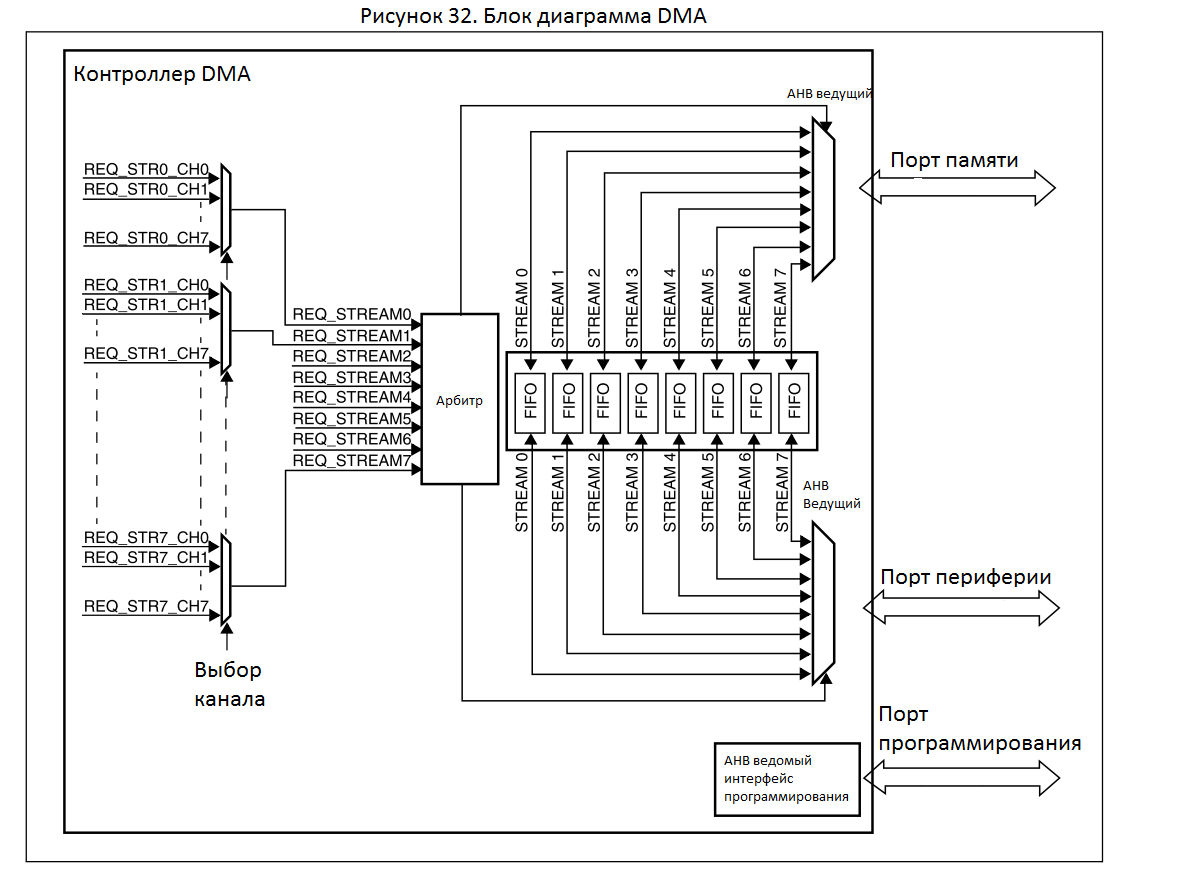

На рисунке 32 изображена блок-диаграмма для DMA

Контроллер DMA выполняет прямую передачу памяти: как мастера АНВ, он может взять на себя управление шиной матрицы AHB, чтобы инициировать AHB транзакции.

Он может выполнять следующие операции:

Из периферии в память;

Из памяти в периферию;

Из памяти в память.

Контроллер DMA имеет два AHBмастер порта: Порт памяти AHB, предназначенный для подключения к памяти и периферийный порт АНВ, предназначенный для подключения к периферийным устройствам. Однако, для предоставления возможности передачи из памяти в память, периферийный порт АHBтакже должны иметь доступ к памяти.

Подчиненный порт AHB используется для программирования контроллера DMA (поддерживается только 32-битный доступ).

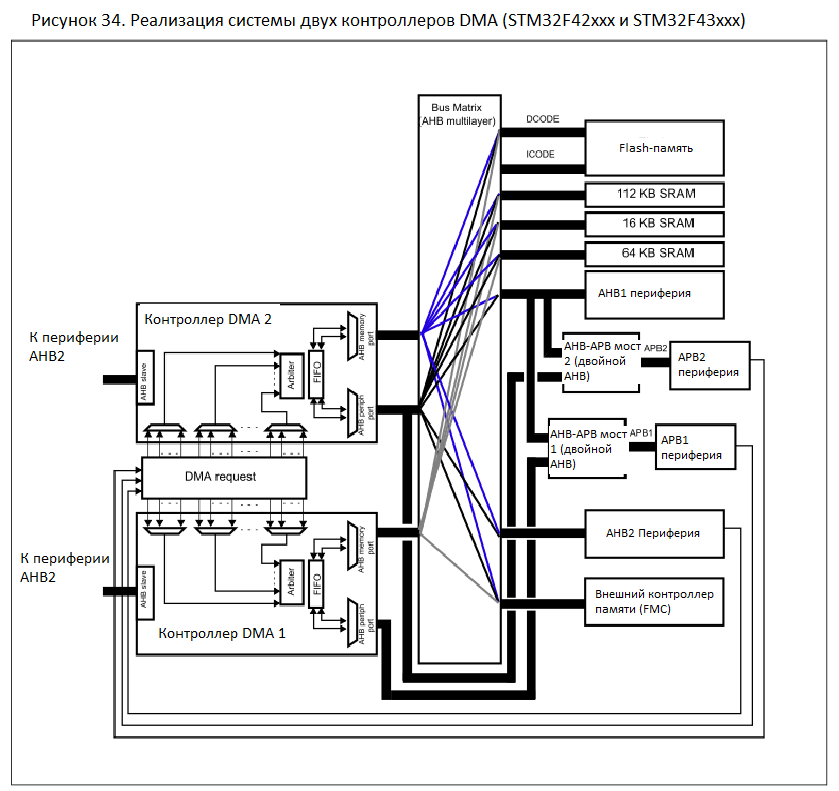

Смотрите Рисунок 33 и Рисунок 34 – реализация системы двух контроллеров DMA.

1. Контроллер DMA1 периферийного порта AHBне подключен к матричной шине, как и в случае с контроллером DMA2, таким образом, только потоки DMA2 способны выполнять передачу из памяти в память.

1. Контроллер DMA1 периферийного порта AHBне подключен к матричной шине, как и в случае с контроллером DMA2, таким образом, только потоки DMA2 способны выполнять передачу из памяти в память.

3.2 DMAтранзакции

Транзакция DMA состоит из последовательности заданного числа передач данных. Количество элементов данных, подлежащих передаче, и их ширина (8-бит, 16-бит или 32-бит) задается программно.

Каждая передача DMAвключает три операции:

Загрузка из данных из регистра периферийных данных или области памяти, адресованные в регистре DMA_SxPAR или DMA_SxM0AR;

сохранение данные загружаются в регистр данных периферии или расположение в памяти, адресуемые через регистры DMA_SxPAR или DMA_SxM0AR;

Постдекремент регистра DMA_SxNDTR, который содержит число операций, которые еще должны быть выполнены.

После события, периферия посылает сигнал запроса в контроллер DMA. Контроллер DMA обслуживает запрос в зависимости от приоритетов каналов. Как только контроллер DMA получает доступ к периферии, посылается сигнал подтверждения периферии контроллером DMA. Периферия инициирует свой запрос, как только он получает сигнал подтверждения от контроллера DMA. После того, как запрос был сброшен на периферийном устройства, контроллера DMA сбрасывает сигнал подтверждения. Если есть другие запросы, периферия может инициировать следующую транзакцию.

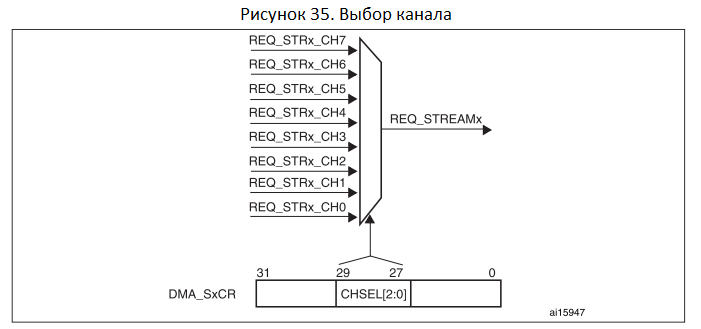

3.3 Выбор канала

Каждый поток связан с запросом DMA, который может быть выбран из 8 возможных запросов канала. Выбор контролируется битами CHSEL [2: 0] регистра DMA_SxCR.

Восемь запросов от периферийных устройств (TIM, ADC, SPI, I2C и т.д.) независимо друг от друга подключены к каждому каналу и их соединения зависит от реализации продукта.

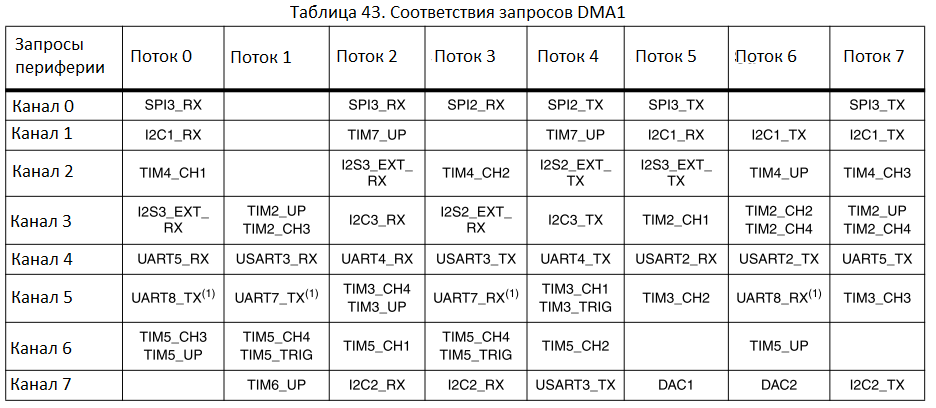

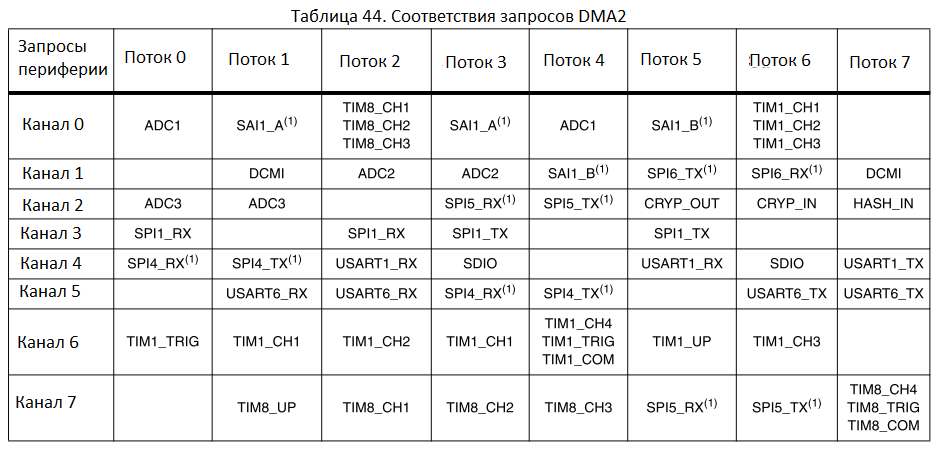

Таблица 43 и Таблица 44 предоставляют примеры соответствий запросов DMA.

1. Эти запросы доступны только для STM32F42XXXиSTM32F43XXX.

1. Эти запросы доступны только для STM32F42XXXиSTM32F43XXX.

3.4 Арбитр

Арбитр управляет 8 DMA потоками, выполняя запросы в зависимости от их приоритета для каждого из двух основных портов AHB (памяти и периферийных портов) и запускает последовательности доступа периферии / памяти.

Приоритеты управляются в две стадии:

Программно: приоритет для каждого из потоков конфигурируется в регистре DMA_SxCR. Существует 4 уровня: очень высокий приоритет, высокий приоритет, средний приоритет, низкий приоритет.

Аппаратно: Если два запроса имеют один некий программный приоритет, потоки с более низким номером берут приоритет над потоками с более высоким номером. Например, поток 2 более приоритетный чем поток 4.

3.5 Потоки DMA

Каждый из 8 потоков контроллера DMAобеспечивает однонаправленный канал связи между источником и местом назначения.

Каждый поток может быть настроен для выполнения:

обычные операции: передача память в периферию, периферия в память или память в память;

Операции с использованием двойного буфера: передачи с использованием двойного буфера используют два указателя памяти (когда DMA считывает/записывает из/в буфера, приложение может записывать/считывать в/из другого буфера.

Количество данных, подлежащих передаче (вплоть до 65535) программируемые и связаны с размером памяти периферии, которая запрашивает передачу DMA, подключенный к периферийномуAHB-порту. Регистр, содержащий количество элементов данных, подлежащих передаче уменьшается после каждой транзакции.

3.6 Источник, место назначения и режим передачи

И источник, и приемник выполняя передачу могут адресовать периферии и памяти во всей 4 Гб области, по адресам, находящихся между 0x0000 0000 и 0xFFFF FFFF.

Направление конфигурируется, используя биты DIR[1:0] в регистре DMA_SxCR и предлагает три варианта передачи: память в периферию, периферия в память или память в память. В таблице 44 описываются соответствующие адреса источников и приемников.

Таблица 44. Адреса источников и приемников

|

Биты DIR[1:0] регистра DMA_SxCR |

Направление |

Адрес источника |

Адрес приемника |

|

00 |

периферия в память |

DMA_SxPAR |

DMA_SxM0AR |

|

01 |

память в периферию |

DMA_SxM0AR |

DMA_SxPAR |

|

10 |

память в память |

DMA_SxPAR |

DMA_SxM0AR |

|

11 |

зарезервировано |

- |

- |

Когда ширина данных (программируемая и битах PSIZE или MSIZE в регистре DMA_SxCR) полслова или слово, соответственно, адрес периферии или памяти, записуемые в регистры DMA_SxPAR или DMA_SxM0AR/M1AR, должен быть выровнен по слову или полуслову, соответственно.

Режим периферия в память

Рисунок 36 описывает этот режим.

Когда этот режим включен (при установке бита EN в реестре DMA_SxCR), каждый раз, когда происходит запрос от периферии, поток инициирует передачу из источники и заполняет FIFO.

Когда достигается пороговое значение в FIFO, содержимое FIFO сливают и сохраняют в месте назначения.

Передача останавливается, как только значение регистра DMA_SxNDTR достигает нуля, когда периферия запрашивает конец передач (в случае контроллера периферийного потока) или когда бит ENв регистре DMA_SxCR очищается программно.

В прямом режиме (когда значение DMDISв регистреDMA_SxFCRравно ‘0’), пороговой уровень вFIFOне используется: после каждой одной единицы данных, переданных с периферии вFIFO, соответствующие данные немедленно передаются и сохраняются в приемнике.

Поток получает доступ к AHB-шине приемника только еслиарбитраж соответствующего потока выигрывает. Этот арбитраж выполняется с использованием приоритетов, определенных для каждого потока в битах PL[1:0] регистра DMA_SxCR.

Режим память в периферию

Рисунок 37 описывает этот режим.

Когда этот режим включен (при установке бита EN в реестре DMA_SxCR), поток немедленно инициирует передачу от источника, что бы полностью заполнить FIFO.

Каждый раз, когда периферия инициирует запрос, содержимое FIFOопустошается и сохраняется в приемнике.

Передача останавливается, как только значение регистра DMA_SxNDTR достигает нуля, когда периферия запрашивает конец передач (в случае контроллера периферийного потока) или, когда бит ENв регистре DMA_SxCR очищается программно.

В прямом режиме (когда значение DMDISв регистреDMA_SxFCRравно ‘0’), пороговой уровень вFIFOне используется. Как только поток включается,DMAвыполняет предварительную загрузку первых данных для передачи в внутреннийFIFO. Как только периферия инициирует запрос передачи данных,DMAпередает предварительно загруженные данные в сконфигурированный приемник. Затем он перезагружает снова пустой внутреннийFIFOсо следующими данными для передачи. Объем предварительно загружаемых данных соответствует значению битового поля PSIZE в регистре DMA_SxCR.

Поток получает доступ к AHB-шине приемника только еслиарбитраж соответствующего потока выигрывает. Этот арбитраж выполняется с использованием приоритетов, определенных для каждого потока в битах PL[1:0] регистра DMA_SxCR.

Режим память в память

Каналы DMAтак же могут работать без их включения по запросу от периферии. Это называется режим память в память, описанный на рисунке 38.

Когда поток включается, установкой бита включения (EN) в регистреDMA_SxCR, поток немедленно начинает заполнениеFIFOдо порогового значения. Когда пороговой уровень достигнут, содержимоеFIFOопустошается и сохраняется в пункте назначения.

Передача останавливается, как только значение регистра DMA_SxNDTR достигает нуля или, когда бит ENв регистре DMA_SxCR очищается программно.

Поток получает доступ к AHB-шине источника или приемника только еслиарбитраж соответствующего потока выигрывает. Этот арбитраж выполняется с использованием приоритетов, определенных для каждого потока в битах PL[1:0] регистра DMA_SxCR.

Заметка: Когда используется режим память в память, циклический и прямой режимы не доступны. Только контроллер DMA2 способен выполнять передачи память в память.

3.7 Приращение указателя

Указатели периферии и памяти могут опционально автоматически пост-инкрементироватьсяили сохранять константное значение после каждой передачи в зависимости от битов PINC и MINC в регистре DMA_SxCR.

Отключение режима инкрементации используют, когда источник периферия или место назначения находится в одном регистре.

Если режим инкрементации включен, адрес следующей передачи будет адрес предыдущей, увеличенной на 1 (для байтов), 2 (для полуслова) или 4 (для слова) в зависимости от ширины данных, запрограммированных в битах PSIZE или MSIZE регистра DMA_SxCR.

Для того, чтобы оптимизировать операцию упаковки, можно закрепить размер инкрементного смещения для адреса периферии независимо от размера передаваемых данных наAHBпорту периферии. Бит PINCOS в регистре DMA_SxCR используется для выравниванияразмера инкрементного смещения с размером данных в периферийномAHBпорту. Бит PINCOS в регистре DMA_SxCR используется для выравнивания приращение размера смещения с размером данных на периферийном порту AHB, или на 32-битный адрес (в адрес в этом случае увеличивается на 4). Бит PINCOS влияет только на периферийный порт AHB.