схемотехника / Сборник задач

.pdf

Вариант 7. |

|

Вариант 8. |

|

Вариант 9. |

|||

|

|

|

|

|

|

|

|

Такт |

|

|

Такт |

|

|

Такт |

|

Вход |

i |

|

Вход |

i |

|

Вход |

i |

D1 |

1 |

|

D1 |

0 |

|

D1 |

1 |

D2 |

1 |

|

D2 |

1 |

|

D2 |

1 |

D3 |

1 |

|

D3 |

0 |

|

D3 |

0 |

Вариант 10. |

|

Вариант 11. |

|

|

Вариант 12. |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Такт |

|

|

|

|

Такт |

|

|

|

|

Такт |

|

|

|

|

i-2 |

i-1 |

i |

|

|

i-2 |

i-1 |

i |

|

|

i-2 |

i-1 |

i |

Вход |

|

|

|

|

Вход |

|

|

|

|

Вход |

|

|

|

D1 |

X |

X |

1 |

|

D1 |

0 |

1 |

0 |

|

D1 |

0 |

X |

X |

D2 |

X |

1 |

X |

|

D2 |

0 |

1 |

0 |

|

D2 |

X |

0 |

X |

D3 |

1 |

X |

X |

|

D3 |

0 |

1 |

0 |

|

D3 |

X |

X |

0 |

В вариантах 13–15 требуется подсчитать количество выполнений заданных отношений между селектируемыми данными двух типов. В скобках записан двоичный код: старший бит, указан слева, младший бит – справа.

Вариант 13. (D1(i-1),D2i)> (D2(i-1),D3i). (Селекция с такта 2). Вариант 14. (D3i,D2i,D1i) ≥ (D3(i-1),D2(i-1),D1(i-1)). (Селекция с

такта 2).

Вариант 15. (D3(i-2), D2(i-2),D1(i-1)) ≤ (D3(i-1),D2(i-1),D1i). (Селекция с

такта 3).

Задача 4. Разработать схему для подсчёта общего количества групп изолированных нулей в N-разрядном коде. Группа из любого количества нулей изолирована, если она справа и слева ограничена единицами.

Код поступает на вход CODE схемы последовательно в сопровождении N синхроимпульсов С. Значения разрядов кода на входе CODE изменяются в паузе между импульсами С. Перед поступлением кода на устройство подается сигнал начальной установки RESET. Ниже приведены варианты последовательностей с четырьмя группами изолированных нулей для N=19 и N=18.

191

Вариант 1.

Вариант 2.

Вариант 3.

Вариант 4.

Задача 5. Разработать схему для подсчёта общего количества изолированных нулей и единиц в 16-разрядном двоичном коде. Нуль (единица) считается изолированным (ой), если он (она) с обеих сторон имеет единицы (нули). Крайние разряды считаются неизолированными. Например, для кода 1011010…01 результат равен 5 (три изолированных «0» и две изолированных «1»).

192

Код поступает на вход CODE схемы последовательно в сопровождении синхроимпульсов С. Значения разрядов кода на входе CODE изменяются в паузе между импульсами С. Перед поступлением кода и синхроимпульсов на схему подается одиночный импульс RESET для установки схемы в начальное состояние. Результат должен быть зафиксирован.

Задача 6. Разработать схему для подсчёта общего количества групп нулей и единиц в 20-разрядном коде. Группой нулей (единиц) считается не менее двух рядом стоящих нулей (единиц), отделенных единицами (нулями) или левой границей кода (со стороны старших разрядов). Например, код 1100010…0111 содержит три группы.

Код поступает на вход CODE схемы последовательно со старших разрядов в сопровождении двадцати синхроимпульсов С. Значения разрядов кода на входе CODE изменяются в паузе между импульсами С. Перед поступлением кода и импульсов С на схему подается одиночный импульс CLR для установки схемы в начальное состояние. Результат должен быть зафиксирован.

Задача 7. Разработать схему, которая вырабатывает на выходе Y сигнал единичного уровня, если сигнал на входе X имеет нулевое значение для шести и более тактовых интервалов.

193

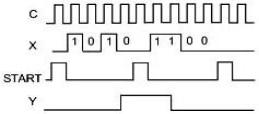

Задача 8. Четырёхразрядные посылки двоичных данных в последовательной форме, синхронизируемые тактовыми импульсами С, поступают на вход X логической схемы. Перед началом каждой посылки на вход START схемы синхронно с импульсами С подаётся стартовый сигнал. Разработать синхронную последовательностную схему, которая при обнаружении среди входных посылок любой из трёх комбинаций, заданных вариантом, вырабатывает на выходах Y1 и Y0 код номера этой комбинации. При обнаружении любой другой комбинации на выходах выставляется код 00. Рисунок иллюстрирует работу схемы для варианта 1.

Вариант |

|

Кодовые комбинации |

|

||

Первая |

|

Вторая |

|

Третья |

|

|

|

|

|||

1 |

1010 |

|

0110 |

|

0010 |

2 |

0001 |

|

1011 |

|

0101 |

3 |

0010 |

|

1101 |

|

0110 |

4 |

0111 |

|

1001 |

|

1100 |

5 |

0011 |

|

0110 |

|

1000 |

6 |

0100 |

|

1010 |

|

1100 |

7 |

1110 |

|

0010 |

|

0101 |

8 |

1011 |

|

0111 |

|

1111 |

9 |

1001 |

|

0101 |

|

1110 |

10 |

0101 |

|

1011 |

|

1000 |

11 |

1100 |

|

1010 |

|

0001 |

12 |

0110 |

|

0011 |

|

1100 |

13 |

0001 |

|

0011 |

|

0111 |

14 |

0101 |

|

0011 |

|

1111 |

15 |

0010 |

|

1110 |

|

0100 |

194

Задача 9. Разработать схему, которая имеет четыре входа START, C, D, Х и три выхода Y2,Y1,Y0. В каждом цикле работы схемы на входы START, C и D подаются сигналы в соответствии с временной диаграммой:

После подачи сигнала START в одном из последующих восьми тактов (1-8) по фронту 0/1 импульса C на вход Х приходит потенциальный сигнал, который разрешает подачу на схему импульсов С и сохраняется до начала следующего цикла. После окончания цикла работы схемы на выходах Y2,Y1,Y0 должен быть сформирован номер такта, в котором пришёл сигнал на вход Х.

Вариант |

|

Битовая последовательность на входе D в тактах |

|

||||||||||

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

||

|

|||||||||||||

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

|

2 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

|

3 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

|

4 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

|

5 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

|

6 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

|

7 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

|

8 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

|

9 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

|

10 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

|

11 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

|

12 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

|

13 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

|

14 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

|

15 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

|

195

Задача 10. Четырёхразрядные посылки двоичных данных в последовательной форме, синхронизируемые тактовыми импульсами С, поступают на вход Х логической схемы. Перед началом каждой посылки на вход START схемы синхронно с импульсами С подаётся стартовый сигнал. Разработать схему, которая вырабатывает выходной сигнал Y при обнаружении среди входных посылок любой из трёх комбинаций, заданных вариантом. Если выход Y был предварительно установлен в «1», то он должен сбрасываться в «0, если текущая посылка не относится к трём заданным комбинациям. Рисунок иллюстрирует работу схемы для варианта 1.

Вариант |

Кодовые комбинации |

1 |

1010, 0110, 0010 |

2 |

0001, 1011, 0101 |

3 |

0010, 1101, 0110 |

4 |

0111, 1001, 1100 |

5 |

0011, 0110, 1000 |

6 |

0100, 1010, 1100 |

7 |

1110, 0010, 0101 |

8 |

1011, 0111, 1111 |

9 |

1001, 0101, 1110 |

10 |

0010, 0101, 1100 |

11 |

0101, 1101, 0011 |

12 |

0111, 1001, 0100 |

13 |

1000, 0110, 1110 |

14 |

1101, 0101, 1001 |

15 |

0001, 0111, 1011 |

Задача 11. Разработать устройство, которое имеет четыре входа и один выход. После подачи сигнала начальной установки на вход RESET на входы Х2, Х1 и Х0 начинают синхронно и последова-

196

тельно, начиная со старших разрядов, подаваться коды 6-разрядных беззнаковых чисел. Устройство должно передавать на выход Y код максимального из трёх чисел, подаваемых на его входы (пример показан на рисунке).

Задача 12. Разработать схему, которая вырабатывает на выходе Y сигнал единичного уровня в течение шести тактовых импульсов после того, как сигнал на входе X имеет единичное значение в течение одного тактового интервала времени. Если сигнал на входе X принимает единичное значение снова в течение шести тактовых интервалов, то схема не реагирует на это изменение. Сигнал X изменяет свое значение по фронту 1/0 сигнала синхронизации С.

Задача 13. Разработать схему анализа 6-разрядной кодовой последовательности, которая поступает на вход X схемы одновременно с синхроимпульсами С. Кодовые сигналы изменяются в промежутках между импульсами С. Схема должна выдать на выход Y импульс в 7 такте, если число единиц в 3, 5 и 6 тактах кодовой последовательности больше числа единиц в 1, 2 и 4 тактах. Если меньше, то схема должна выдать импульс в 8 такте. Если же число единиц в тактах 3, 5 и 6 равно числу единиц в тактах 1, 2 и 4, то импульс на выходе схемы не вырабатывается. Перед поступлением кодовой последовательности на схему подается сигнал CLR установки в начальное состояние.

197

Задача 14. Разработать схему, которая выдает на выход Y импульс всякий раз, когда в двух кодовых последовательностях X1 и X2, поступающих на отдельные входы схемы, одновременно появляется подряд (без пропуска) три единицы. Кодовые сигналы в последовательностях X1 и X2 изменяются в промежутках между синхроимпульсами С.

Задача 15. Разработать схему, которая выдает на выход Y импульс всякий раз, когда в поступающей на ее вход X кодовой последовательности появляется подряд (без пропуска) четыре единицы. Кодовые сигналы изменяются в промежутках между синхроимпульсами С.

Задача 16. На один вход схемы поступает кодовая последовательность X, на другой – сопровождающая её последовательность синхроимпульсов C. Кодовые сигналы изменяются в промежутках между импульсами С. Схема должна выдавать на выход Y каждый третий импульс С, если сигналы кодовой последовательности в каждом из трёх тактов равны «1».

198

Задача 17. На вход схемы сравнения последовательного действия синхронно с тактовыми импульсами С поступают четырехразрядные двоичные числа: A3,A2,A1,A0 и B3,B2,B1,B0, начиная со старших разрядов. Подаче чисел на входы А и В схемы предшествует подача стартового сигнала на вход START.

Разработать синхронную последовательностную схему, на выходах Y1, Y2 и Y3 которой формируются сигналы по следующему правилу:

Y1=1 при А>В, Y2=1 при А=В, Y3=1 при А<В.

Задача 18. Разработать асинхронную схему обнаружения последовательности, которая имеет два входа Х1 и Х0 и один выход Y. Выходной сигнал Y становится равным «1» только при последовательности входных состояний Х1,Х0, принимающих значения 00, 01, 11. Выходной сигнал Y становится равным «0» только после появления на входах последовательности состояний 11, 01, 00.

199

Задача 19. Двоично-десятичные данные в последовательной форме, синхронизируемые импульсами С, начиная со старших разрядов, поступают на вход Х логической схемы. Перед началом каждой кодовой посылки на вход START схемы синхронно с импульсами С подается стартовый сигнал. Разработать схему, которая вырабатывает выходной сигнал Y, как только обнаруживается подача на её вход неиспользуемой в данном коде кодовой комбинации. На рисунке представлен пример для варианта 1.

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|||||||

X |

|

1 |

|

0 |

0 |

|

1 |

|

0 |

|

1 |

0 |

|

|

1 |

1 |

|

|

|

|

|

|

|

||||||||||||||

START |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||

Вариант |

|

|

|

|

Двоично-десятичный код |

|

|||||||||||||||||||||||||||||||

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8421 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8421+3 |

|

|

|

|

|

|

|

|

|

|

|

|||||||

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5421 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5421+3 |

|

|

|

|

|

|

|

|

|

|

|

|||||||

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2421 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7421 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3321 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5211 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2521 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3411 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2621 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4271 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4621 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5221 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6321 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

Задача 20. Двоичные данные в последовательной форме, синхронизируемые тактовыми импульсами C, поступают по линии X на логическую последовательностную схему. Данные изменяются по фронту 1/0 сигнала С.

Разработать схему, в которой на выходе Y сигнал появляется каждый раз, как только во входной последовательности X появляется набор 1101.

200