схемотехника / Сборник задач

.pdf

FDCE — D-триггер с входом разрешения синхросигнала и асинхронной установкой в «0»

Условное графическое обозначения D-триггера FDCE приведено на рис. П.11, а его таблица переходов представлена табл. П.2.

Рис. П.11. Условное графическое обозначение D-триггера FDCE

|

|

|

|

|

Таблица П.2 |

|

Таблица переходов D-триггера FDCE |

|

|||

|

|

|

|

|

|

|

|

Входы |

|

Выход |

|

CLR |

CE |

|

D |

C |

Q |

1 |

X |

|

X |

X |

0 |

0 |

0 |

|

X |

X |

Q |

0 |

1 |

|

1 |

0/1 |

1 |

0 |

1 |

|

0 |

0/1 |

0 |

FDPE — D-триггер с входом разрешения синхросигнала и асинхронной установкой в «1»

Условное графическое обозначения D-триггера FDРE приведено на рис. П.12, а его таблица переходов представлена табл. П.3.

Рис. П.12. Условное графическое обозначение D-триггера FDРE

211

|

|

|

|

|

Таблица П.3 |

|

Таблица переходов D-триггера FDPE |

|

|||

|

|

|

|

|

|

|

|

Входы |

|

Выход |

|

PRE |

CE |

|

D |

C |

Q |

1 |

X |

|

X |

X |

1 |

0 |

0 |

|

X |

X |

Q |

0 |

1 |

|

1 |

0/1 |

1 |

0 |

1 |

|

0 |

0/1 |

0 |

FDRE — D-триггер с входом разрешения синхросигнала и синхронной установкой в «0»

Условное графическое обозначения D-триггера FDRE приведено на рис. П.13, а его таблица переходов представлена табл. П.4.

Рис. П.13. Условное графическое обозначение D-триггера FDRE

|

|

|

|

|

Таблица П.4 |

|

Таблица переходов D-триггера FDRE |

|

|||

|

|

|

|

|

|

|

|

Входы |

|

Выход |

|

R |

CE |

|

D |

C |

Q |

1 |

X |

|

X |

0/1 |

0 |

0 |

0 |

|

X |

X |

Q |

0 |

1 |

|

1 |

0/1 |

1 |

0 |

1 |

|

0 |

0/1 |

0 |

Данный триггер является макроэлементом, его структура приведена на рис. П.14.

212

Рис. П.14. Внутренняя структура D-триггера FDRE

FDSE — D-триггер с входом разрешения синхросигнала и синхронной установкой в «1»

Условное графическое обозначения D-триггера FDSE приведено на рис. П.15. а его таблица переходов представлена табл. П.5.

Рис. П.15. Условное графическое обозначение D-триггера FDSE

|

|

|

|

|

Таблица П.5 |

|

Таблица переходов D-триггера FDSE |

|

|||

|

|

|

|

|

|

|

|

Входы |

|

Выход |

|

S |

CE |

|

D |

C |

Q |

1 |

X |

|

X |

0/1 |

1 |

0 |

0 |

|

X |

X |

Q |

0 |

1 |

|

1 |

0/1 |

1 |

0 |

1 |

|

0 |

0/1 |

0 |

Триггер FDSE является макроэлементом, его структура приведена на рис. П.16.

213

Рис. П.16. Внутренняя структура D-триггера FDSE

JK-триггеры

FJKC — JK-триггер с асинхронной установкой в «0»

Условное графическое обозначения JK-триггера FJKC приведено на рис. П.17, а его таблица переходов представлена табл. П.6.

Рис. П.17. Условное графическое обозначение JK-триггера FJKC

|

|

|

|

|

Таблица П.6 |

|

Таблица переходов JK-триггера FJKC |

|

|||

|

|

|

|

|

|

|

|

Входы |

|

Выход |

|

CLR |

J |

|

K |

C |

Q |

1 |

X |

|

X |

X |

0 |

0 |

0 |

|

0 |

0/1 |

Q |

0 |

0 |

|

1 |

0/1 |

0 |

0 |

1 |

|

0 |

0/1 |

1 |

0 |

1 |

|

1 |

0/1 |

¬Q |

|

|

214 |

|

|

|

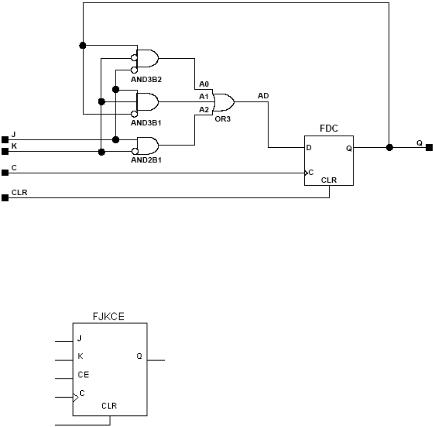

Триггер FJKC является макроэлементом, его структура приведена на рис. П.18.

Рис. П.18. Внутренняя структура JK-триггера FJKC

FJKCE — JK-триггер с входом разрешения синхросигнала и асинхронной установкой в «0»

Условное графическое обозначения JK-триггера FJKCE приведено на рис. П.19, а его таблица переходов представлена табл. П.7.

Рис. П.19. Условное графическое обозначение JK-триггера FJKCE

|

|

|

|

|

|

Таблица П.7 |

|

|

Таблица переходов JK-триггера FJKCE |

|

|||

|

|

|

|

|

|

|

|

|

|

Входы |

|

|

Выход |

CLR |

CE |

|

J |

K |

C |

Q |

1 |

X |

|

X |

X |

X |

0 |

0 |

0 |

|

X |

X |

X |

Q |

0 |

1 |

|

0 |

0 |

X |

Q |

0 |

1 |

|

0 |

1 |

0/1 |

0 |

0 |

1 |

|

1 |

0 |

0/1 |

1 |

0 |

1 |

|

1 |

1 |

0/1 |

¬Q |

215

Триггер FJKCE является макроэлементом, его структура приведена на рис. П.20.

Рис. П.20. Внутренняя структура JK-триггера FJKCE

T-триггеры

FTCE — T-триггер с входом разрешения синхросигнала и асинхронной установкой в «0»

Условное графическое обозначения T-триггера FTCE приведено на рис. П.21, а его таблица переходов представлена табл. П.8.

Рис. П.21. Условное графическое обозначение T-триггера FTCE

216

|

|

|

|

|

Таблица П.8 |

|

Таблица переходов T-триггера FTCE |

|

|||

|

|

|

|

|

|

|

|

Входы |

|

Выход |

|

CLR |

CE |

|

T |

C |

Q |

1 |

X |

|

X |

X |

0 |

0 |

0 |

|

X |

X |

Q |

0 |

1 |

|

0 |

0/1 |

Q |

0 |

1 |

|

1 |

0/1 |

¬Q |

Триггер FTCE является макроэлементом, его структура дана на рис. П.22.

Рис. П.22. Внутренняя структура T-триггера FTСE

FTCLE — T-триггер с функцией синхронной загрузки, входом разрешения синхросигнала и асинхронной установкой в «0»

Условное графическое обозначения T-триггера FTCLE приведено на рис. П.23, а его таблица переходов представлена табл. П.9.

Рис. П.23. Условное графическое обозначение T-триггера FTCLE

217

|

|

|

|

|

|

|

|

|

Таблица П.9 |

|

|

Таблица переходов T-триггера FTCLE |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Входы |

|

|

|

Выход |

|

CLR |

L |

|

CE |

|

T |

D |

|

C |

Q |

1 |

X |

|

X |

|

X |

X |

|

X |

0 |

0 |

1 |

|

X |

|

X |

1 |

|

0/1 |

1 |

0 |

1 |

|

X |

|

X |

0 |

|

0/1 |

0 |

0 |

0 |

|

0 |

|

X |

X |

|

X |

Q |

0 |

0 |

|

1 |

|

0 |

X |

|

0/1 |

Q |

0 |

0 |

|

1 |

|

1 |

X |

|

0/1 |

¬Q |

Триггер FTCLE является макроэлементом, его структура приведена на рис. П.24.

Рис. П.24. Внутренняя структура T-триггера FTСLE

FTCLEX — T-триггер с функцией синхронной загрузки, входом разрешения синхросигнала и асинхронной установкой в «0»

Условное графическое обозначения T-триггера FTCLEX приведено на рис. П.25, а его таблица переходов представлена табл. П.10.

218

Рис. П.25. Условное графическое обозначение T-триггера FTCLEX

|

|

|

|

|

|

|

|

Таблица П.10 |

|

|

Таблица переходов T-триггера FTCLEX |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Входы |

|

|

Выход |

|

CLR |

L |

|

CE |

|

T |

D |

C |

Q |

1 |

X |

|

X |

|

X |

X |

X |

0 |

0 |

1 |

|

1 |

|

X |

1 |

0/1 |

1 |

0 |

1 |

|

1 |

|

X |

0 |

0/1 |

0 |

0 |

0 |

|

0 |

|

X |

X |

X |

Q |

0 |

0 |

|

1 |

|

0 |

X |

0/1 |

Q |

0 |

0 |

|

1 |

|

1 |

X |

0/1 |

¬Q |

Триггер FTCLEX является макроэлементом, его структура дана на рис. П.26.

Рис. П.26. Внутренняя структура T-триггера FTСLEX

Примечание.: Как видно из рис. П.23 и П.25, графическое обозначение и наименование выводов триггеров FTCLE и FTCLEX полностью совпадают. Однако

219

рассмотрение способов их реализации позволяет выявить различие при выполнении микрооперации загрузки (см. рис. П.24 и П.26).

Если активен сигнал на входе L, то по фронту тактового сигнала триггер принимает состояние, определяемое входом D. Однако для триггера FTCLE такая загрузка возможна при отсутствии активного сигнала на входе разрешения CE (такое разрешение формируется элементом OR2 при наличии активного уровня на входе L), а для триггера FTCLEX загрузка возможна только при наличии активного уровня на входе СЕ (см. табл. П.9 и П.10).

Мультиплексоры

Пример соглашения для обозначения мультиплексоров в библиотеке элементов приведен на рис. П.27.

Рис. П.27.Обозначение мультиплексоров

Мультиплексор 2-1 (M2_1)

Мультиплексор выбирает один информационный вход из двух источников (D1 или D0) в зависимости от состояния управляющего входа S0. Выход (O) принимает состояние выбранного входа данных. При S0 = 0 на выходе появляется состояние входа D0, при

S0 = 1 – D1.

Условное графическое обозначение мультиплексора приведено на рис. П.28, а его таблица истинности представлена табл. П.11.

Рис. П.28. Условное графическое обозначение мультиплексораM2_1

220