схемотехника / Сборник задач

.pdf

|

|

|

Таблица П.11 |

|

Таблица истинности мультиплексора M2_1 |

|

|

|

|

|

|

|

Входы |

|

Выход |

S0 |

D1 |

D0 |

O |

1 |

1 |

X |

1 |

1 |

0 |

X |

0 |

0 |

X |

1 |

1 |

0 |

X |

0 |

0 |

Мультиплексоры 2-1 с инверсными входами (M2_1B1 и M2_1B2)

Условные графические обозначения мультиплексоров с инверсными входами приведены на рис. П.29. Данные мультиплексоры отличаются от предыдущего наличием одного или двух инверсных входов, что отражено на их условном графическом обозначении.

Рис. П.29. Условное графическое обозначение мультиплексоров с инверсными входами

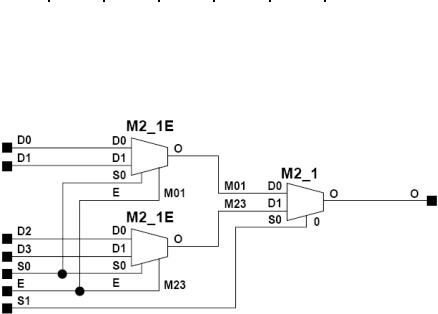

Мультиплексор 2-1 с входом разрешения (M2_1E)

Условное графическое обозначение мультиплексора M2_1Е приведено на рис. П.30.

Вход Е разрешает работу мультиплексора. Когда разрешающий вход E = 1, то мультиплексор M2_1E выбирает один из информационных входов (D1 или D0) в зависимости от состояния управляющего входа S0. При Е = 0 состояние выхода равно «0».

Таблица истинности мультиплексора M2_1Е представлена табл. П.12.

221

|

|

|

|

Рис. П.30. Условное графическое |

||

|

|

|

|

обозначение мультиплексора M2_1Е |

||

|

|

|

|

|

|

Таблица П.12 |

|

Таблица истинности мультиплексораM2_1Е |

|

||||

|

|

|

|

|

|

|

|

|

Входы |

|

|

Выход |

|

E |

S0 |

|

D1 |

|

D0 |

O |

0 |

X |

|

X |

|

X |

0 |

1 |

0 |

|

X |

|

1 |

1 |

1 |

0 |

|

X |

|

0 |

0 |

1 |

1 |

|

1 |

|

X |

1 |

1 |

1 |

|

0 |

|

X |

0 |

Мультиплексор 4-1 с входом разрешения (M4_1E)

Условное графическое обозначение мультиплексора M4_1Е приведено на рис. П.31.

Рис. П.31. Условное графическое обозначение мультиплексора M4_1Е

Вход Е разрешает работу мультиплексора. Когда разрешающий вход E = 1, то мультиплексор M4_1E выбирает один из четырех информационных входов (D3, D2, D1 или D0) в зависимости от со-

222

стояния управляющих (адресных) входов S1 и S0. При Е = 0 состояние выхода равно «0».

Таблица истинности мультиплексора M4_1Е представлена табл. П.13.

Таблица П.13

Таблица истинности мультиплексора M4_1Е

|

|

|

Входы |

|

|

|

Выход |

E |

S1 |

S0 |

D0 |

D1 |

D2 |

D3 |

O |

0 |

X |

X |

X |

X |

X |

X |

0 |

1 |

0 |

0 |

D0 |

X |

X |

X |

D0 |

1 |

0 |

1 |

X |

D1 |

X |

X |

D1 |

1 |

1 |

0 |

X |

X |

D2 |

X |

D2 |

1 |

1 |

1 |

X |

X |

X |

D3 |

D3 |

Структура мультиплексора M4_1Е приведена на рис. П.32.

Рис. П.32. Внутренняя структура мультиплексораM4_1Е

Дешифратор

Дешифратор 2-4 с входом разрешения (D2_4E)

Условное графическое обозначение дешифратора D2_4E приведено на рис. П.33.

223

Рис. П.33. Условное графическое обозначение дешифратора D2_4E

Дешифратор преобразует двухразрядный двоичный код, поступающий на входы А1, А0, в четырехразрядный унитарный код на выходах D0 D3, при наличии сигнала высокого уровня на входе разрешения Е (табл. П.14).

Дешифратор D2_4E является макроэлементом, его структура приведена на рис. П.34.

|

|

|

|

|

|

|

|

Таблица П.14 |

|

|

|

Таблица истинности дешифратора D2_4E |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

Входы |

|

|

|

Выходы |

|

|

|

|

E |

A1 |

|

A0 |

D0 |

D1 |

|

D2 |

|

D3 |

0 |

X |

|

X |

0 |

0 |

|

0 |

|

0 |

1 |

0 |

|

0 |

1 |

0 |

|

0 |

|

0 |

1 |

0 |

|

1 |

0 |

1 |

|

0 |

|

0 |

1 |

1 |

|

0 |

0 |

0 |

|

1 |

|

0 |

1 |

1 |

|

1 |

0 |

0 |

|

0 |

|

1 |

Рис. П.34. Внутренняя структура дешифратора D2_4E

224

Сумматоры

Четырехразрядный и восьмиразрядный сумматоры

(ADD4 и ADD8)

Условные графические обозначения сумматоров ADD4 и ADD8 приведены на рис. П.35.

Сумматоры складывают два операнда А и В с учетом состояния входа CI. На выходах сумматоров формируется сумма S, сигнал переноса (CO — carry-out) или сигнал переполнения (OFL — overflow). В зависимости от того, какое толкование пользователь дает операндам А и В, он может использовать или выходы S и CO, или S и OFL (табл. П.15).

Рис. П.35. Условное графическое обозначение сумматоров ADD4 и ADD8: А, В — входы данных; CI — вход переноса; S — сумма входных сигналов; OFL — выход переполнения (для операндов со знаком, представленных в дополнительном коде); СО — выход переноса (для операндов без знака)

225

|

|

|

|

|

Таблица П.15 |

|

Использование выходов CO и OFL сумматоров ADD4 и ADD8 |

|

|||||

|

|

|

|

|

||

S |

СО |

OFL |

Режим работы |

|

||

A+B+CI |

0 |

X |

Суммирование двоичных кодов (S |

16 для |

||

|

|

|

ADD4 и S 256для ADD8) |

|

|

|

A+B+CI |

1 |

X |

Суммирование двоичных кодов (S ≥ 16 для |

|||

|

|

|

ADD4 и S ≥ 256для ADD8) |

|

|

|

A+B+CI |

X |

0 |

Суммирование двух операндов со знаком, пред- |

|||

|

|

|

ставленных в дополнительном коде (S |

– 9 или |

||

|

|

|

8 для ADD4; S |

– 129 или |

128 для ADD8) |

|

A+B+CI |

X |

1 |

Суммирование двух операндов со знаком, пред- |

|||

|

|

|

ставленных в дополнительном коде (S |

7 или |

||

|

|

|

– 8 для ADD4; S |

127 или |

– 128 для ADD8) |

|

Данные сумматоры могут использоваться в двух режимах: или как сумматоры двоичных кодов, или как сумматоры чисел, представленных в дополнительном коде. В последнем случае крайний левый разряд операндов и результата является знаком числа. Функциональное различие между этими режимами состоит в определении «переполнения».

Если интерпретировать операнды как двоичные коды, то переполнение фиксируется на выходе СО, а состояние выхода OFL игнорируется (см. табл. П.15).

Если операнды рассматриваются как числа в дополнительном коде, то переполнение как положительное, так и отрицательное определяется на выходе OFL в виде единичного сигнала, а состояние выхода СО игнорируется (см. табл. П.15).

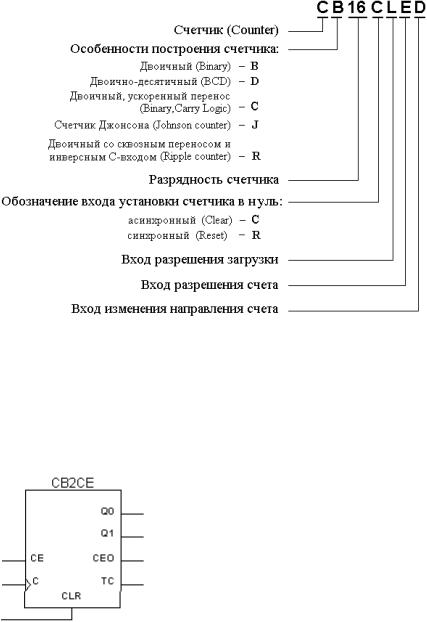

Счётчики

Библиотека элементов содержит большое количество разнообразных счётчиков. Расшифровка обозначения счётчиков приведена на рис. П.36.

Двоичные счётчики в библиотеке элементов имеют разрядность 2, 4, 8 и 16. Их построение однотипно, поэтому рассмотрение двоичных счётчиков будет проведено на примере двухразрядных двоичных счётчиков с различным набором микроопераций.

226

Рис. П.36. Обозначение счётчиков

Двоичный счётчик с асинхронным сбросом и входом разрешения счёта (СВ2СЕ, СВ4СЕ, СВ8СЕ, СВ16СЕ)

Условное графическое обозначение двухразрядного двоичного счётчика СВ2СЕ приведено на рис. П.37, а его внутренняя структура — на рис. П.38.

Рис. П.37. Условное графическое обозначение счётчика СВ2СЕ: С — тактовый вход; СЕ — вход разрешения счёта; CLR — вход сброса; Q1- Q0 — выходы (1-0 разряды); ТС — выход переноса (выход завершения счёта); СЕО — выход разрешения счёта

(СЕО = ТС∙СЕ)

227

Рис. П.38. Внутренняя структура счётчика СВ2СЕ

Вход С является тактовым входом счётчика. У всех библиотечных счётчиков имеется также вход СЕ (разрешение счёта). При низком уровне сигнала на этом входе счётчик не изменяет свое состояние при поступлении тактового сигнала. Выход CEO (Clock Enable Output) принимает то же значение, что и вход СЕ и служит для каскадного соединения счётчиков. Выход ТС (Terminal Count) принимает высокое активное состояние в момент перехода счётчика к последнему разрёшенному состоянию.

Многоразрядные счётчики получают путём соединения выхода CEO одного счётчика с входом CE следующего и объединением входов C и CLR всех счётчиков соответственно.

Двоичный счётчик с параллельной загрузкой, асинхронным сбросом и входом разрешения счёта (СВ2СLЕ, СВ4СLЕ, СВ8СLЕ, СВ16СLЕ)

Условное графическое обозначение двухразрядного двоичного счётчика СВ2СLЕ показано на рис. П.39. Микрооперации, выполняемые счётчиком СВ2СLЕ, приведены в табл. П.16, а его внутренняя структура — на рис. П.40.

228

Рис. П.39. Условное графическое обозначение счётчика СВ2СLЕ: С — тактовый вход; СЕ — вход разрешения счёта; L — вход разрешения параллельной загрузки; CLR — вход сброса; D1-D0 — параллельные входы данных; Q1-Q0 — выходы (1-0 разряды); ТС — выход

переноса (выход завершения счёта); СЕО — выход разрешения счёта (СЕО = ТС∙СЕ)

|

|

|

|

|

Таблица П.16 |

|

|

|

Микрооперации счётчика СВ2СLЕ |

||

|

|

|

|

|

|

|

|

Входы |

|

Микрооперация |

|

CLR |

L |

|

CE |

C |

|

|

|

||||

1 |

X |

|

X |

X |

Асинхронный сброс в нуль |

0 |

1 |

|

X |

0/1 |

Параллельная загрузка |

0 |

0 |

|

1 |

0/1 |

Счёт |

0 |

0 |

|

0 |

X |

Хранение |

Рис. П.40. Внутренняя структура счётчика СВ2СLЕ

229

Двоичный реверсивный счётчик с параллельной загрузкой, асинхронным сбросом и входом разрешения счёта

(СВ2СLЕD, СВ4СLЕD, СВ8СLЕD, СВ16СLЕD)

Условное графическое обозначение двухразрядного двоичного счётчика СВ2СLЕD показано на рис. П.41. Микрооперации, выполняемые счётчиком СВ2СLЕD, приведены в табл. П.17, а его внутренняя структура — на рис. П.42.

Рис. П.41. Условное графическое обозначение счётчика СВ2СLЕD: С — тактовый вход; СЕ — вход разрешения счёта; L — вход разрешения параллельной загрузки; UP — вход изменения направления счёта; CLR — вход сброса; D1-D0

— параллельные входы данных; Q1-Q0 — выходы (1-0 разряды); ТС — выход переноса (выход завершения счёта); СЕО — выход разрешения счёта (СЕО = ТС∙СЕ)

|

|

|

|

|

Таблица П.17 |

|

|

|

Микрооперации счётчика СВ2СLЕD |

||||

|

|

|

|

|

|

|

|

|

Входы |

|

|

Микрооперация |

|

|

|

|

|

|

||

CLR |

L |

CE |

C |

UP |

||

|

||||||

|

|

|

|

|

|

|

1 |

X |

X |

X |

X |

Асинхронный сброс в нуль |

|

|

|

|

|

|

|

|

0 |

1 |

X |

0/1 |

X |

Параллельная загрузка |

|

|

|

|

|

|

|

|

0 |

0 |

1 |

0/1 |

1 |

Счёт на увеличение |

|

|

|

|

|

|

|

|

0 |

0 |

1 |

0/1 |

0 |

Счёт на уменьшение |

|

|

|

|

|

|

|

|

0 |

0 |

0 |

X |

X |

Хранение |

|

|

|

|

|

|

|

|

230