- •Министерство образования республики беларусь

- •Министерство образования республики беларусь

- •Реферат

- •Рэферат

- •Abstract

- •Введение

- •1. Обзор литературных источников

- •1.1 Описание основных программ

- •1.2 Описание схемы

- •1.3 Обзор компонентов

- •1.4 Виртуальные приборы

- •2. Разработка лабораторного комплекса по созданию сенсорного интерфейса на основе графической платформы cicrcuit design suite

- •2.1 Выбор платформы для моделирования

- •2.2 Микропроцессор

- •2.3 Разработка электрической схемы

- •2.4 Создание схемы в программеMultisim

- •3. Бизнес-планировние и менеджмент дипломного проекта

- •3.1 Оценка конкурентоспособности объекта проектирования

- •3.2 Определение единовременных затрат на создание программного продукта (разработку модели)

- •3.2.1 Определение трудоемкости разработки алгоритма пп

- •3.2.3 Определение оптовой и отпускной цены пп

- •3.2.4 Определение ожидаемого прироста прибыли в результате внедрения программного продукта

- •3.2.5 Определение годовых текущих затрат, связанных с эксплуатацией задачи

- •3.2.6 Определение ожидаемого прироста прибыли в результате внедрения пп

- •3.2.7 Расчет показателей эффективности использования программного продукта

- •4. Охрана труда

- •4.1 Производственная санитария и техника безопасности

- •4.1.1 Вредные факторы

- •4.1.1.1 Шум

- •4.1.1.2 Вибрация

- •4.1.1.3 Излучение

- •4.2 Метеорологические условия

- •4.3 Вентиляция и кондиционирование

- •4.5 Организация рабочего места

- •4.6 Освещение

- •4.6.1 Определение освещения, расчет освещения.

- •4.7 Пожарная безопасность

- •Заключение

- •Список использованных источников

2.2 Микропроцессор

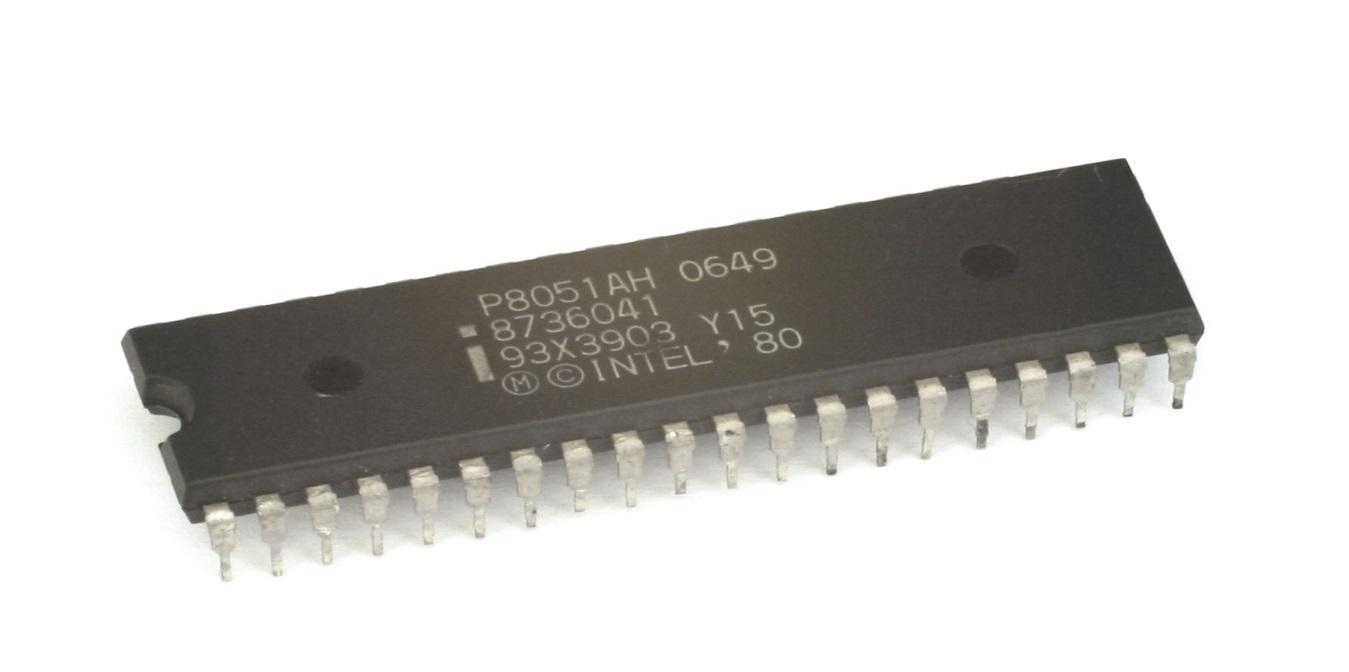

В качестве микропроцессора, который будет использован в разработке, был выбран Intel8051 (рисунок 2.1).

Выбор этого микропроцессора был обусловлен тем, что база микропроцессоров программы Multisimсодержит всего 4 микропроцессора. Такие какIntel8051,Intel8052,PIC16F84 иPIC16F84A.

Рисунок 2.1 – Микропроцессор Intel8051.

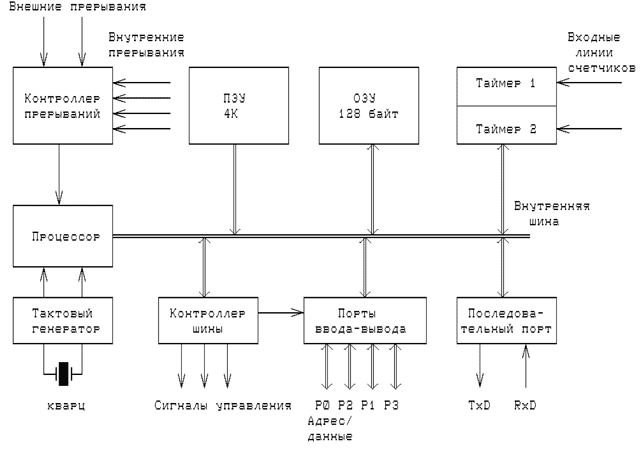

Общей особенностью в современных 8051-совместимых микроконтроллерах стало встраивание улучшенных и дополнительных схем, таких как: автоматический сброс по падению питающего напряжения; встроенные тактовые генераторы; внутрисхемное программирование памяти программ; автозагрузчики долговременной памяти данных на основе EEPROM;I²C;SPI(стандарт 3-проводной последовательной шины);USBхост-интерфейс; ШИМ-генераторы; аналоговых компараторов; АЦП и ЦАП преобразователей; часов реального времени; дополнительных таймеров и счетчиков; внутрисхемных отладчиков, дополнительных источников прерываний; расширенных энергосберегающих режимов.

8051-совместимые микроконтроллеры обычно имеют один или два УАПП (UART), два или три таймера, 128 или 256 байт встроенной ОЗУ (16 байт которой имеют побитовую адресацию), от 512 байт до 128 Кбайт встроенной памяти программ (ПЗУ), и иногда встречается использованиеEEPROM, адресуемой через «регистры специального назначения» (SFR=specialfunctionregister). УАПП/UARTможет быть настроен для использования в режиме 9-бит данных, что делает возможным адресную приёмопередачу в многоточечном подключении на основеRS-485 аппаратного протокола.

Один

машинный цикл оригинального 8051-ядра

занимает 12 временных тактов, а большинство

инструкций выполняется за один или два

машинных цикла. При частоте тактового

генератора, равной 12 МГц, 8051-ядро может

выполнять 1 миллион операций в секунду,

выполняемых за один цикл, или 500 тысяч

операций в секунду, выполняемых за два

цикла. Улучшенное 8051-совместимое ядро,

которое в настоящее время распространено,

выполняет машинный цикл за шесть, четыре,

два, или даже за один временной такт, и

позволяет использовать тактовые

генераторы с частотой до 100 МГц, что

позволило увеличить количество

выполняемых операций в секунду.

Рисунок 2.2 - Обобщенная структурная схема контроллера Intel 8051.

Еще более быстрые 8051-ядра, с 1 тактом на машинный цикл, организуются с использованием ПЛИС, таких как FPGA(скорость в диапазоне 130 - 150 МГц) илиASIC(скорость в диапазоне нескольких сотен МГц), при помощи специальной прошивки. Все 8051-совместимые устройства, производимыеSILabs, некоторые из производимыхDallasи немногие из производимыхAtmelимеют ядро с 1 тактом на машинный цикл.

Чрезвычайно полезной особенностью 8051-ядра является обработка булевых данных, что позволило ввести бинарную логику, оперирующую напрямую с битами внутренней ОЗУ (области из 128 прямо-адресуемых битов) и регистров. Данная особенность была востребована в приложениях промышленной автоматики. Еще одна ценная особенность состояла в 4 независимых наборах регистров, которые значительно уменьшали задержки при обработке прерываний, в сравнении с классическим использованием стека, применявшимся ранее.